Цель работы: Изучение способов упрощения логических функций, в том числе частично определенных (недоопределенных) функций. Приобретение практических навыков по разработке и расчету схем на базе логических элементов, в том числе на основе базовых логических элементов.

2.2. Контрольные вопросы

1. Объясните принцип построения карты Карно.

На практике для упрощения логических выражений, описывающих работу устройства, применяют карты Карно. Карта Карно представляет собой графическое изображение всех возможных наборов значений аргументов, каждый минтерм изображается на карте в виде клетки. Карта образуется путем такого расположения клеток, при котором минтермы, находящиеся в соседних клетках, отличаются значением одной переменной.

Карта Карно для 2-х переменных имеет вид, представленный на рисунке 3.1.а.

| а) | б) | в) |

| Рис. 3.1 – Упрощение логического выражения с помощью карты Карно |

Минимизируем исходное логическое выражение посредством применения карты Карно. Поставим 1 в карте Карно в тех клетках, которые соответствуют наборам функции, присутствующим в логическом выражении, рисунок 3.1.б.

Отыскание минимальной формы сводится к максимальному склеиванию по некоторому аргументу: по В – вертикаль и по А – горизонталь. Единицы, находящиеся в соседних клетках, объединим контурами (рисунок 3.1.в). Возможно объединение 2, 4, 8 и т.д. единиц, стоящих в соседних клетках. Кроме этого, карта Карно может быть свернута в горизонтальный или вертикальный цилиндры, или шар, что также позволяет объединить единицы, стоящие в соседних крайних клетках свернутых карт.

Нижний контур, даст аргумент А. Верхний контур – аргумент В

В результате значение функции будет также сведено к логической операции ИЛИ: F = А+В.

2. Объясните особенность минимизации недоопределенных булевых функций.

Частично определенной (недоопределенной) функцией называется функция, значение которой на некоторых наборах запрещено или некоторые наборы входных значений не используются в работе схемы. Значение функции на таких наборах можно задать по своему усмотрению (1 или 0), т.е. доопределить функцию.

Доопределение функции не отразится на работе устройства, но облегчит егореализацию.

При минимизации недоопределенных булевых функций в клетках карты Карно, которые соответствуют запрещенным наборам, ставят прочерки, которые могут доопределяться 1 или 0 для удобства конкретной минимизации.

Пример минимизации недоопределенной функции показан на рисунке 3.2.

| ||||||||||||||||||||||||||||||||||||||

| а) таблица истинности | б) карта Карно | в) доопределение карты Карно | ||||||||||||||||||||||||||||||||||||

| Рисунок 3.2– Минимизация недоопределенной функции |

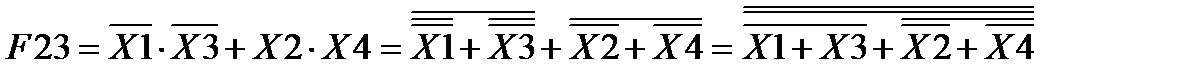

В результате будет получено логическое выражение

3. Поставьте значения после знака равенства: Х*1 = X; Х*0 = 0

4. Поставьте значения после знака равенства: Х+1 = 1; Х+0 = X

5. Какие входы ИС называются «лишними»? Решите проблему лишних входов для элемента И на 4 входа, относящегося к семейству ТТЛ(Ш), если задействованы будут только 2. Приведите схему решения.

При реализации функциональной логической схемы на наборе стандартных ИС возможны несовпадения состава элементов, имеющихся для реализации схемы, с составом элементов, необходимых согласно синтезу.

Существует несколько типовых ситуаций:

1. наличие у имеющихся элементов «лишних» (неиспользуемых в данном случае) входов;

2. наличие в корпусах ИС лишних элементов;

3. отсутствие у имеющихся элементов необходимого числа входов.

Рисунок 3.2 – Решение проблемы лишних входов для элемента И на 4 входа, относящегося к семейству ТТЛ(Ш).

6. Решите вопрос «лишнего» элемента в корпусах ИС, представленных на рисунке 2.1, если в корпусе НЕ «лишние» элементы имеют выходы 2 и 4; 2ИЛИ-НЕ –10 и 13; 3И-НЕ – 6; 9И1НЕ – 12. Приведите схемы решений.

Для ТТЛ(Ш)-элементов строгого запрета на оставление разомкнутых входов нет, но так делать не рекомендуется, поскольку пострадают параметры быстродействия элемента.

Таким образом, для КМОП и ТТЛ(Ш) режим неиспользуемых входов заключается в подаче на них констант (логических единиц или нулей), не изменяющих работу схемы для задействованных входов.

| а) НЕ | б) 2ИЛИ-НЕ | в) 3И-НЕ | г) 9И, 1НЕ | |

| Рис. 3.3 – Цифровые интегральные схемы | ||||

7. Осуществите наращивание числа входов ЛЭ: для 5 входных переменных, используя только корпуса ИС, представленной на рисунке 3.3.б, и для 7 входных переменных, используя только корпуса ИС, представленной на рисунке 3.3.в. Нарисуйте принципиальные схемы решений.

Для наращивание числа входов ЛЭ для 5 входных переменных, преобразуем функцию  в базис 2ИЛИ-НЕ.

в базис 2ИЛИ-НЕ.

На основании этого выражения осуществим наращивание числа входов для операций 5ИЛИ-НЕ(рис. 3.4)

Рис. 3.4 – Наращивание числа входов ЛЭ для операций 5ИЛИ-НЕ.

Для наращивание числа входов ЛЭ для 7 входных переменных, преобразуем функцию  в базис 3И-НЕ.

в базис 3И-НЕ.

На основании этого выражения осуществим наращивание числа входов для операций 7И-НЕ(рис. 3.5)

Рис. 3.5 – Наращивание числа входов ЛЭ для операций 7И-НЕ.

Индивидуальные задания

1. В соответствии с вариантом, указанным преподавателем, осуществить упрощение логической функции, заданной таблицей истинности 2.1, представив в отчете таблицу истинности в стандартной форме. Упрощение провести по 0 и 1.

Определить и записать, в каком случае и почему результирующее логическое выражение окажется проще.

Таблица 3.1

| Входные сигналы | Функция F | |||

| Х1 | Х2 | Х3 | Х4 | F23 |

| - | ||||

| - | ||||

| - | ||||

| - | ||||

| - | ||||

| - | ||||

| - | ||||

При минимизации недоопределенных булевых функций в клетках карты Карно, которые соответствуют запрещенным наборам, ставят прочерки, которые могут доопределяться 1 или 0 для удобства конкретной минимизации.

Перерисуем таблицу истинности в 2-х мерный вид, заполним её значениями из таблицы истинности и минимизируем по 1 в соответствии с правилами:

Таблица 3.2

| X3X4 X1X2 | ||||

| -1 | ||||

| -1 | -1 | -0 | ||

| -1 | -0 | |||

| -0 |

Минимизируем по 0 в соответствии с правилами.

Таблица 3.3

| X3X4 X1X2 | ||||

| -1 | ||||

| -1 | -0 | -0 | ||

| -0 | -0 | |||

| -0 |

Логическое выражение минимизируемое по 1 оказалось проще.

2. Нарисовать принципиальную схему, реализующую упрощенную логическую функцию, рационально используя корпуса ИС, представленные на рисунке 2.1, и руководствуясь требованиями ЕСКД.

К155ЛН1 К155ЛЕ1 К155ЛА4 К176ЛИ1

| а) НЕ | б) 2ИЛИ-НЕ | в) 3И-НЕ | г) 9И, 1НЕ | ||||||||||||||||||||||||||||||||||||

Рис. 3.6 – Цифровые интегральные схемы

Таблица 3.4-Справочные данныемикросхем серии 155

| |||||||||||||||||||||||||||||||||||||||

Для реализации функции

Рис. 3.7 – Принципиальная схема реализующая минимизированную функцию F23.

3. Осуществить проверку схемы. Для этого взять любую комбинацию входных данных из таблицы истинности и проверить, соответствует ли значение, полученное на выходе схемы, значению функции F, заданному для этой комбинации в таблице. Процедуру проверки представить в отчете.

Проверим комбинацию

Таблица3.5

Рис. 3.7 – Принципиальная схема функцию F23, процедура проверки. | |||||||||||||||||||||||||||||||||||||||

Средняя задержка распространения сигнала одного ЛЭ будет равна:

τзд р срЛЭ = (t10зд р + t01зд р)/2 = (15+22)*10-9 /2 = 18.5 нс.

τзд р ср общ. = τзд р срDD1.1+ τзд р срDD2.1+ τзд р срDD2.3+ τзд р срDD1.3= 4*18.5*10-9 =74 нс.

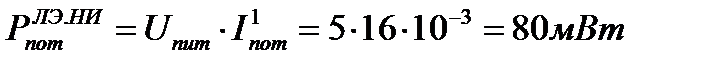

Cредняя потребляемая мощность ЛЭ рассчитывается по формуле:

Токи потребления микросхемы К155ЛН1 в состоянии логического «0»  и «1»

и «1»

Cредняя потребляемая мощность используемого ЛЭ микросхемы К155ЛН1:

Cредняя потребляемая мощность не используемого ЛЭ микросхемы К155ЛН1:

Токи потребления микросхемы K155ЛE1 в состоянии логического «0»  и «1»

и «1»

Cредняя потребляемую мощность ЛЭ рассчитывается по формуле:

Мощность, потребляемая используемые схемой от источника питания:

Мощность, потребляемая cхемой от источника питания:

Л а б о р а т о р н а я р а б о т а №4