РАССЧЕТ ОСНОВНЫХ ПАРАМЕТРОВ СВЁРТОЧНОГО КОДА

Исходные данные:

1. Количество единиц в информационной подматрице проверочного треугольника 4;

2. Скорость входного потока R=3/4;

3. Тип помехоустойчивого кода ССК.

4. Алгоритм декодирования пороговый.

5. Тип канала связи ДСК без памяти

6. Среднее время восстановления работоспособности кодека 20 мин.

7. Время работы кодека 12 час.

8. Способ реализации проектируемого кодека аппаратурный.

Примечание. Выходной сигнал на выходе демодулятора квантуется на Q=2 уровня (жесткое решение).

Расчёт основных параметров СК

Определим параметры свёрточного кода:

1. Эти параметры можно определить исходя из скорости передачи кода, т.к.:

(1)

(1)

R=1-r (2)

где r – относительная избыточность свёрточного кода;

r= (1 - ¾) ∙100= 25%

2. Исходя из представленных выше данных количество информационных символов ko=3, а количество кодовых символов no=4;

3. Т.к. значение ko определяет количество порождающих полиномов, то при наших условиях их три;

4. По количеству единиц в информационной подматрице проверочного треугольника можно судить о числе проверочных уравнений для данного кода. В нашем случае J=4, следовательно, ССК может исправлять tисп≤J/2=4/2=2 ошибки, обнаруживать tобн≥ d0-1 = (J+1) - 1 = 4 ошибки;

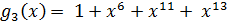

5. По значению k0 и J можно определить номер варианта, в нашем случае даны три полинома, в каждом из которых по четыре члена. Значит, необходимо выбрать 10 вариант, для которого:

a) Отношение сигнал/шум Pc/Pш = 8 дБ;

b) Вероятность допустимой ошибки декодирования Рош.доп=10-8;

c) Скорость передачи входного информационного потока  I(D) = 1,544 Мбит/с;

I(D) = 1,544 Мбит/с;

d) Тип модуляции — ОФМ;

e) Способ обработки модулированных сигналов — когерентный;

f)  ,

,  ,

,  ;

;

6. Выходная скорость передачи информации.

=

=  ; (2.2)

; (2.2)

=

=  = 2,059 Мбит/с;

= 2,059 Мбит/с;

7. Рассчитаем новое значение отношения сигнал/шум.

=

=  –Δ; (2.3)

–Δ; (2.3)

Δ=  *процент из интервала (12, 1),исходя из значения R=

*процент из интервала (12, 1),исходя из значения R=  ; (

; ( )

)

Рисунок 2.1 - Распределение значения процента в зависимости от значения отношения  .

.

Исходя из зависимости процент, на который уменьшится отношение сигнал/шум  6%.

6%.

Δ=  ∙0,06;

∙0,06;

=8дБ-8дБ∙0,06=7,52дБ

=8дБ-8дБ∙0,06=7,52дБ

8. Нахождение вероятности ошибки  .

.

Исходя из полученного нового отношения сигнал/шум, определим  по графику зависимости

по графику зависимости  от

от  при когерентном способе обработки информации и при типе модуляции ОФМ (Рисунок2.2).

при когерентном способе обработки информации и при типе модуляции ОФМ (Рисунок2.2).

Рисунок 2.2 – Вероятность ошибочного приёма двоичного символа в ДСК при когерентном способе обработки информации при типе модуляции ОФМ.

По графику видно, что

7*10-5

7*10-5

Вероятность первой ошибки декодирования  .

.

≤

≤  (2.4)

(2.4)

≤

≤  (2.5)

(2.5)

=5.65 × 10-11 ≤

=5.65 × 10-11 ≤

9. Длина кодового ограничения свёрточного кода:

=(m+1)∙

=(m+1)∙  ; (2.6)

; (2.6)

где m – максимальная степень порождающего полинома.

=(19+1)∙4

=(19+1)∙4  дв.симв.;

дв.симв.;

10. Эффективная длина

=

=  +

+  + 1; (2.7)

+ 1; (2.7)

=8+2+1=11;

=8+2+1=11;

3 РАЗРАБОТКА СТРУКТУРНОЙ СХЕМЫКОДЕКА

3.1 Разработка структурной схемы кодера

Разработку структурной схемы кодера ССК следует выполнять с определения основных функций кодера, к которым следует отнести:

- деление входного потока на k0 информационных подпотоков;

- определение проверочных символов;

- объединение проверочных и контрольных символов.

Исходя из этого он должен содержать в себе следующие блоки:

1. КРИ(1/ k0) – коммутатор распределения информации I(х) на k0 информационных подпотоков;

2. ФПС – формирователь проверочных символов;

3. КОИ – коммутатор объединения n0 информационных потоков в один поток;

Для кода со скоростью 3/4 блоки КРИ и КОИ должны иметь следующие параметры:

- КРИ(1/3)

- КОИ(4/1)

Исходя из вышеуказанного, построим структурную схему кодера (Рисунок 3.1).

Рисунок 3.1 – Структурная схема кодера ССК.

Кодер ССК работает следующим образом.

Символы входного информационного потока I(x) разделяются в КРИ(1/3) на три подпотока – I1(x)…I3(x). Информационные символы данных подпотоков поступают одновременно на соответствующие входы КОИ(4/1) и ФПСк. В ФПС из символов информационных подпотоков формируются проверочные (контрольные) символы Рпер(x). Сформированные проверочные символы поступают на соответствующий вход КОИ(4/1), который объединяет символы информационных подпотоков I1(x)…I3(x) и символы проверочного подпотока в единый поток кодовых символов T(x), поступающих далее на вход устройства преобразования сигналов (УПС) или модема ДКС.

3.2 Разработка структурной схемы декодера

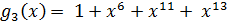

Для полученных в расчетах полиномов построим проверочные треугольники и определим по ним синдромы ошибок.

По этой матрице составим систему синдромов:

По этой матрице составим систему синдромов:

По этой матрице составим систему синдромов:

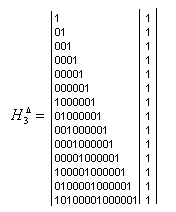

Разработка структурной электрической схемы декодера ССК с алгоритмом порогового декодирования производится по методике, аналогичной разработке структурной электрической схемы кодера ССК.

Декодер должен выполнять следующие функции:

1. Разделять принятый поток на n0 подпотоков – блок КРИ ¼;

2. Формировать проверочные символы из принятых информационных I’(x) – блок ФПСд;

3. Формировать синдромные последовательности S – блок ФСП;

4. Анализировать синдромные последовательности – блок АСП с пороговыми элементами;

5. Корректировать ошибки – блок КО, включающий в себя регистры сдвига (РС) и сумматоры по модулю два;

6. Объединять скорректированные подпотоки в один информационный поток I(x) – блок КОИ 3/1

Построим структурную электрическую схему декодера ССК с алгоритмом порогового декодирования:

Рисунок 3.2 - Структурная электрическая схема декодера ССК с алгоритмом порогового декодирования

На вход КРИ 1/4 поступает принимаемый поток Т’(x). Далее он разделяется на 4 подпотока: 3 информационных и один проверочный. Информационные подпотоки поступают на Корректор Ошибок (КО) и на ФПСд. С ФПСд сформированный сигнал Рсф, и сигнал Р’пер , принятый с КРИ, поступают на формирователь синдромной последовательности (ФСП). В ФСП формируются символы синдромных последовательностей, после чего эти символы поступают на анализатор синдромной последовательности, на выходах которого формируются корректирующие символы информационной последовательности. В корректоре ошибок (КО) символы сравниваются и, если требуется, корректируются. С КО исправленные символы поступают в КОИ 3/1 и на выходе мы получаем декодированную информационную последовательность I(x).

4 РАЗРАБОТКА ФУНКЦИОНАЛЬНОЙ СХЕМЫКОДЕКА

4.1 Разработка функциональной схемы кодера

В схему кодера входят такие функциональные блоки, как:

- КРИ 1/3;

- ФПСк;

- КОИ 4/1;

Наиболее простым способом построения КРИ 1/3 является использование двух регистров RG (последовательного RG1 и параллельного RG2) и блока формирования тактовых частот RG1 и RG2, представляющих собой схему управления, построенную на кольцевом счётчике CT и дизъюнкторе. Последовательный и параллельный регистры RG содержат по k0 ячеек памяти, т.е. в нашем случае по три ячейки памяти. Регистры представляют собой совокупность k0 D-триггеров, т.е. нам необходимо k0=3 D-триггера. Функциональная электрическая схема КРИ – 1/3 представлена на рисунке 4.2.

Рисунок 4.2 - Функциональная электрическая схема КРИ 1/3 кодера

Для описания принципа работы КРИ будем использовать временные диаграммы, построенные для контрольных точек (рисунок 4.3).

Отметим, что при построении временных диаграмм, необходимо учесть то, что счётчик работает по отрицательному фронту (по спаду), а данные считываются по переднему фронту тактовой последовательности.

Рисунок 4.3 – Временные диаграммы работы КРИ 1/3

Функциональная электрическая схема ФПСк выполняется в виде схем умножения полиномов и реализуется в виде регистра сдвига RG либо со встроенными сумматорами по модулю два.

Для полиномов g(x)=1+x3+x15+x19, g(x)=1+x8+x17+x18, g=1+x6+x11+x13 построим ФПСк:

Так как максимальная степень порождающих полиномов m=19, RG будет содержать 19 сумматоров по модулю два.

Так как максимальная степень порождающих полиномов m=19, RG будет содержать 19 сумматоров по модулю два.

Рисунок 4.4 – Схема функциональная электрическая ФПСк

Нумерация ячеек памяти ФПСк ведётся справа налево. Места включения сумматоров по модулю два определяются ненулевыми членами порождающих полиномов; выходной сумматор по модулю два является многовходовым (3 входа).

КОИ – 4/1 кодера ССК выполняется в виде синхронного мультиплексора на соответствующее число информационных и управляющих входов, а также формирователя сигналов управления мультиплексором, представляющего собой двоичный счётчик.

Функциональная электрическая схема КОИ – 4/1 представлена на рисунке 4.5, а временные диаграммы, поясняющие его принцип работы, приведены на рисунке 4.6.

4.2 Разработка функциональной схемы декодера

В схему декодера входят такие функциональные блоки, как:

- КРИ 1/4;

- ФПСд;

- ФСП;

- АСП;

- КО;

- КОИ 3/1;

Способ построения КРИ-1/4 является аналогичным способу построения КРИ-1/3, различие заключается лишь в количестве D триггеров у регистров RG1 и RG2, а также в схеме управления. Необходимо отметить то, что сброс будет происходить по спаду каждого 4-ого такта, т.к. на выходе RG1 у нас 4 подпотока.

Способ построения КОИ-3/1 является также аналогичным способу построения КОИ-4/1, различие заключается лишь в количестве входов мультиплексора, в схеме управления, а так же в том, что сброс в нём будет происходить по спаду каждого 3-ого такта, т.к. у MUX будут задействованы 3 входа.

Для декодера ФПС будет таким же, как и для кодера.

Корректор ошибок (КО) декодера выполняется в виде трех регистров сдвига, каждый из которых содержит по 19 ячеек памяти. На выходе каждого регистра включается сумматор по модулю два, на второй вход которого поступает сигнал коррекции с выхода порогового элемента (ПЭ) анализатора синдромной последовательности (АСП) декодера.

Построим КО:

Рисунок 4.7 – Схема функциональная электрическая КО

Информационные символы с выходов КО поступают на соответствующие входы КОИ декодера.

Формирователь синдромной последовательности ФСП представляет собой сумматор по модулю два, на входы которого поступают Р`пер и Pсф, а на выходе формируется синдром S(x). Выход сумматора подключается к АСП.