Быстродействующие широкополосные операционные усилители (К154УД2) используются для преобразования быстроизменяющихся сигналов. Они характеризуются высокой скоростью нарастания выходного сигнала, малым временем установления, высокой частотой единичного усиления, а по остальным параметрам уступают операционным усилителям общего применения. К сожалению, для них не нормируется время восстановления после перегрузки, Их основные параметры: скорость нарастания VUвых max >> 30 В/мкс; время установления tуст ≤ 1 мкс; частота единичного усиления f1 ≥ 10 МГц.

Прецизионные (высокояочные) операционные усилители (К140УД24) используются для усиления малых электрических сигналов, сопровождаемых высоким уровнем помех, и характеризуются малым значением напряжения смещения и его температурным дрейфом, большими коэффициентами усиления и подавления синфазного сигнала, большим входным сопротивлением и низким уровнем шумов. Как правило, имеют невысокое быстродействие. Их основные параметры: напряжение смещения Uсм ≤ 250 мкВ; температурный дрейф ΔUсм / ΔT ≤ 5 мкВ/°С; коэффициент усиления KU0 ≥ 150 тыс.

Операционные усилители общего применения (К140УД7) используются для построения узлов аппаратуры, имеющих суммарную приведенную погрешность на уровне 1%. Характеризуются относительно малой стоимостью и средним уровнем параметров (напряжение смещения Uсм — единицы милливольт, температурный дрейф ΔUсм / ΔT — десятки микровольт/°С, коэффициент усиления КU0 — десятки тысяч, скорость нарастания VUвых max — от десятых долей до единиц вольт/микросекунд).

Операционные усилители с малым входным током — усилители с входным каскадом, построенным на полевых транзисторах. Входной ток Iвх ≤ 100 пА.

Многоканальные операционные усилители имеют параметры, аналогичные усилителям общего применения или микромощным усилителям с добавлением такого параметра, как коэффициент разделения каналов. Они служат для улучшения массогабаритных показателей и снижения энергопотребления аппаратуры. Западные фирмы выпускают сдвоенные прецизионные и быстродействующие усилители.

Мощные и высоковольтные операционные усилители — усилители с выходными каскадами, построенными на мощных высоковольтных элементах. Выходной ток Iвых ≥ 100 мА; выходное напряжение Uвых ≥ 15 В.

48Микромощные операционные усилители (К1423УД1) необходимы в случаях, когда потребляемая мощность жестко лимитирована (переносные приборы савтономным питанием, приборы, работающие в ждущем режиме). Ток потребления Iпот max ≤ 1 мА.

Компараторы

Компараторы – особый класс электронных схем, основная функция которых - сравнение входного сигнала с эталонным. В них состояние выходного сигнала изменяется при превышении входным сигналом порогового значения (рис. 6.14). Компараторы могут выполняться на базе различных элементов, в том числе и на операционных усилителях. При этом усиление входного сигнала значительно лишь вблизи порога, в основном работа ОУ происходит в области ограничения выходного напряжения (отрицательной или положительной).

Компараторы – особый класс электронных схем, основная функция которых - сравнение входного сигнала с эталонным. В них состояние выходного сигнала изменяется при превышении входным сигналом порогового значения (рис. 6.14). Компараторы могут выполняться на базе различных элементов, в том числе и на операционных усилителях. При этом усиление входного сигнала значительно лишь вблизи порога, в основном работа ОУ происходит в области ограничения выходного напряжения (отрицательной или положительной).

На рисунке представлен компаратор LM311:

Рисунок 6.14 Принцип работы компаратора.

Основной характеристикой компаратора является зависимость “вход-выход” (зависимость выходного напряжения от входного), представленная на рис. 6.15

Основной характеристикой компаратора является зависимость “вход-выход” (зависимость выходного напряжения от входного), представленная на рис. 6.15

Рис. 6.15. Зависимость “вход-выход” для компаратора.

Схема простейшего компаратора детектора нулевого уровня (пороговое напряжение достаточно близко к нулю) представлена на рисунке 6.16

|

Рис. 6.16. Схема включения компаратора.

Электронный генератор — электронное устройство, вырабатывающее электрические колебания определенной частоты и формы, используя энергию источника постоянного напряжения (тока). Различают генераторы с самовозбуждением (автогенераторы) и генераторы с внешним возбуждением. Любой автогенератор содержит колебательную систему и усилительный элемент (на биполярном или полевом транзисторе), связанные положительной обратной связью. Основными характеристиками генератора являются форма, частота и мощность колебаний. По форме различают электронные генераторы гармонических (почти синусоидальных) колебаний и так называемые релаксационные генераторы различной формы.

Модель компаратора в среде Multisim представлена на рис. 6. 17, показания осциллографа на рис. 6.18.

Рис. 6.17. Компаратор в среде Multisim

Рис. 6.18. Показания осциллографа на входе/выходе компаратора

Стабилизатор напряжения

Стабилизатором напряжения называют преобразователь электрической энергии, позволяющий получить на входе напряжение, находящееся в заданных больших колебаниях входного напряжения и сопротивления нагрузки. По типу выходного напряжения стабилизаторы делятся на стабилизаторы постоянного тока и переменного тока. Как правило, тип питания такой же, как и выходное напряжение, хотя возможны и исключения.

Рассмотрим стабилизатор постоянного тока – линейный стабилизатор (рис. 6.19). Он представляет собой делитель напряжения, на вход которого подаётся входное (нестабильное) напряжение, а выходное (стабилизированное) напряжение снимается с нижнего плеча делителя. Стабилизация осуществляется путём изменения сопротивления одного из плеч делителя: сопротивление постоянно поддерживается таким, чтобы напряжение на выходе стабилизатора находилось в установленных пределах. При большом отношении величин входного/выходного напряжений линейный стабилизатор имеет низкий КПД, так как большая часть мощности Pрасс = (Uin - Uout) * It рассеивается в виде тепла на регулирующем элементе. Поэтому регулирующий элемент должен иметь возможность рассеивать достаточную мощность, т. е. должен быть установлен на радиатор нужной площади. Преимущество линейного стабилизатора — простота, отсутствие помех и небольшое количество используемых деталей.

Рис. 6.19. Микросхема линейного стабилизатора КР1170ЕН8

В зависимости от расположения элемента с изменяемым сопротивлением линейные стабилизаторы делятся на два типа:

· Последовательный: регулирующий элемент включен последовательно с нагрузкой.

· Параллельный: регулирующий элемент включен параллельно нагрузке.

В зависимости от способа стабилизации:

· Параметрический: в таком стабилизаторе используется участок ВАХ прибора, имеющий большую крутизну.

· Компенсационный: имеет обратную связь. В нём напряжение на выходе стабилизатора сравнивается с эталонным, из разницы между ними формируется управляющий сигнал для регулирующего элемента.

На рис. 6. 20 представлены модели: а) параллельного параметрического стабилизатора на стабилитроне; б) последовательного компенсационного стабилизатора на ОУ.

Рис. 6. 20. а) Модель параллельного параметрического стабилизатора на стабилитроне

Рис. 6. 20. б) Модель последовательного компенсационного стабилизатора на ОУ

Рис. 6. 20. б) Модель последовательного компенсационного стабилизатора на ОУ

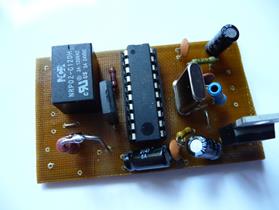

Стабилизатор можно построить и с помощью интегральной схемы (показан на рисунке), например, LM7812CT – линейного регулятора напряжения. Модель изображена на рис. 6. 21.

Рис. 6.21. Модель стабилизатора на интегральной микросхеме

Цифровые устройства

Цифровыми называют устройства, предназначенные для формирования, преобразования и передачи кодовых слов. При этом кодовые слова (коды или числа) в электронных цифровых устройствах представляются в виде последовательностей электрических импульсов (сигналов с двумя уровнями напряжения: высоким и низким), а их преобразования осуществляются арифметическими, логическими, запоминающими и вспомогательными устройствами.

Элементами и узлами цифровых устройств, служащими основой для построения микропроцессоров, микропроцессорных систем, компьютеров, автоматизированных систем управления объектами, технологическими процессами и информационными потоками являются: дешифраторы, сумматоры, триггеры, регистры, счетчики и многие другие.

Базовые элементарные единицы цифровых схем, такие как элементы «И», «ИЛИ», «НЕ», находятся в разделе Misc Digital, подраздел TIL.

Рассмотрим каждый из них в отдельности:

| Элемент «AND» - «И» |

| Элемент «OR» - «ИЛИ» |

| Элемент «NOT» - «НЕ» |

| Элемент «NOR» - «ИЛИ-НЕ» |

| Элемент «XNOR» - «НЕ-ЛИБО» |

На основе базовых элементов создадим схему цифрового устройства для принятия решения по условию. Блок-схема такого устройства представлена на рис. 6.22. Условие будет задано логическим выражением:

Рис. 6.22. Блок-схема цифрового устройства

Модель, полученная в Multisim, отображена на рис. 6. 23. На выходах будет наблюдаться сигнал высокого уровня (5В), когда конфигурация входов будет удовлетворять заданному условию.

Рис. 6.23. Модель устройства в Multisim

Теперь рассмотрим схему и механизм работы часто используемого устройства – мультиплексора – переключателя каналов. Структурная схема отображена на рис. 6.21. На схеме есть два базовых элемента - переключатель и выключатель. Переключатель выполнен в виде ключа с сигналами x1 и x2, именно он определяет, какой из четырех каналов подключен к выходу в данный момент. В положении ключа 00 (код адреса х1 = 0, х2 = 0) у = а; в положении 01 (х1 = 0, х2 = 1) у = b; в положении 10 (х1 = 1, х2 = 0) у = c; в положении 11 (х1 = 1, х2 = 1) у = d. Выключатель контролирует работу устройства в целом: при Е = 1 мультиплексор работает как обычно, при Е = 0 выход узла находится в неактивном состоянии, мультиплексор заперт. Функционирование мультиплексора описывается выражением:

Рис. 6. 24. Структурная схема мультиплексора

На рис. 6.25 а, б приведены два примера реализации модели мультиплексора. В первом случае ключ состоит из двух линий, в каждой из которых по два последовательно включенных элементов «НЕ». Во втором - используется дешифратор DCD_2TO4.

Рис. 6.25 а. Модель мультиплексора

Рис. 6.25 б. Модель мультиплексора

Триггеры.

Триггерами называются устройства, обладающие двумя устойчивыми состояниями (Q = 1 и Q = 0) и способные находиться в одном из них сколь угодно долго и переходить из одного состояния в другое под воздействием внешних сигналов. В каком из этих состояний окажется триггер, зависит от сигналов на входах триггера и от его предыдущего состояния, т.е. он имеет память. Таким образом, триггер – элементарная ячейка памяти.

Тип триггера определяется алгоритмом его работы, в зависимости от которого триггер может иметь установочные, информационные и управляющие входы. Установочные входы обуславливают состояние триггера независимо от состояния других входов. Входы управления разрешают запись данных, подающихся на информационные входы. Наиболее распространенными являются триггеры RS -, JK-, D - и T -типов.

Тип триггера определяется алгоритмом его работы, в зависимости от которого триггер может иметь установочные, информационные и управляющие входы. Установочные входы обуславливают состояние триггера независимо от состояния других входов. Входы управления разрешают запись данных, подающихся на информационные входы. Наиболее распространенными являются триггеры RS -, JK-, D - и T -типов.

RS-триггер – простейший автомат с памятью, который может находиться в двух состояниях. Триггер имеет два установочных входа: установки S (set – установка) и сброса R (reset – сброс), на которые подаются входные сигналы от внешних источников. При подаче на установки активного логического уровня триггер устанавливается в единицу (Q = 1, Q ′ = 0, здесь штрих означает инвертирование), при подаче активного уровня на вход сброса триггер устанавливается в ноль (Q = 0, Q ′ = 1). Если на оба установочных входа подать пассивный логический уровень, то триггер сохраняет предыдущее состояние выходов: Q = 1 или Q = 0. Каждое состояние устойчиво и поддерживается за счет действия обратных связей. Подача активного уровня одновременно на оба установочных входа запрещена, так как триггер не может быть установлен в ноль и единицу.

RS -триггер может быть выполнен на элементах «ИЛИ-НЕ» или «И-НЕ» (рис. 6.26).

а б

Рис. 6.26. RS -триггер: а – на элементах «ИЛИ-НЕ», б – на элементах «И-НЕ»

Рис. 6.26. Моделирование RS-триггера в Multisim

Для RS -триггеров, выполненных на элементах «ИЛИ-НЕ», активным уровнем на управляющих входах является уровень логической единицы, а на элементах «И-НЕ» – уровень логического нуля.

RS -триггер – основной узел построения последовательных схем. Условия переходов триггеров из одного состояния в другое можно описать табличным, аналитическим или графическим способами. Табличное описание работы RS -триггера на элементах «ИЛИ-НЕ» и «И-НЕ» представлено в табл. 6.1 и 6.2 соответственно, где Qt – предшествующее состояние выхода; Qt +1 – новое состояние, устанавливающееся после перехода; - – неопределенное состояние.

Т а б л и ц а 6.1 Т а б л и ц а 6.2

| R | S | Qt+1 | R | S | Qt+1 | |

| Qt | – | |||||

| – | Qt |

Триггер JK-типа имеет более сложную структуру и более широкие возможности по сравнению в RS -триггером. Кроме информационных входов J и K и прямого и инверсного выходов Q и Q ′, JK -триггер имеет вход управления C (тактирующий или счетный) и два асинхронных установочных входа R и S. Обычно активными уровнями установочных сигналов являются нули. Установочные входы имеют приоритет над остальными входами. Активный уровень сигнала на входе S устанавливает триггер в состояние единица (Q = 1), а на входе R в состояние ноль (Q = 0), независимо от сигналов на остальных входах. Если на входы установки подать пассивный уровень сигнала, то состояние триггера будет изменяться по фронту импульса на счетном входе в зависимости от состояния входов J и K.

Один из вариантов функциональной схемы JK -триггера и его условное графическое изображение приведены на рис. 6.27, временные диаграммы его работы при R = S =1 – на рис. 6.28.

Рис. 6.27. JK -триггер: а – функциональная схема; б – условное

графическое обозначение

Рис. 6.28. Временная диаграмма работы JK -триггера

Рис. 6.29. Моделирование JK-триггера в Multisim

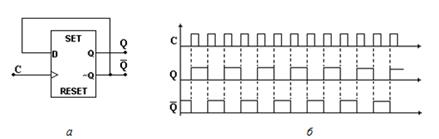

D-триггер имеет один информационный вход D (data – данные) и один счетный вход C. Информация с входа D записывается в триггер по положительному перепаду импульса на счетном входе и сохраняется до следующего положительного перепада. Кроме счетного C и информационного D входов, у триггера есть два асинхронных установочных входа R и S. Установочные входы приоритетные. Активный уровень сигнала на входе S устанавливает триггер в состояние единица (Q =1), а на входе R в состояние ноль (Q=0), независимо от сигналов на остальных входах.

D-триггер имеет один информационный вход D (data – данные) и один счетный вход C. Информация с входа D записывается в триггер по положительному перепаду импульса на счетном входе и сохраняется до следующего положительного перепада. Кроме счетного C и информационного D входов, у триггера есть два асинхронных установочных входа R и S. Установочные входы приоритетные. Активный уровень сигнала на входе S устанавливает триггер в состояние единица (Q =1), а на входе R в состояние ноль (Q=0), независимо от сигналов на остальных входах.

Условное обозначение D -триггера с диаграммами входных и выходных сигналов приведено на рис. 6.30.

Рис. 6.30. D -триггер: а – условное обозначение; б – временные диаграммы

Рис. 6.31. Моделирование D-триггера в Multisim

T-триггер, или счетный триггер, – устройство, осуществляющее счетный режим. Такие схемы можно построить на основе JK - или D -триггеров.

T-триггер, или счетный триггер, – устройство, осуществляющее счетный режим. Такие схемы можно построить на основе JK - или D -триггеров.

В D -триггере счетный режим (рис. 6.32, а) реализуется при помощи обратной связи, когда на вход D подается сигнал с инверсного выхода триггера, т.е. всегда осуществляется неравенство сигналов на входе D и на выходе Q (если Q =1, D =0 и наоборот). Следовательно, при каждом положительном перепаде сигнала на счетном входе С состояние выхода будет изменяться на противоположное.

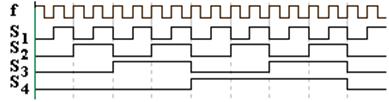

Рис. 6.32. T -триггер: а – условное обозначение; б – временная диаграмма

Таким образом, на каждые два входных тактовых импульса T -триггер формирует один период выходного сигнала Q, т.е. период выходного сигнала в два раза больше периода входного сигнала. Следовательно, триггер осуществляет деление частоты f т на его входе на две: fQ = f т/2, где fQ – частота следования импульсов на выходе триггера.

Рис. 6.33. Моделирование T-триггера в Multisim

Регистры.

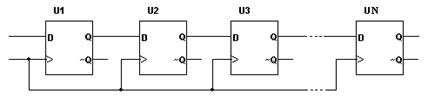

Триггерным регистром называется совокупность триггеров с определенными связями между ними, при которых они действуют как единое устройство. Регистры выполняются на синхронных триггерах JK - или D -типа. В зависимости от выполняемых функций регистры делятся на накопительные (параллельные) и сдвигающие.

Триггерным регистром называется совокупность триггеров с определенными связями между ними, при которых они действуют как единое устройство. Регистры выполняются на синхронных триггерах JK - или D -типа. В зависимости от выполняемых функций регистры делятся на накопительные (параллельные) и сдвигающие.

В последовательном регистре выход предыдущего триггера подается на вход следующего триггера, а тактовые импульсы подаются на входы С всех триггеров, составляющих регистр, одновременно (рис. 6.34). При этом содержимое каждого триггера записывается в последующий триггер. Такие регистры называются сдвиговыми регистрами, или регистрами сдвига.

Рис. 6.34. Последовательный регистр (регистр сдвига)

Рис. 6.35. Моделирование последовательного регистра в Multisim

Если на вход D регистра сдвига подать единицу, а на вход С тактовую частоту, то единица начнет продвигаться по регистру сдвига, т.е. под воздействием первого тактового импульса единица запишется в первый триггер регистра. Под воздействием второго тактового импульса эта единица перепишется во второй триггер и т.д., когда под воздействием N -го тактового импульса единица не выйдет из регистра сдвига. Временная диаграмма работы четырехразрядного регистра сдвига приведена на рис. 6.36.

Рис. 6.36. Временная диаграмма четырехразрядного регистра сдвига

Виды регистров сдвига:

· с последовательным вводом и выводом;

· с последовательным вводом и параллельным выводом;

· с параллельным вводом и последовательным выводом;

·  с переменным направлением сдвига (реверсивные регистры сдвига).

с переменным направлением сдвига (реверсивные регистры сдвига).

Кроме последовательных регистров сдвига существуют параллельные регистры, в

которых информация подается одновременно на все N триггеров и считывается одновременно с выходов всех триггеров регистра (рис. 6.37). Тактовая частота подается одновременно на все триггеры.

Рис. 6.38. Моделирование параллельного регистра в Multisim

Параллельные регистры используются для хранения двоичной информации небольшого объема в течение короткого промежутка времени.

Счетчики.

Счетчики.

Счетчиком называется устройство, подсчитывающее число входных импульсов. Число, представляемое состоянием его выходов по фронту каждого входного импульса, изменяется на единицу. Счетчик состоит из n последовательно соединенных счетных триггеров, причем выход одного счетного триггера соединен с тактовым входом следующего триггера. Счетчики бывают суммирующими (прямой счет) и вычитающими (обратный счет). В суммирующих счетчиках каждый входной импульс увеличивает число на его выходах на единицу, в вычитающих счетчиках уменьшает это число на единицу. Для того чтобы построить суммирующий счетчик, необходимо счетный вход очередного триггера подключить к инверсному выходу предыдущего (рис. 6.39).

Рис. 6.39. Суммирующий счетчик и диаграмма его работы

Рис. 6.40. Моделирование суммирующего счетчика в Multisim

Для того чтобы изменить направление счета (реализовать вычитающий счетчик), необходимо счетный вход очередного триггера подключить к прямому выходу предыдущего, при этом изменяется последовательность переключения триггеров (рис. 6.41).

Счетчик характеризуется числом состояний в течение одного периода (цикла). Для двоичных счетчиков полный цикл счета N =2 n от состояния 0..000 до состояния 1…11. Число состояний называется коэффициентом пересчета K сч, равным отношению числа импульсов Nс на входе к числу импульсов NQ ст на выходе старшего разряда за период:

.

.

Рис. 6.41. Вычитающий счетчик и диаграмма его работы

Рис. 6.42. Моделирование вычитающего счетчика в Multisim

Счетчик характеризуется числом состояний в течение одного периода (цикла). Для двоичных счетчиков полный цикл счета N =2 n от состояния 0..000 до состояния 1…11. Число состояний называется коэффициентом пересчета K сч, равным отношению числа импульсов Nс на входе к числу импульсов NQ ст на выходе старшего разряда за период:

.

.

Если на вход счетчика подавать периодическую последовательность импульсов с частотой fс, то частота fQ на выходе старшего разряда счетчика будет меньше в K сч раз: K сч= fс / fQ. Поэтому счетчики также называют делителями частоты, а K сч – коэффициентом деления. Для увеличения величины K сч нужно увеличить число триггеров в цепочке. Каждый дополнительный триггер удваивает число состояний счетчика и число K сч.

Дешифраторы.

Дешифраторы.

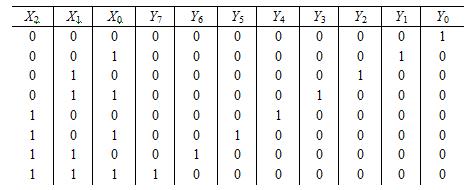

Комбинационной называется логическая схема, реализующая однозначное соответствие между значениями входных и выходных сигналов. Дешифратор – логическая комбинационная схема, имеющая n информационных входов и 2 n выходов. Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из 2 n выходов. Как любая логическая схема, дешифратор может быть задан таблицей истинности. Таблица истинности дешифратора 3х8 (табл. 6.3) состоит из трех столбцов, соответствующих входным сигналам Х 0, Х 1, Х 2, и восьми столбцов, соответствующих выходным сигналам Y 0, Y 1, Y 2, Y 3, Y 4, Y 5, Y 6, Y 7. В первых слева трех столбцах расположены возможные комбинации входных сигналов, а в последних восьми – соответствующие им комбинации выходных сигналов.

Т а б л и ц а 6.3

Схема имеет восемь выходов, на одном из которых потенциал высокий, на остальных низкий. Номер единственного выхода, имеющего высокий потенциал, соответствует двоичному числу, формируемому состояниями входных сигналов. Этот принцип формирования выходного сигнала можно описать следующим образом: Yi = 0, если i = k; Yi = 1, если i ≠ k, здесь i – номер разряда; k = 22 X 2 + 21 X 1 + 20 X 0.

Выражения для каждого выхода дешифратора:

где «¯» – инвертирование.

Таким образом, схема дешифратора должна содержать три схемы «НЕ» и восемь схем «3И» (рис. 6.43).

Рис. 6.43. Схема дешифратора 3х8

Рис. 6.44. Моделирование дешифратора 3х8 в Multisim

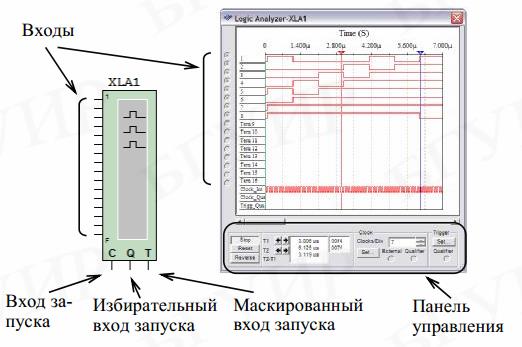

Цифровой анализатор

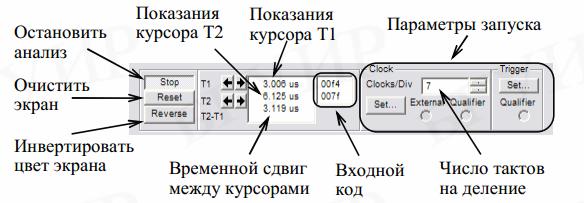

Цифровой (логический) анализатор – устройство, предназначенное для диагностики цифровых схем. ЛА позволяет отслеживать и записывать состояния логических элементов цифровых электронных устройств, анализировать и визуализировать их. Внешний вид и лицевая панель ЛА показаны на рис. 6. 45.

Рис. 6.45. Логический анализатор

ЛА имеет 16 каналов для съема сигналов, а также несколько входов запуска. Кроме этого прибор снабжен двумя курсорами, позволяющими проводить измерения во временной области. Если вход 1 считать младшим разрядом, а вход 16 страшим, то состояние всех входов может быть представлено 16-разрядным двоичным кодом. Код, соответствующий позиции курсора, отображается в поле «входной код» (рис. 6. 46).

При нажатии кнопки «Set» в группе Clock (тактовый генератор) открывается диалоговое окно настройки параметров тактирования входных сигналов (рис. 6.47).

Тактирование сигналов осуществляется с использованием внешнего (External) или внутреннего (Internal) источника. В поле Clocl Qualifier устанавливается активный уровень сигнала синхронизации. В поле Clock Rate устанавливается частота выборки анализатора.

Рис. 6.46. Панель управления логического анализатора

В группе Sampling Setting задаются параметры выборки сигналов:

· Pre-trigger Samples – сбор данных производится до поступления импульса запуска;

· Post-trigger Samples – сбор данных начинается после поступления импульса запуска и продолжается до тех пор, пока не будет набрано заданное количество отсчетов;

· Treshold Volt (V) –пороговая величина;

Рис. 6.47. Настройка параметров синхронизации

Дополнительные условия запуска анализатора осуществляются с помощью диалогового окна Trigger Settings (рис. 6. 48). В данном окне настраивается маска, по которой осуществляется фильтрация логических уровней и синхронизация входных каналов.

Рис. 6.48. Настройка дополнительных параметров синхронизации