Мультиплексор

Mультипле́ксор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передавать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.

Аналоговые и цифровые мультиплексоры значительно различаются по принципу работы. Первые электрически соединяют выбранный вход с выходом (при этом сопротивление между ними невелико — порядка единиц/десятков ом). Вторые же не образуют прямого электрического соединения между выбранным входом и выходом, а лишь «копируют» на выход логический уровень ('0' или '1') с выбранного входа. Аналоговые мультиплексоры иногда называют ключами[3] или коммутаторами.

Устройство, противоположное мультиплексору по своей функции, называется демультиплексором. В случае применения аналоговых мультиплексоров (с применением ключей на полевых транзисторах) не существует различия между мультиплексором и демультиплексором; такие устройства могут называться коммутаторами.

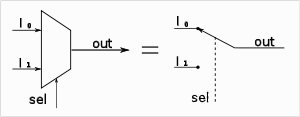

Схема мультиплексора.

Устройство

Схематически мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства. Коммутатор обслуживает управляющая схема, в которой имеются адресные входы и, как правило, разрешающие (стробирующие).

Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если между числом информационных входов и числом адресных входов действует соотношение, то такой мультиплексор называют полным. Если, то мультиплексор называют неполным.

Разрешающие входы используют для расширения функциональных возможностей мультиплексора. Они используются для наращивания разрядности мультиплексора, синхронизации его работы с работой других узлов. Сигналы на разрешающих входах могут разрешать, а могут и запрещать подключение определенного входа к выходу, то есть могут блокировать действие всего устройства.

В качестве управляющей схемы обычно используется дешифратор. В цифровых мультиплексорах логические элементы коммутатора и дешифратора обычно объединяются.

Обобщённая схема мультиплексора

Обобщённая схема мультиплексора.

Входные логические сигналы Xi поступают на входы коммутатора и через коммутатор передаются на выход Y. На вход управляющей схемы подаются адресные сигналы Ak (от англ. Address). Мультиплексор также может иметь дополнительный управляющий вход E (от англ. Enable), который разрешает или запрещает прохождение входного сигнала на выход Y.

Кроме этого, некоторые мультиплексоры могут иметь выход с тремя состояниями: два логических состояния 0 и 1, и третье состояние — отключённый выход (высокоимпедансное состояние, Z-состояние — выходное сопротивление равно бесконечности). Перевод мультиплексора в третье состояние производится снятием управляющего сигнала OE (от англ. Output Enable).

Использование

Мультиплексоры могут использоваться в делителях частоты, триггерных устройствах, сдвигающих устройствах и др. Мультиплексоры могут использоваться для преобразования параллельного двоичного кода в последовательный. Для такого преобразования достаточно подать на информационные входы мультиплексора параллельный двоичный код, а сигналы на адресные входы подавать в такой последовательности, чтобы к выходу поочередно подключались входы, начиная с первого и заканчивая последним.

Обозначение

Мультиплексоры обозначают сочетанием MUX (от англ. multiplexer), а также MS (от англ. multiplexer selector).

Условное графическое обозначение (УГО) мультиплексора «4 в 1».

Демультиплексоры

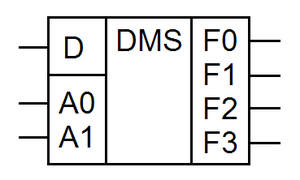

Демультиплексор — это логическое устройство, предназначенное для переключения сигнала с одного информационного входа на один из информационных выходов. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. На схемах демультиплексоры обозначают через DMX или DMS.

Условное графическое обозначение (УГО) демультиплексора «1 в 4».

Суть и схема реализации

В случае ТТЛ логики для коммутации каналов применяются логические элементы "И". В КМОП микросхемах широко применяются ключи на полевых транзисторах. Поэтому в них отсутствует понятие демультиплексора. Информационные входы и выход можно поменять местами, в результате чего мультиплексор может служить в качестве демультиплексора.

Если между числом выходов и числом адресных входов действует соотношение n=2m для двоичных демультиплексоров или n=3m для троичных демультиплексоров, то такой демультиплексор называют полным. Если n<2m для двоичных демультиплексоров или n<3m для троичных демультиплексоров, то демультиплексор называют неполным. Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют роль входов дешифратора. Поэтому в обозначении как дешифраторов, так и демультиплексоров в отечественных микросхемах используются одинаковые буквы - ИД.

Демультиплексоры выполняют унарные (одновходовые, однооперандные) логические функции с n-арным выходом.

Схема демультиплексора "2 на 4"

Компаратор и триггер Шмитта

Компаратор (аналоговых сигналов) (англ. comparator — сравнивающее устройство[1]) — электронная схема, принимающая на свои входы два аналоговых сигнала и выдающая логическую «1», если сигнал на прямом входе («+») больше, чем на инверсном входе («−»), и логический «0», если сигнал на прямом входе меньше, чем на инверсном входе.

Одно напряжение сравнения двоичного компаратора делит весь диапазон входных напряжений на два поддиапазона. Двоичный логический сигнал (бит) на выходе двоичного компаратора указывает, в каком из двух поддиапазонов находится входное напряжение.

Простейший компаратор представляет собой дифференциальный усилитель. Компаратор отличается от линейного операционного усилителя (ОУ) устройством и входного, и выходного каскадов:

Входной каскад компаратора должен выдерживать широкий диапазон входных напряжений между инвертирующим и неинвертирующим входами, вплоть до размаха питающих напряжений, и быстро восстанавливаться при изменении знака этого напряжения.

Выходной каскад компаратора выполняется совместимым по логическим уровням и токам с конкретным типом входов логических схем (технологий ТТЛ, ЭСЛ и т. п.). Возможны выходные каскады на одиночном транзисторе с открытым коллектором (совместимость с ТТЛ и КМОП логикой).

Для формирования гистерезисной передаточной характеристики компараторы часто охватывают положительной обратной связью. Эта мера позволяет избежать быстрых нежелательных переключений состояния выхода, обусловленном шумами во входном сигнале, при медленно изменяющемся входном сигнале.

При подаче эталонного напряжения сравнения на инвертирующий вход входной сигнал подаётся на неинвертирующий вход, и компаратор является неинвертирующим (повторителем, буфером).

При подаче эталонного напряжения сравнения на неинвертирующий вход входной сигнал подаётся на инвертирующий вход, и компаратор является инвертирующим (инвертором).

Несколько реже применяются компараторы на основе логических элементов, охваченных обратной связью (см., например, триггер Шмитта — не компаратор по своей природе, но устройство с очень схожей областью применения).

При математическом моделировании компаратора возникает проблема выходного напряжения компаратора при одинаковых напряжениях на обоих входах компаратора. В этой точке компаратор находится в состоянии неустойчивого равновесия. Проблему можно решить многими разными способами, описанными в подразделе «программный компаратор».

Аналоговый компаратор на операционном усилителе

Реализации

В аналоговой схемотехнике компаратор обычно реализуется на базе операционного усилителя, охваченного резистивной положительной обратной связью.

Компараторы с двумя и более напряжениями сравнения

Строятся на двух и более дифференциальных усилителях.

Компараторы, построенные на двух дифференциальных усилителях, можно условно разделить на двухвходовые и трёхвходовые. Двухвходовые компараторы применяются в тех случаях, когда сигнал изменяется достаточно быстро (не вызывает быстрых переключений состояния выхода, и на выходе генерируют один из потенциалов, которыми запитаны операционные усилители (как правило — +5В или 0В).

Троичный компаратор

Трёхвходовой (троичный) компаратор имеет два напряжения сравнения. Два напряжения сравнения делят весь диапазон входных напряжений на три нечётких поддиапазона в нечёткой (fuzzy) троичной логике, которым присваиваются три чётких значения в чёткой троичной логике. Двухбитный троичный (2B BCT) логический сигнал (трит) на выходе троичного компаратора указывает, в каком из трёх поддиапазонов находится входное напряжение. Логическая часть троичного компаратора выполняет унарную троичную логическую функцию — «повторитель» (F1073 = F810). Двухбитный троичный трит (2B BCT) может быть преобразован в трёхбитный трит (3B BCT) или в трёхуровневый трит (3LCT).

Троичный компаратор является простейшим одноразрядным троичным АЦП.

Троичный компаратор является переходником из нечёткой (fuzzy) троичной логики в чёткую троичную логику для решения задач нечёткой троичной логики средствами чёткой троичной логики.

Применяется в прецизионном триггере Шмитта с RS-триггером.

Троичный компаратор низкого качества с двоичными компараторами на цифровых логических элементах применён в троичном индикаторе напряжения источника питания с преобразованием двухбитного трита (2B BCT) в трёхбитный одноединичный трит (3B BCT)[2].

Многовходовые компараторы[править | править исходный текст]

Входной каскад параллельных АЦП прямого преобразования является многоуровневым компаратором. В нём применяются напряжений сравнения, где n — количество битов выходного кода.

Проходная характеристика неинвертирующего компаратора

Триггер Шмитта (не Шмидта) — электронный двухпозиционный релейный (переключающий) элемент, статическая характеристика которого имеет зону неоднозначности (петлю гистерезиса). Триггер Шмитта используется для восстановления цифрового сигнала, искаженного в линиях связи, фильтрах дребезга, в качестве двухпозиционного регулятора в системах автоматического регулирования, в двухпозиционных стабилизаторах-регуляторах напряжения. Этот триггер стоит особняком в семействе триггеров: он имеет один аналоговый вход и цифровой выход.

Механический триггер Шмитта с механическим гистерезисом применяется в регуляторах температуры холодильников.

Фазовая траектория (статическая характеристика) триггера Шмитта представляет собой характеристику переключателя, но с прямоугольной петлёй гистерезиса. Неоднозначность статической характеристики позволяет утверждать, что триггер Шмитта, как и другие триггеры обладает свойством памяти — его состояние в зоне неоднозначности определяется предысторией — ранее действовавшим входным сигналом.

В триггере Шмитта весь входной диапазон возможных напряжений делится входным троичным компаратором на три нечётких поддиапазона в нечёткой (fuzzy) троичной логике, которым присваиваются три чётких значения (трит) в чёткой троичной логике, в верхнем из которых (трит = +1) триггер устанавливается в "1", в среднем из которых (трит = 0) действия не производятся, а в нижнем из которых (трит = -1) триггер устанавливается в "0". Логическая часть триггера Шмитта выполняет сложную унарную троичную логическую функцию с памятью - "повторитель (F1073 = F810) с запоминанием в RS-триггере двух (трит = +1 и трит = -1) из трёх возможных состояний трита".

Описание

Триггер Шмитта представляет собой RS-триггер, управляемый одним входным аналоговым сигналом, с двумя разными напряжениями переключения в "1" и в "0", причём, напряжение переключения в "1" выше напряжения переключения в "0".

Простые реализации (быстродействующие, без обратной связи) состоят из RS-триггера и троичного компаратора на входе RS-триггера, в котором два напряжения сравнения, для переключения в "0" и для переключения в "1", устанавливаются раздельно[1][2][3][4].

Триггер Шмитта с обратной связью

В более сложных реализациях (с обратной связью, которая снижает быстродействие) цифровой выходной сигнал используется для переключения напряжения сравнения в обычном двоичном компараторе, превращая его и в троичный компаратор и в триггер на одних и тех же элементах. При "1" на выходе обратная связь уменьшает напряжение переключения, при "0" на выходе обратная связь увеличивает напряжение переключения. В таких реализациях затруднена раздельная установка напряжений переключения в "1" и в «0».

Простой (без обратной связи)

Аппаратный

Прецизионный триггер Шмитта с RS-триггером состоит из троичного компаратора на двух двоичных компараторах, среднее состояние которого не используется, и асинхронного RS-триггера[1][2][3]. Применён в интегральном таймере NE555 (КР1006ВИ1)[6], выпущенном в 1971 г.

Программный

В "программном прецизионном триггере Шмитта с RS-триггером" двумя компараторами троичного компаратора являются два оператора IF-THEN, а RS-триггером является нулевой разряд (бит) целой переменной RStrigger%, с двумя значениями ("0" и "1")[7].

При логических элементах с одинаковым временем задержки аппаратный триггер Шмитта имеет значительно большее быстродействие (tзадержки = 3dt, где dt - время задержки в одном логическом элементе), чем программный.

Более сложный (с обратной связью)

На аналоговых элементах

Эмиттерно-связанный триггер Шмитта на дифференциальном усилителе[8].

В аналоговой схемотехнике триггер Шмитта обычно реализуется на базе компаратора (операционного усилителя, охваченного резистивной положительной обратной связью) цифровой выходной сигнал которого, по этой же обратной связи, через время задержки, определяемое сопротивлением резистора обратной связи и распределённой ёмкостью, изменяет напряжение сравнения компаратора. В результате, компаратор становится троичным с двумя разными напряжениями переключения в "1" и в "0". Из-за этого в статической характеристике устройства появляется гистерезис, т.е. устройство приобретает свойства триггера.

Из-за дополнительной задержки в цепи обратной связи, может оказаться, что триггер Шмитта с обратной связью работает медленнее, чем триггер Шмитта без обратной связи. Кроме этого, в триггере Шмитта с обратной связью, после переключения триггера, существует интервал на котором действует предыдущее значение напряжения сравнения до прихода сигнала переключения напряжения сравнения по цепи обратной связи. Если на этом интервале произойдёт резкое изменение входного сигнала в другую сторону, то триггер переключится по предыдущему напряжению сравнения, т.е. преждевременно.

Использование аналоговых элементов, как цифрового триггера, создаёт триггер, но низкого качества, и ухудшает компараторные свойства устройства.

На цифровых логических элементах

Простейшая реализация триггера Шмитта на цифровых логических элементах — это два последовательно включенных инвертора, охваченные резистивной обратной связью, цифровой выходной сигнал которых через обратную связь изменяет напряжение переключения на входе. Скорость нарастания выходного сигнала не зависит от скорости нарастания входного сигнала, для данной технической реализации является величиной постоянной (зависит от быстродействия логических вентилей).

Использование цифрового логического элемента, как аналогового компаратора, ухудшает компараторные свойства устройства, а резистивная обратная связь ухудшает триггерные свойства устройства.