ИССЛЕДОВАНИЕ СТАТИЧЕСКИХ КМОП ТРИГГЕРОВ

Цель работы

Исследование свойств, а также параметров и характеристик статических КМОП триггеров с помощью программного средства схемотехнического моделирования HSpice и оценка значений последних вычислительными способами.

Лабораторные задания

2.1. (DFFRBSB) схема и входные файлы статического КМОП триггера управляемого положительным фронтом, с установкой низким уровнем асинхронных входов “0” и “1”.

2.1.1. Составить схему статического КМОП триггера управляемого положительным фронтом, с установкой низким уровнем асинхронных входов “0” и “1”, используя данные из таблицы 1 (Рис. 6.1):

|

|

|

|

Подложки n-МОП транзисторов подключены к VSS

Подложки p-МОП транзисторов подключены к VDD

Рис. 6.1. Условный знак, логическая схема, таблица истинности и виды входного и выходного сигналов статического КМОП триггера управляемого положительным фронтом, с установкой низким уровнем асинхронных входов “0” и “1”

2.1.2. Получить описание схемы (dffrbsb.netl файл) и расположить его по следующему адресу:

/student_lab/digital_ic/variant_val/...

2.1.3. Необходимые входные файлы для моделирования.

Для входных файлов принять:

· Продолжительность входного фронта: 50 псек

· Значение выходной емкостной нагрузки: Cload=5 фФ

2.1.3.1. Необходимый входной файл для статического КМОП триггера управляемого положительным фронтом, с установкой низким уровнем асинхронных входов “0” и “1”, используемый для измерения задержек и времени переключения в переходном режиме с применением программного средства схемотехнического моделирования HSpice, следующий:

| *Pos edge DFF, low active async set and reset *Propagation Delay, Transition Time * HSPICE Netlist .options POST=1 parhier=local * Models section * Include models .include '/student_lab/digital_ic/all_models/model_val' * Design variables section * Define parameters .param vdd = VDD_val .param tr=TR_val .param freq=FREQ_val .param per=’1/freq’ .param tst=’0.5*per’ .temp Temp_val * Structural netlist section .include '/student_lab/digital_ic/variant_val/variant_val/dffrbsb.netl' vvss vss gnd dc=0 vvdd vdd gnd dc='vdd' ***Input Signals vclk1 clk1 0 pwl (0 vdd 'tst+2.5*per' vdd 'tst+2.5*per+tr' 0) vclk2 clk clk1 pulse (0 vdd 'tst+6.5*per' tr tr '0.5*per-tr' '1.0*per') vd d 0 pulse (0 vdd 'tst+7.25*per' tr tr '1.0*per-tr' '2.0*per') vrstb0 rstb0 0 vdd vrstb1 rstb1 rstb0 pulse (0 '-vdd' 'tst-tr' tr tr '0.5*per-tr' '11.0*per') vrstb2 rstb rstb1 pulse (0 '-vdd' 'tst+3.0*per' tr tr '0.5*per-tr' '11.0*per') vsetb0 setb0 0 vdd vsetb1 setb1 setb0 pulse (0 '-vdd' 'tst+1.75*per' tr tr '0.5*per-tr' '11.0*per') vsetb2 setb setb1 pulse (0 '-vdd' 'tst+4.75*per' tr tr '0.5*per-tr' '11.0*per') cloadq q gnd LOAD_val cloadqn qn gnd LOAD_val * Analysis section * Transient Analyses .tran ‘0.01*tr’ ‘9*per’ .probe v(*) *Options .option post probe ***Measures ***Propagation Delay .meas tran tplh_clk_q trig v(clk) val='vdd*0.5' rise=2 targ v(q) val='vdd*0.5' rise=3 .meas tran tphl_clk_q trig v(clk) val='vdd*0.5' rise=3 targ v(q) val='vdd*0.5' fall=3 ***Transition Time .meas tran ttrlh_clk_q trig v(q) val='vdd*0.1' rise=3 targ v(q) val='vdd*0.9' rise=3 .meas tran ttrhl_clk_q trig v(q) val='vdd*0.9' fall=3 targ v(q) val='vdd*0.1' fall=3 .end |

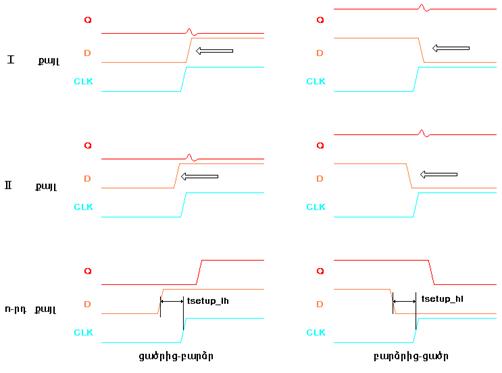

2.2. Процесс измерения времени установки (DFFRBSB) статического КМОП D триггера управляемого положительным фронтом, с установкой низким уровнем асинхронных входов “0” и “1” (Рис. 6.2).

|

|

|

|

|

|

Рис. 6.2. Процесс измерения времени установки статического КМОП D триггера управляемого положительным фронтом

2.2.1. Необходимые входные файлы для моделирования.

Для входных файлов принять:

· Продолжительность входного фронта: 50 псек

· Значение выходной емкостной нагрузки: Cload=5 фФ

2.2.1.1. Необходимый входной файл для статического КМОП триггера управляемого положительным фронтом, с установкой низким уровнем асинхронных входов “0” и “1”, используемый для измерения динамического времени установки от низкого до высокого с применением программного средства схемотехнического моделирования HSpice, следующий:

| *Pos edge DFF, low active async set and reset *Setup Time * HSPICE Netlist .options POST=1 parhier=local * Models section * Include models .include '/student_lab/digital_ic/all_models/model_val' * Design variables section * Define parameters .param vdd = VDD_val .param tr=TR_val .param freq=FREQ_val .param per=’1/freq’ .temp Temp_val * Structural netlist section .include '/student_lab/digital_ic/variant_val/dffrbsb.netl' vvss vss gnd dc=0 vvdd vdd gnd dc='vdd' ***Input Signals vsetb setb 0 vdd vrstb rstb 0 vdd vclk clk 0 pwl 0 0 per 0 'per+tr' vdd vd d 0 pwl 0 0 'per-tsetup' 0 'per-tsetup+tr' vdd .param tsetup = 150p ***Initial Conditions .ic v(q2)=0 cloadq q gnd LOAD_val cloadqn qn gnd LOAD_val * Analysis section * Transient Analyses .tran ‘0.01*tr’ ‘5*per’ .probe v(*) *Options .option post probe .end |

2.2.1.2. Необходимый входной файл для статического КМОП триггера управляемого положительным фронтом, с установкой низким уровнем асинхронных входов “0” и “1”, используемый для измерения динамического времени установки от высокого до низкого с применением программного средства схемотехнического моделирования HSpice, следующий:

| *Pos edge DFF, low active async set and reset *Setup Time * HSPICE Netlist .options POST=1 parhier=local * Models section * Include models .include '/student_lab/digital_ic/all_models/model_val' * Design variables section * Define parameters .param vdd = VDD_val .param tr=TR_val .param freq=FREQ_val .param per=’1/freq’ .temp Temp_val * Structural netlist section .include '/student_lab/digital_ic/variant_val/dffrbsb.netl' vvss vss gnd dc=0 vvdd vdd gnd dc='vdd' ***Input Signals vsetb setb 0 vdd vrstb rstb 0 vdd vclk clk 0 pwl 0 0 per 0 'per+tr' vdd vd d 0 pwl 0 vdd 'per-tsetup' vdd 'per-tsetup+tr' 0 .param tsetup = 150p ***Initial Conditions .ic v(q2)=0 cloadq q gnd LOAD_val cloadqn qn gnd LOAD_val * Analysis section * Transient Analyses .tran ‘0.01*tr’ ‘5*per’ .probe v(*) *Options .option post probe .end |

2.3. Процесс измерения времени установки (DFFRBSB) статического КМОП D триггера управляемого положительным фронтом, с установкой низким уровнем асинхронных входов “0” и “1” (Рис. 6.3).

Рис. 6.3. Процесс измерения времени установки статического КМОП D триггера управляемого положительным фронтом

2.3.1. Необходимые входные файлы для моделирования.

Для входных файлов принять:

· Продолжительность входного фронта: 50 псек

· Значение выходной емкостной нагрузки: Cload=5 фФ

2.3.1.1. Необходимый входной файл для статического КМОП D триггера управляемого положительным фронтом, с установкой низким уровнем асинхронных входов “0” и “1”, используемый для измерения динамического времени установки от низкого до высокого с применением программного средства схемотехнического моделирования HSpice, следующий:

| *Pos edge DFF, low active async set and reset *Hold Time * HSPICE Netlist .options POST=1 parhier=local * Models section * Include models .include '/student_lab/digital_ic/all_models/model_val' * Design variables section * Define parameters .param vdd = VDD_val .param tr=TR_val .param freq=FREQ_val .param per=’1/freq’ .temp Temp_val * Structural netlist section .include '/student_lab/digital_ic/variant_val/dffrbsb.netl' vvss vss gnd dc=0 vvdd vdd gnd dc='vdd' ***Input Signals vsetb setb 0 vdd vrstb rstb 0 vdd vclk clk 0 pwl 0 0 per 0 'per+tr' vdd vd d 0 pwl 0 vdd 'per+thold' vdd 'per+thold+tr' 0 .param thold = 0p ***Initial Conditions .ic v(q2)=0 cloadq q gnd LOAD_val cloadqn qn gnd LOAD_val * Analysis section * Transient Analyses .tran ‘0.01*tr’ ‘5*per’ .probe v(*) *Options .option post probe .end |

2.3.1.2. Необходимый входной файл для статического КМОП триггера управляемого положительным фронтом, с установкой низким уровнем асинхронных входов “0” и “1”, используемый для измерения динамического времени установки от низкого до высокого с применением программного средства схемотехнического моделирования HSpice, следующий:

| *Pos edge DFF, low active async set and reset *Hold Time * HSPICE Netlist .options POST=1 parhier=local * Models section * Include models .include '/student_lab/digital_ic/all_models/model_val' * Design variables section * Define parameters .param vdd = VDD_val .param tr=TR_val .param freq=FREQ_val .param per=’1/freq’ .temp Temp_val * Structural netlist section .include '/student_lab/digital_ic/variant_val/dffrbsb.netl' vvss vss gnd dc=0 vvdd vdd gnd dc='vdd' ***Input Signals vsetb setb 0 vdd vrstb rstb 0 vdd vclk clk 0 pwl 0 0 per 0 'per+tr' vdd vd d 0 pwl 0 0 'per+thold' 0 'per+thold+tr' vdd .param thold = 0p ***Initial Conditions .ic v(q2)=0 cloadq q gnd LOAD_val cloadqn qn gnd LOAD_val * Analysis section * Transient Analyses .tran ‘0.01*tr’ ‘5*per’ .probe v(*) *Options .option post probe .end |

Порядок выполнения работы

3.1. Исследование параметров и характеристик статического КМОП D триггера управляемого положительным фронтом, с установкой низким уровнем асинхронных входов “0” и “1”с помощью моделирования.

3.1.1. При переходном режиме -

а) Получить виды входного и выходного сигналов,

б) Измерить задержки tPHL и tPLH и определить их среднее значение (tP=tPHL+tPLH/2) (Таблица 9, пункт 3, 4),

в) Определить времена установки при переключении от низкого состояния к высокому и от высокого к низкому (Таблица 9, пункт 13). Для измерения времени установки с применением программного средства схемотехнического моделирования Hspice, определить во входном файле то наименьшее значение параметра tsetup, при котором будет иметь место правильное переключение. Данное значение параметра tsetup принять как время установки триггера (рис. 6.2).

г) Определить времена сохранения при переключении от низкого состояния к высокому и от высокого к низкому (Таблица 9, пункт 14). Для измерения времени сохранения с применением программного средства схемотехнического моделирования Hspice, определить во входном файле то наименьшее значение параметра thold, при котором будет иметь место правильное переключение. Данное значение параметра thold принять как время установки триггера (рис. 6.3).

3.1.2. Выполнить пункт 3.1.1, при:

a) LOAD_val = 0

b) LOAD_val = CLoad