Русак С.В. 09-Гео-1

Память часто разделяют на так называемую внутреннюю, которая выполняется на основе полупроводниковых БИС, и внешнюю — устройства для долговременного хранения информации (магнитные ленты, диски и т.п.). Ниже мы будем рассматривать только полупроводниковые запоминающие устройства (ЗУ).

По способу обращения к элементам различают адресные и ассоциативные ЗУ. В адресных БИС памяти обращение к элементам памяти производится по их физическим координатам, задаваемым двоичным кодом — адресом. Они бывают с произвольным обращением (выборкой), т.е. допускают любой порядок следования адресов, и с последовательным обращением, где выборка элементов памяти возможна только в определенном порядке— возрастания или убывания адресов. Архитектура микропроцессоров ориентирована в первую очередь на использование адресных ЗУ с произвольной выборкой.

По принципу построения полупроводниковые устройства памяти можно также разделить на энергонезависимые ЗУ «только для чтения» — постоянные запоминающие устройства ПЗУ или ROM и энергозависимые оперативные ЗУ с произвольной выборкой для чтения и записи или RAM.

ПЗУ Существует несколько их разновидностей, которые различаются принципом занесения информации, а также технологией изготовления.

Масочно-программируемые ПЗУ. Эти БИС выпускаются по различным технологиям (ТТЛ, МОП, КМОП). Информация заносится в них в процессе изготовления, обычно на финишном его участке и не может быть впоследствии изменена. В серийном производстве эти БИС относительно дешевы. Однако каждая «прошивка», т. е. заносимый в ПЗУ массив информации, требует соответствующей дорогостоящей технологической подготовки производства — индивидуальной маски (фотошаблона). Поэтому данный тип ПЗУ рентабельно применять в уже отлаженных изделиях, выпускаемых большими партиями.

Программируемые ПЗУ (ППЗУ) с плавкими перемычками поступают к потребителю в первоначальном незапрограммированном состоянии, соответствующем О или 1 (в зависимости от типа БИС) во всех элементах памяти. В режиме программирования можно записать в ППЗУ информацию путем пережигания перемычек электрическим током по специальной программе [49]. В дальнейшем изменение информации, занесенной в ППЗУ, возможно путем повторного программирования только в одном направлении — путем пережигания перемычек, оставшихся после предыдущего программирования.

Выпускается широкая гамма подобных микросхем серии КР556 на основе схем ТТЛШ. Их емкость достигает в настоящее время 2 кбайт (РТ16, РТ18).

ППЗУ с ультрафиолетовым стиранием информации в настоящее время наиболее широко используются в МП-системах. В этих БИС каждый бит хранимой информации отображается состоянием соответствующего МОП-транзистора с плавающим затвором. Затворы транзисторов при программировании заряжаются лавинной инжекцией, т. е. обратимым пробоем окружающего затвор изолирующего слоя под действием электрического импульса напряжением 18—26 В. Заряд в таких конденсаторах за счет высокого качества изолирующего слоя может сохраняться очень долго. Так, например, для отечественных ППЗУ серии К573 гарантируется сохранение информации не менее 15—25 тыс. ч во включенном состоянии и до 100 тыс. ч (К573РФ1), т.е. более 10 лет, — в выключенном.

Программирование ПЗУ обычно производят вне МП-системы, в которой предполагается их использовать, с помощью специальных устройств — программаторов. Последние часто выполняют в виде периферийных устройств ЭВМ, в которых производится подготовка, а также и хранение на внешних носителях записываемой в ПЗУ информации. Незапрограммированная микросхема ПЗУ с ультрафиолетовым стиранием имеет на выходах по всем адресам уровень логической единицы. Для записи в требуемые разряды логического нуля при установленном адресе на соответствующие выводы данных подается уровень 0, а на остальные — 1. Можно производить коррекцию ранее записанной информации, изменяя состояние 1 в любых разрядах на нулевое (но не наоборот).

Для полного программирования БИС типа К573РФ2 емкостью 2 кбайт требуется в стандартном режиме время порядка 100 с.

Для стирания информации в течение 30—60 мин облучают кристалл БИС сквозь прозрачное окно в корпусе ультрафиолетовым излучением люминесцентной лампы, которое увеличивает ток утечки в изолирующем слое, приводя к рассасыванию хранимого на плавающих затворах заряда.

Число циклов перезаписи обычно лежит в пределах 10—100 (для различных типов), так как при каждом программировании частично изменяется структура изолирующего слоя, что постепенно ухудшает его диэлектрические свойства.

ППЗУ с электрическим стиранием позволяет производить как запись, так и стирание (или перезапись) информации с помощью электрических сигналов. Для построения таких ППЗУ используются различные технологии и структуры элементов памяти. В частности, применяются структуры с лавинной инжекцией заряда, аналогичные тем, на которых строятся ППЗУ с ультрафиолетовым стиранием, но с дополнительными управляющими затворами, размещаемыми над плавающими. Подача напряжения на управляющий затвор приводитк рассасыванию заряда за счёт туннелирования носителей сквозь изолирующий слой.

Достоинством ППЗУ с электрическим стиранием является не только удобство и высокая скорость перезаписи информации, но и значительное допустимое число циклов перезаписи. Обычно гарантируется не менее 104 циклов.

Оперативные запоминающие устройства (ОЗУ) для записи — чтения информации в зависимости от структуры элементов памяти подразделяются на статические и динамические.

Элементы памяти в статических ОЗУ строятся на основе статических триггерных цепей. Хранение информации в триггере требует определенной мощности от источника питания, т. е. такое ЗУ является энергозависимым. Типовая реализация триггерного элемента памяти в nПМОПи КМОП-БИС ОЗУ (эти виды технологии в наибольшей степени прогрессируют в настоящее время составляет шеститранзисторную схему. Поэтому статические ОЗУ проигрывают в 4—8 раз по информационной емкости на кристалле динамическим ОЗУ, в которых запоминающий элемент выполняется однотран-зисторным.

Информация в таком элементе хранится в виде заряда на запоминающем конденсаторе, обкладками которого являются области стока МОП-транзистора и подложки. Запись и считывание информации производятся путем открывания транзистора по затвору и подключения тем самым запоминающей емкости к схеме усилителя-регенератора. Последний, по существу, является статическим триггерным элементом, который в зависимости от предварительной его подготовки или принимает (считывает) информацию из емкостной запоминающей ячейки, устанавливаясь при этом в состояние 0 или 1, или, наоборот, в режиме записи соответствующим образом заряжает ячейку, будучи предварительно установленным в 0 или 1.

В режиме чтения триггер усилителя — регенератора вначале специальным управляющим сигналом устанавливается в неустойчивое равновесное состояние, из которого при подключении к нему запоминающей емкости он переключается в 0 или 1. При этом вначале он потребляет часть заряда, а затем при установке в устойчивое состояние возвращает его ячейке, осуществляя таким образом регенерацию ее состояния.

В режиме хранения информации необходимо периодически производить регенерацию для компенсации естественных утечек заряда. Максимальный период цикла регенерации для каждой из ячеек обычно составляет 1— 2 мс. В принципе для полной регенерации можно было бы с таким периодом считывать содержимое каждой из ячеек ОЗУ. Однако это заняло бы слишком много времени. Поэтому архитектура БИС динамических ЗУ строится таким образом, что операция регенерации является групповой, т. е. при каждом обращении к ОЗУ регенерируется содержимое не одной ячейки, а целой строки. Поэтому, например, для регенерации БИС типа К565РУ5 емкостью 64 кбит необходимо обращение к каждой из 128 строк не реже, чем раз в 2 мс. Если учесть, что. регенерация одной строки занимает около 0,5 мкс, то общие потери времени на регенерацию составят примерно 3,2 %.

Регенерация может проводиться процессором программно, например с помощью специальных прерываний. Но чаще она реализуется аппаратно с помощью специального контроллера регенерации. Возможно также выполнение этой операции с помощью контроллера ПДП.

Построение модулей памяти МП-систем. Исходными «кирпичиками» при построении модулей памяти МП-систем служат отдельные БИС статической или динамической оперативной памяти, а также БИС ПЗУ. Отметим, что БИС памяти, выпускаемые различными фирмами, гораздо в большей степени стандартизованы по внешнему интерфейсу и даже в большинстве случаев по нумерации выводов по сравнению с другими типами микропроцессорных БИС.

При построении модулей памяти возникают задачи наращивания информационной емкости путем объединения БИС в соответствующую матрицу, а также буферизации шин адреса, данных и управления. Наращивание емкости может производиться двумя путями. Во-первых, можно расширять разрядность путем параллельного включения БИС. Последние в этом случае объединяются по всем выводам, кроме информационных, которые в совокупности образуют расширенную информационную шину.

Второй путь наращивания информационной емкости — объединение БИС памяти по информационным входам — выходам. Кроме них объединяются все остальные входы за исключением входов CS (выбор чипа). Сигналы на этих входах определяют, какой из микросхем необходимо включаться в работу. Максимальное число объединяемых таким образом БИС определяется допустимой емкостной нагрузкой на выходе микросхемы.

ПЗУ, как правило, выпускаются многоразрядными. Разрядность ПЗУ, так же как и разрядность МП, составляет 4, 8, 16. Это связано в первую очередь с удобством занесения и изменения информации в ПЗУ. Действительно, записывать информацию в ПЗУ целыми словами гораздо удобнее, чем, допустим, по одному разряду в каждое из нескольких ПЗУ, образующих заданную длину слова.

В последние годы стали выпускать БИС статических ОЗУ, аналогичных по цоколевке и назначению выводов программируемым ПЗУ. Например, ОЗУ типа К537РУ9 имеет, как и микросхемы ПЗУ типа К573РФ2, РФ5, организацию 2К X 8 и аналогичную цоколевку, за исключением одного вывода (21). У ПЗУ на этот вывод подается напряжение программирования, а в микросхеме ОЗУ — это вход управления записью WR.

Таким образом, можно представить себе резервирование на печатной плате посадочных мест под микросхемы памяти с практически идентичной разводкой выводов, куда в зависимости от решаемой задачи можно устанавливать микросхемы ОЗУ и ПЗУ в необходимом соотношении.

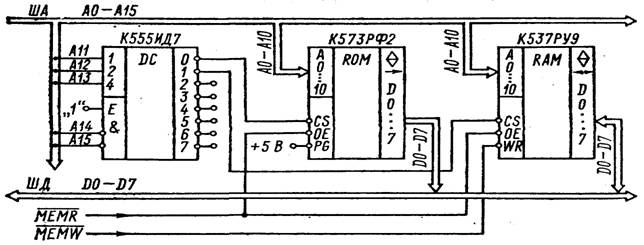

Пример схемы включения устройств памяти в МП-системе показан на рис. 1.

В данном случае используются микросхемы ПЗУ с ультрафиолетовым стиранием типа К573РФ2 или КФ573РФ5 и микросхемы статического ОЗУ типа К537РУ9. Каждая из этих микросхем способна хранить 2 кбайта информации, представленной в виде 2048 восьмиразрядных слов.-

Рис. 1. Схема включения устройств памяти

Выбор нужного слова производится с помощью одиннадцати адресных сигналов АО—А10. Кроме того, эти микросхемы имеют входы CS (выбор чипа), на которые подаются сигналы, зависящие от состояния старших разрядов адресной шины МП-системы All — А15. Как видно из рис. 1 управление этими входами осуществляется с помощью дешифратора типа К555ИД7. Микросхемы ПЗУ (ROM) и ОЗУ (RAM) включаются в работу тогда, когда старшие разряды адресной шины А15 — А11 будут находиться в состояниях 00000 и 00001. Таким образом, ячейки ПЗУ и ОЗУ занимают в адресном пространстве соответственно области 0000 Н— 07FF Н и 0800 H—0FFF Н.

Перевод выходов микросхем памяти в высокоимпедансное состояние производится при подаче логической единицы на входы ОЕ (разрешение выхода) с линии MEMR шины управления МП. Направление передачи информации в ОЗУ изменяется в зависимости от сигнала на линии MEMW шины управления.

В ПЗУ имеется вход включения режима программирования PG. Как уже указывалось, обычно программирование ПЗУ производится вне МП-системы. В обычном режиме (режиме чтения) на этот вход подается напряжение питания (+5 В).

При необходимости объем памяти в устройстве по схеме рис. 1 может быть увеличен. Это достигается путем включения дополнительных ПЗУ или ОЗУ. При этом микросхемы К573РФ2 или К537РУ9 включаются точно так же, как это показано на рис. 7.6, но их входы CS присоединяются к другим выходам дешифратора DC. Наибольшее число микросхем памяти, включаемых параллельно на шину данных без дополнительных буферов, как мы уже говорили, ограничено допустимой емкостной нагрузкой выходов микросхем памяти.

Рассмотренная схема включения устройств памяти рассчитана на управляющую шину МП типа ВМ80. Ес ли же пр именяетс я МП типа ВМ85, то вместо сигналов MEMR и MEMW используются сигналы RD и WR, а на один из входов разрешения дешифратора DC подается сигнал IO/M

Вопросы дл самоконтроля:

1. Что является носителем информации в системах цифровой записи?

2. Какие виды устройств памяти Вы знаете?

3. Схемы построения модулей памяти