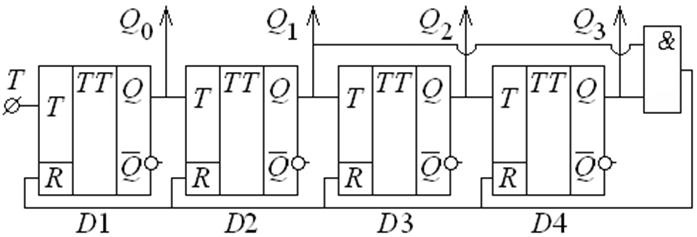

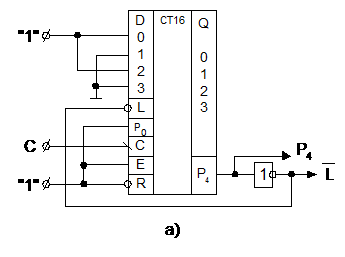

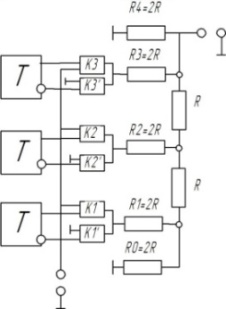

Двоично-десятичные (декадные) счетчики ведут счет в десятичной системе счисления. Каждая десятичная цифра от 0 до 9 кодируется четырехразрядным двоичным кодом, так называемой тетрадой. Эти устройства являются разновидностью счетчиков по модулю n. В своем составе они, как правило, имеют четыре триггера. Простейший двоично-десятичный счетчик представлен на рис. 11.

Рис. 11 Декадный счетчик

Логический элемент 2И выявляет первый запрещенный набор 1010, который соответствует десятичному числу 10, и производит сброс триггеров.

Такой счетчик хорошо работает при невысокой частоте входных импульсов.

Недостатком счетчика является кратковременное присутствие двоичного сигнала, соответствующего десятичной цифре 10, т.к. счетчик считает до 10 включительно, а затем удаляет это состояние. Устранение этого недостатка осуществляется аналогично техническому решению в схеме рис. 10.

С помощью нескольких декадных счетчиков можно производить подсчет количества единиц, десятков, сотен импульсов и т.д., присвоив каждому из счетчиков соответствующий вес. Данные счетчики бывают суммирующими, вычитающими и реверсивными.

Билет 53 Программируемые счетчики на основе двоичных, двоично-десятичных, реверсивных и нереверсивных, счетчики на сдвигающих регистрах.

Сдвигающий счетчик

Такой счетчик имеет 5 состояний: 10000 – исходное состояние, затем: 01000, 00100, 00010, 00001 и вернулись в исходное состояние 10000.

Программирование модуля пересчета двоичных счетчиков

В данной схеме модуль пересчета можно изменять с помощью загружаемого числа (dm) при j=const или методом переключения выхода дешифратора Kj приdm=const.

Выключение программирования осуществляется сигналом  = 1, в этом случае на выходах дешифратора устанавливаются лог. 1, L=1 - запрет загрузки.

= 1, в этом случае на выходах дешифратора устанавливаются лог. 1, L=1 - запрет загрузки.

Связь между числом dm, модулем пересчета счетчика и номером состояния счетчика можно выразить следующим выражением:

где М - модуль пересчета, i - состояние счетчика.

Схема программирования модуля пересчета с заданием дополнительного числа

Для изменения модуля пересчета счетчика (в постоянном режиме) можно использовать выход старшего переноса

В данной схеме счетчик имеет модуль пересчета 16. Для реализации M=11 на вход D поступает код dm=5. При появлении сигнала P4 осуществляется счет до 11 (5+11)=16. Эта схема чаще называется делителем с переменным коэффициентом деления. Для переключения счетчика из режима счета в режим загрузки можно использовать и выходы счетчика (Q0...Qi). Эти же сигналы можно использовать для задания числа dm

56. Оперативные запоминающие устройства с произвольной выборкой.

Полупроводниковые ЗУ подразделяются на ЗУ с произвольной выборкой и ЗУ с последовательным доступом. ЗУПВ подразделяются на:

-статические оперативные запоминающие устройства (СОЗУ);

-динамические оперативные запоминающие устройства (ДОЗУ). ЗУ с последовательным доступом подразделяются на:

-регистры сдвига;

- приборы с зарядовой связью (ПЗС).

В основе большинства современных ОЗУ лежат комплиментарные МОП ИМС (КМОП), которые отличаются малой потребляемой мощностью. Это достигается применением пары МОП транзисторов с разным типом канала: n-МОП и p-МОП.

Запоминающее устройство с произвольным доступом — один из видов памяти компьютера, позволяющий единовременно получить доступ к любой ячейке (всегда за одно и то же время, вне зависимости от расположения) по её адресу на чтение или запись

54. Назначение сумматоров. Полусумматоры и полные сумматоры.

Сумматор является простейшим цифровым устройством. Это узел ЭВМ, выполняющий арифметическое суммирование кодов чисел, т.е. он предназначен для сложения двух чисел, заданных в двоичном коде.

Одноразрядный двоичный сумматор состоит из двух комбинационных схем: одна формирования Si, вторая для определения Pi.. Многоразрядный сумматор строится на основе одноразрядных в соответствии с правилами сложения.

Полусумматоры — бинарные (двухоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма по модулю в данном разряде, а на другом — перенос в следующий (старший) разряд.

Полные сумматоры — (трёхоперандные) сумматоры по модулю с разрядом переноса, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма по модулю в данном разряде, а на другом — перенос в следующий (более старший разряд).

55.Постоянное запоминающее устройство, классификация ПЗУ

Запоминающие устройства (ЗУ) предназначены для хранения информации в системах различного назначения.

ЗУ на 40-50% определяют быстродействие всей системы.

Одним и важных параметров памяти является объём и быстродействие.

Постоянные запоминающие устройства – предназначены для постоянного энергонезависимого хранения информации.

Классификация

1 Масочное

2 Однократно-программируемые пользователем

3 перепрограммируемые

Масочные ПЗУ могут изготавливаться на основе матриц диодов, биполярных транзисторов или МОП транзисторов.

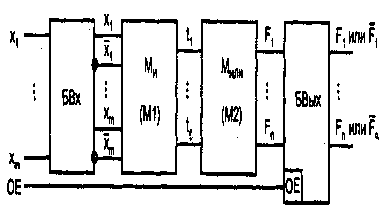

57. Программируемые логические матрицы и схемы логики. Схемы сборок на базе ПЛМ.

Программируемые логические матрицы появились в середине 70-х годов. Основой их служит последовательность программируемых матриц элементов И и ИЛИ. В структуру входят также блоки входных и выходных буферных каскадов (БВх и БВых). Входные буферы, если не выполняют более сложных действий, преобразуют однофазные входные сигналы в парафазные и формируют сигналы необходимой мощности для питания матрицы элементов И. Выходные буферы обеспечивают необходимую нагрузочную способность выходов, разрешают или запрещают выход ПЛМ на внешние шины с помощью сигнала ОЕ, а иногда выполняют и более сложные действия. Основными параметрами ПЛМ (рис. 7.1) являются число входов т, число термов I и число выходов п.

Переменные xj...xm подаются через БВх на входы элементов И (конъюнкторов), и в матрице И образуются £ термов. Под термом здесь понимается конъюнкция, связывающая входные переменные, представленные в прямой или инверсной форме. Число формируемых термов равно числу конъюнкторов или, что то же самое, числу выходов матрицы И.

Термы подаются далее на входы матрицы ИЛИ, т. е. на входы дизъюнкто-ров, формирующих выходные функции. Число дизъюнкторов равно числу вырабатываемых функций п.

Таким образом, ПЛМ реализует дизъюнктивную нормальную форму (ДНФ) воспроизводимых функций (двухуровневую логику). ПЛМ способна реализовать систему п логических функций от т аргументов, содержащую не более £ термов. Воспроизводимые функции являются комбинациями из любого числа термов, формируемых матрицей И. Какие именно термы будут выработаны и какие комбинации этих термов составят выходные функции, определяется программированием ПЛМ.

59. Принципы аналого-цифрового преобразования. Схемотехника АЦП.

Для передачи аналоговых сигналов по цифровым каналам их необходимо преобразовать в цифровую форму, то есть превратить их в сигналы дискретные по уровню и во времени. Для преобразования аналогового сигнала в цифровой применяют специальные устройства, которые называют аналого-цифровыми преобразователями (АЦП).В основе аналого-цифрового преобразования лежат три операции: дискретизация аналоговой функции во времени, квантование значений аналоговой функции по уровню и кодирование.

60. Цифро-аналоговый преобразователь с матрицей весовых резисторов.

Исходное двоичное число, предназначенное для перевода, помещается в регистр состоящий из сов-ти триггеров, выходное значение которых может принимать две величины, либо 0 либо Е.

Напряжение с выходов триггера подается на ЦАП ч/з усилитель, работающий в режиме сумм.напряжений.

Весовые коэф.вводятся для того, чтобы разделить по уровню входного сигнала разные разрядные значения исходного двоичного числа. Широкого распространения эта схема не получила по причине того, что невозможно обеспечить абсолютно точное соответствие используемых резисторов заявленных в схеме непостоянством величины Uвых триггера.

61. Цифро-аналоговый преобразователь с матрицей лестничного типа.

61. Цифро-аналоговый преобразователь с матрицей лестничного типа.

Широкого распространения эта схема не получила по причине того, что невозможно обеспечить абсолютно точное соответствие используемых резисторов заявленных в схеме непостоянством величины Uвых триггера. Указанные недостатки устраняются ЦАП на R-2R матрицы, т.к. используются сопротивления двух номиналов, а напряжение триггеров изменяет значение только ключей, количественно не влияет на величину выходного напряжения.

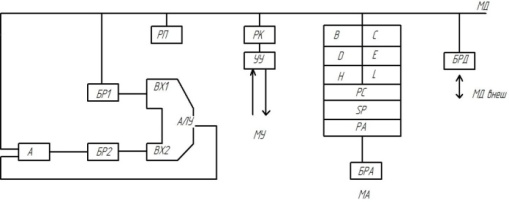

62. Однокристальные микропроцессоры, структурная схема ОМ. Основные узлы микропроцессора, их назначение и характеристики.

РК- регистр команд, BCDE - регистры общего назначения,PC- программный счетчик,SP – указатель стека, PA – регистр адреса,РП регистр признаков, БРА – буферный регистр адреса, БРД буферный регистр данных, МД- магистраль данных, МА – магистраль адреса, МУ магистраль управления, А- аккумулятор

АЛУ – комбинационное устройство, имеющие два входных порта и один выходной.

Аккумулятор – главный регистр микропроцессора. Для выполнения любой операции над данными нужно поместить их в аккумулятор

Блок РОН (регистр общего назначения) содержит шесть 8-разрядных регистров, обозначаемых буквами В, С, D, E, H, L, которые могут использоваться как одиночные 8-разрядные регистры, как регистровые 16-разрядные пары

УУ – обеспечивает необходимую послед. Действий мк-а и включает в себя дешифровку команд и формирователь сигналов управления. Программный счетчик следит за тем, какая команда выполняется и какая подлежит дальнейшему выполнению.

Основными узлами ЭВМ являются:

- центральный процессор (ЦП) (ЦП) = (УУ) + (АЛУ)

- оперативная память (ОЗУ)

- постоянное запоминающее устройство (ПЗУ)

- внешняя память (ВЗУ)

- устройства Ввода (УВв)

- устройства Вывода Все устройства ЭВМ подсоединены к единой информационной шине.

63. Разрядно-модульные микропроцессоры. Микропроцессоры с наращиваемой разрядностью шины данных.

Наряду с однокристальными МП широкое применение находят многокристальные секционированные (или их еще называют разрядно-модульные) микропроцессоры (СМП). Для СМП характерны: модульность построения, магистральные связи между модулями и микропрограммное управление. СМП имеют разрядность 2, 4, 8, 16 и изготовляются обычно на основе

технологии биполярных транзисторов.

СЕКЦИОНИРОВАННЫй МП состоит из модуля операционного устройства (ОУ); модуля устройства управления (УУ), содержащего в свою очередь: модуль памяти (обычно это ПЗУ) микрокоманд (ПЗУ МК) и модуль (блок) управления памятью микрокоманд (БУП МК); на входы УУ подаются код операции (КОП) и признаки условий (ПР)

Краткая характеристика основных модулей СМП: модуль операционного устройства (ОУ) предназначен для осуществления обработки данных и адресов. Секционность МП определяет возможность наращивания разрядности обрабатываемых данных или усложнения УУ микропроцессором при параллельном включении большого числа БИС(большая интегральная схема)

Вне зависимости от разрядности ОУ в него входят блоки: арифметических и логических операций, памяти (сверхоперативной) на РОН и местное устройство управления.

Модуль (блок) управления памятью микрокоманд предназначен для приема команды и формирования последовательности адресов для памяти микрокоманд в зависимости от признаков результата, поступающих из ОУ.

Модуль памяти (ПЗУ) микрокоманд предназначен для хранения управляющей информации.

Модуль обмена информацией с устройствами ввода-вывода (УВВ) предназначен для приема и выдачи информации, а также для организации приоритетной обработки информации при работе МП с внешними устройствами (ВУ).

В качестве достоинств СМП по сравнению с однокристальными можно отметить следующие:

-повышенное быстродействие, на практике в 5... 10 раз; оно достигается за счет увеличения числа БИС и уменьшения степени их интеграции, что позволяет выделить на транзистор большую мощность, а следовательно, получить большее быстродействие

-большую универсальность; если однокристальный МП имеет фиксированный набор команд, то СМП позволяет определить в процессоре свой собственный набор команд и соответствующую архитектуру аппаратных средств с тем, чтобы получить особые воможности или чтобы выполнить задачу с максимальной эффективностью

-возможность построения на базе СМП операционных устройств с распределенной обработкой информации путем введения дополнительных модулей, обеспечивающих аппаратное или микропрограммное выполнение операций типа умножения, деления, индексной арифметики, операций над числами с плавающей запятой и регистровых модулей для хранения информации.