Логическая схема шифратора.

Назначение шифратора в цифровых системах является введение первичной информации с клавиатуры. При нажатии любой клавиши на соответствующий вход шифратора подается сигнал(лог.ед.),который преобразуется на выходе в двоичный код.

Дешифратор.

Дешифратором называется комбинационное логическое устройство для преобразования чисел из двоичной системы счисления в десятичную. каждому входному двоичному числу ставится в соответствие сигнал, формируемы на определенном выходе устройства. По сути обратная операция шифратора. Дешифратор будет полным если число адресных кодов n связанно с числом его выходов m соотношением m=2n-полный., если m<2n -неполный.Поведение описывается таблицей истинности, как у шифратора, только входы и выходы поменяны местами.

Одно из основных применений шифратора – ввод данных с клавиатуры, при котором нажатие на клавишу с десятичной цифрой должно приводить к передаче в устройство этой цифры в двоичном коде. При нажатии любой из десяти цифровых клавиш единица появляется только на одном из десяти входов шифратора X 0, X 1,..., X 9.На выходе шифратора должен появиться двоичный код (y 0 y 1 y 2 y 3)введенного десятичного числа. Из таблицы истинности (табл. 4.4) видно, что в этом случае нужен преобразователь с десятью входами и четырьмя выходами, т.е. так называемый шифратор 10 – 4.

49.Назначение и классификация регистров. Параллельные сдвигающие регистры, последовательные сдвигающие регистры.

Регистр -устройство предназначенное для хранения одного разрядного числа, представленного в двоичной форме. Следовательно, для хранения n-разрядного машинного слова регистр должен содержать nтриггеров.Регистр представляет собой упорядоченный набор триггеров, обычно D-, число n которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Основой построения регистров являются: D-триггеры, RS-триггеры, JK-триггеры.

Регистры классифицируются по следующим видам:

•накопительные (регистры памяти, хранения);

•сдвигающие.

В свою очередь сдвигающие регистры делятся:

по способу ввода-вывода информации:

· параллельные: запись и считывание информации происходит одновременно на все входы и со всех выходов;

· последовательные: запись и считывание информации происходит в первый триггер, а та информация, которая была в этом триггере, перезаписывается в следующий — то же самое происходит и с остальными триггерами;

O комбинированные;

• по направлению передачи информации:

O однонаправленные;

O реверсивные.

Последовательный регистр обычно служит для преобразования последовательного кода в параллельный и наоборот, а также для сдвига хранимого в регистре числа на определенное количество разрядов влево или вправо. Его используют для передачи большого количества двоичной информации по ограниченному количеству соединённых линий. Входы синхронизации в последовательных (сдвиговых) регистрах, как и в параллельных объединяются. Это обеспечивает одновременность смены состояния всех триггеров, входящих в состав последовательного регистра. Преобразование последовательного кода в параллельный в последовательном регистре производится след. Образом: Отдельные биты двоичной информации последовательно подаются на вход сдвигового регистра D0. Каждый бит сопровождается отдельным тактовым импульсом синхронизации, который поступает на вход синхронизации последовательного регистра C. Через n тактов число окажется принятым в регистр и может затем быть снято в параллельной форме с выходов триггеров всех разрядов.

Перевод числа из параллельной формы в последовательную может быть выполнен сдвиговым регистром, у которого предусмотрены входы для приёма числа в параллельной форме. После записи в регистр n-разрядного слова на выходе триггера первого разряда, мы получим младший разряд числа. При сдвиге числа на один разряд вправо в триггере первого разряда передаётся цифра второго разряда и так далее. Таким образом, при повторении сдвигов вправо (n-1) раз на выходе триггера первого разряда регистра последовательно появляются цифры всех nразрядов.

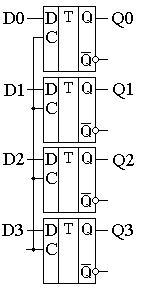

Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного) слова. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырёхразрядного параллельного регистра приведена на рисунке 1, а его условно-графическое обозначение — на рисунке 2.

При записи информации в параллельный регистр все биты (двоичные разряды) должны быть записаны одновременно. Для уменьшения входного тока вывода синхронизации C на этом входе в качестве усилителя часто ставится инвертор.

51. Назначение и классификация счетчиков. Принцип работы счетчика на триггерах. Деление частоты, коэффициент деления.

Основной параметр счётчика — модуль счёта — максимальное число единичных сигналов, которое может быть сосчитано счётчиком. Счётчики обозначают через СТ (от англ. counter).

Классификация[править | править вики-текст]

Счётчики классифицируют:

- по числу устойчивых состояний триггеров

- на двоичных триггерах

- на троичных триггерах[1]

- на n-ичных триггерах

- по модулю счёта:

- двоично-десятичные (декада);

- двоичные;

- с произвольным постоянным модулем счёта;

- с переменным модулем счёта;

- по направлению счёта:

- суммирующие;

- вычитающие;

- реверсивные;

- по способу формирования внутренних связей:

- с последовательным переносом;

- с ускоренным переносом;

- с параллельным ускоренным переносом;

- со сквозным ускоренным переносом;

- с комбинированным переносом;

- кольцевые;

- по способу переключения триггера:

- синхронные;

- асинхронные;

- Счётчик Джонсона[2]

Счетчики используются для построения таймеров или выборке инструкций из пзу в микропроцессорах. Они могут использоваться как делители частоты в управляемых генераторах частоты.

коэф.деления: показывает соотношение между частотой импульсов на входе счетчика и частотой на выходе последнего триггера.

Счетчик представляет собой несколько последовательно включенных триггеров.

Билет 52 Двоичные и двоично десятичные счетчики. Риверсивные и нереверсивные двоичные счетчики

Модуль двоичного счетчика – целая степень числа 2 (М=2n), а его выходное состояние выражается двоичным кодом Qn-1…..Q0, считываемым по выходам триггеров разрядов.

Временная диаграмма

1 – Вход, 2- Q0, 3 – Q1, 4 – Q2. 5 – Q3.

Десятичный счетчик.. Десятичный счетчик состоит из декадных счетчиков, причем число декадных счетчиков равно максимальному разряду десятичных чисел, которые счетчик может считать. Каждый декадный счетчик является двоично-десятичным. Он считает в двоично-десятичном коде от 0 до 10. При поступлении на вход декадного счетчика десятого импульса все его выходы устанавливаются в нулевое состояние.

Временная диаграмма

Реверсивный счетчик служит ля сложения или вычитания поступающих импульсов. Как правило, реверсивные счетчики выполняются синхронными. В рассматриваемой схеме сигналы синхронизации со входа С поступают на все триггеры, но разрешение счета каждого из триггеров формируется в зависимости от направления счета и состояния предыдущих счетчиков. В суммирующем режиме (Режим = 0) переход каждого триггера разрешается, если во всех младших до него разрядах установлены лог.1. В вычитающем режиме триггер переключается, если во всех младших разрядах лог.0.