Рис. 2 – Функциональная схема шинного формирователя i8216

Назначение и особенности применения ШФ i8216 аналогичны ШФ i8286. Незначительные отличия связаны разрядностью: i8216 – это 4-разрядный ШФ. Поэтому для соединения двух 8-разрядных шин необходимо использовать два ШФ i8216, которые будут работать параллельно. Кроме того, в ШФ i8216 вход DI(3-0) и выход DO(3-0) являются однонаправленными, что в общем случае позволяет обеспечить большую гибкость при их использовании.

При их применении в проектируемой МК-системе вход DI(3-0) и выход DO(3-0) необходимо поразрядно соединить друг с другом (на схеме на рис. 2 это показано пунктиром) и затем подключить к соответствующим линиям порта МК.

Таблица истинности i8216

| CS/ | DCE | Направление |

| DI à DB | ||

| DB à DO | ||

| X | Нет передачи (Z – третье состояние) |

Поскольку таблицы истинности i8216 и i8286 совпадают, сигналы на управляющие входы  и

и  i8216 подаются аналогичным образом:

i8216 подаются аналогичным образом:

;

;  .

.

Описание функциональной схемы буферного регистра i8282 (К580ИР82)

Буферный регистр i8282 содержит восемь триггеров и предназначен для запоминания 8 бит информации на время, определяемое периодом поступления синхросигналов на вход STB. После фиксации в восьми триггерах данные могут появиться на выходе DO(7-0) при наличии разрешающего нулевого уровня на активно низком входе  , как следует из функциональной схемы i8282, на рис. 3.

, как следует из функциональной схемы i8282, на рис. 3.

Рис. 3 – Функциональная схема буферного регистра i8282

В проектируемой МК-системе i8282 используется в качестве буферного регистра адреса (РгА), и фиксирует на один командный цикл младший байт адреса, который поступает на вход DI(7-0) из порта BUS МК i8048. Выход DO(7-0) соединяется с шиной адреса A(7-0) МК-системы. Старшие разряды адреса A(11-8) формируются на выходах порта P2(3-0) МК. Поскольку МК является единственным источником адреса для внешних устройств, то на управляющий вход  буферного регистра адреса подается постоянный нулевой уровень, т. е вход

буферного регистра адреса подается постоянный нулевой уровень, т. е вход  должен быть «заземлен». Поэтому после записи битов адреса в РгА по синхросигналу, подаваемому с выхода ALE (САВП) МК на вход STB РгА, они сразу появляются на выходе DO(7-0).

должен быть «заземлен». Поэтому после записи битов адреса в РгА по синхросигналу, подаваемому с выхода ALE (САВП) МК на вход STB РгА, они сразу появляются на выходе DO(7-0).

Функциональная схема буферного регистра i8212 (К580ИР12)

Микросхема i8212 является 8-разрядным многорежимным буферным регистром, который в проектируемой МК-системе применяется так же, как и i8282, в качестве буферного РгА для восьми младших адресных разрядов. Режим записи данных с входа DI (7-0) в восемь триггеров определяется состоянием входа режима MD, как следует из функциональной схемы i8212 на рис. 4. Рекомендуется задать MD=0, тогда сигнал записи W R будет формироваться по синхросигналу на входе STB, аналогично варианту РгА на базе i8282.

Рис. 4 – Функциональная схема многорежимного буферного регистра i8212

Требуется задать логический нуль на входе  и логическую единицу на воде CS 2 для того, чтобы RD был постоянно активным и разрешал выдачу битов адреса с прямых выходов Q триггеров на выход DO (7-0) РгА. Чтобы вход CLR не влиял на работу РгА, на него надо подать логический нуль.

и логическую единицу на воде CS 2 для того, чтобы RD был постоянно активным и разрешал выдачу битов адреса с прямых выходов Q триггеров на выход DO (7-0) РгА. Чтобы вход CLR не влиял на работу РгА, на него надо подать логический нуль.

Содержание лабораторной работы №1 «Проектирование МК-системы с внешней памятью программ»

Цель работы: освоение методики проектирования цифровых устройств с расширенным набором периферийный устройств в САПР Orcad 9.2.

Задача: создать электронную версию принципиальной схемы микроконтроллерной системы с внешней памятью программ (ВПП) в соответствии с вариантом задания.

Перед созданием в Orcad электронной версии принципиальной схемы составить и защитить у преподавателя карту памяти для заданного варианта, в которой показано распределение и селекция БИС памяти в адресном пространстве МК-системы.

Порядок выполнения.

1. Запустить программу Capture CIS. Создать новый проект - project или design под своей фамилией в папке своей группы на студенческом диске.

2. В меню «Опции » задать ед. измерения –мм, формат чертежа - A2, заполнить поля штампа.

3. Для включения в проект требуемых электронных компонент (микросхем) подключить к проекту библиотеку OLDLIB, в ней активировать необходимые библиотеки:

- Intel, содержит БИС серии 80хх микроконтроллеров и 82хх - УВВ, ШФ, Рг;

- ROM, содержит БИС ПЗУ, ППЗУ различных конфигураций;

- Muxdecoder, содержит интегральные схемы мультиплексоров и декодеров (дешифраторов);

- Gate, содержит интегральные схемы (ИС) серии 74хх логических элементов – И, ИЛИ, НЕ.

4. Разместить на чертеже проекта требуемые по варианту задания БИС и ИС, расположив их в соответствии со структурной схемой МК-системы, приведенной на рис.5.

|

Рис. 5 – Структура МК-системы с внешней памятью программ

5. Соединить отдельные входы и выходы БИС и ИС с помощью отдельных линий (проводников) с помощью опции WIRE.

6. Проложить шины в соответствии со структурой МК-системы, приведенной на рис.5, с помощью опции BUS.

7. Подключить группы одноименных входов и выходов с помощью отдельных линий (проводников) с помощью опции WIRE к шинам (см. рис.5).

Содержание лабораторной работы №2 «Проектирование МК-системы с внешней памятью данных»

Задача: создать электронную версию принципиальной схемы МК-системы с внешней памятью данных (ВПД) в соответствии с вариантом задания.

Перед созданием в Orcad электронной версии принципиальной схемы составить и защитить у преподавателя карту памяти для заданного варианта, в которой показано распределение и селекция БИС памяти в адресном пространстве МК-системы.

Порядок выполнения.

1. Запустить программу Capture CIS. Открыть созданный в первой лабораторной работе проект - project или design под своей фамилией в папке своей группы на студенческом диске.

2. Для включения в проект требуемых электронных компонент (микросхем) подключить к проекту библиотеку OLDLIB, в ней активировать необходимые библиотеки:

- Muxdecoder, содержит интегральные схемы мультиплексоров и декодеров (дешифраторов);

- Gate, содержит интегральные схемы (ИС) серии 74хх логических элементов – И, ИЛИ, НЕ.

- SRAM, содержит БИС ОЗУ различных конфигураций;

3.

|

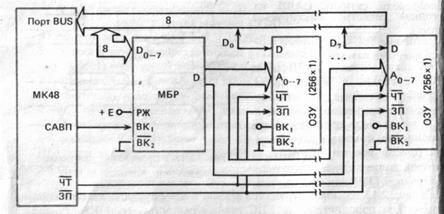

Разместить на чертеже проекта требуемые по варианту задания БИС ОЗУ, упрощенный пример структурной схемы МК-системы с ВПД приведен на рис.6.

Рис. 6 – Структура МК-системы с внешней памятью данных

8. Соединить отдельные входы и выходы БИС и ИС с помощью отдельных линий (проводников) с помощью опции WIRE.

9. Проложить шины в соответствии со структурой МК-системы, приведенной на рис.6, с помощью опции BUS.

10. Подключить группы одноименных входов и выходов с помощью отдельных линий (проводников) с помощью опции WIRE к шинам (см. рис.6).

Содержание лабораторной работы №3 «Проектирование МК-системы с расширенным вводом-выводом»

Задача: создать электронную версию принципиальной схемы МК-системы с единым адресным пространством периферийных БИС устройств ввода-вывода(УВВ) и внешней памятью данных (ВПД) в соответствии с вариантом задания.

Перед созданием в Orcad электронной версии принципиальной схемы составить и защитить у преподавателя карту памяти для заданного варианта, в которой показано распределение и селекция БИС памяти и периферийных устройств в адресном пространстве МК-системы.

Порядок выполнения.

4. Запустить программу Capture CIS. Открыть созданный в первой лабораторной работе проект - project или design под своей фамилией в папке своей группы на студенческом диске.

5. Для включения в проект требуемых электронных компонент (микросхем) подключить к проекту библиотеку OLDLIB, в ней активировать необходимые библиотеки:

- Intel, содержит БИС серии 80хх микроконтроллеров и 82хх - УВВ, ШФ, Рг;

- Muxdecoder, содержит интегральные схемы мультиплексоров и декодеров (дешифраторов);

- Gate, содержит интегральные схемы (ИС) серии 74хх логических элементов – И, ИЛИ, НЕ.

6. Разместить на чертеже проекта требуемые по варианту задания БИС УВВ, добавив их к структурной схеме МК-системы, созданной во второй лабораторной работе в соответствии с рис.6.

11. Соединить отдельные входы и выходы БИС и ИС с помощью отдельных линий (проводников) с помощью опции WIRE.

12. Проложить шины в соответствии со структурой МК-системы, приведенной на рис.6, с помощью опции BUS.

13. Подключить группы одноименных входов и выходов с помощью отдельных линий (проводников) с помощью опции WIRE к шинам (см. рис.6).