ЛАБОРАТОРНАЯ РАБОТА № 1

Краткие теоретические сведения

Маршрут проектирования цифровых устройств на базе ПЛИС фирмы Xilinx

Для создания цифрового устройства на базе ПЛИС Xilinx необходимо выполнить следующую последовательность операций:

1) создать новый проект, указав серию, тип ПЛИС и средств синтеза;

2) разработать описание проектируемого устройства в схемотехнической (с использованием схемотехнического редактора), алгоритмической (с использованием графа состояний конечного автомата) или текстовой (с использованием языков описания аппаратуры – hardware description languages, HDL) формах;

3) выполнить синтез устройства;

4) провести проверку проекта методом функционального моделирования;

5) выполнить размещение и трассировку проекта в кристалл;

6) провести окончательную верификацию проекта методом временного моделирования;

7) загрузить конфигурационные данные проекта в кристалл (выполнить программирование ПЛИС).

Операции функционального и временного моделирования не являются обязательными, но позволяют значительно сократить общее время разработки устройства за счет раннего обнаружения возможных ошибок.

Программирование ПЛИС с помощью языка VHDL

К современным HDL‑языкам относятся VHDL (Very High Speed HDL) и Verilog.

Проект на VHDL состоит из макросов, на основе которых строится описание схемы в целом. Структура макроса имеет вид, показанный на рис. 1.1.

Рис. 1.1. Структура макроса, написанного на языке VHDL

Способы представления переключательных функций (ПФ)

Функция  называется переключательной (булевой), если она принимает значения

называется переключательной (булевой), если она принимает значения  также как и ее аргументы, и зависит от аргументов

также как и ее аргументы, и зависит от аргументов  .

.

Существуют следующие способы представления (ПФ):

1) табличный;

2) номером ПФ;

3) указанием номеров наборов, на которых ПФ равна единице;

4) указанием номеров наборов, на которых ПФ равна нулю;

5) представление ФП в Совершенной дизъюнктивной нормальной форме (СовДНФ);

6) Представление ФП в Совершенной конъюнктивной нормальной форме (СовКНФ);

7) графический.

Для записи ПФ в СовДНФ используется вспомогательная функция, которая называется конституентой единицы (КЕ). Обозначение:  .

.

КЕ – это ПФ  ‑аргументов, равная единице только на одном

‑аргументов, равная единице только на одном  ‑м наборе. КЕ представляет собой элементарное произведение (конъюнкцию)

‑м наборе. КЕ представляет собой элементарное произведение (конъюнкцию)  ‑аргументов, взятых с инверсиями или без.

‑аргументов, взятых с инверсиями или без.

СовДНФ ПФ записывается следующим образом:

1. Выписывается ряд произведений всех аргументов и соединяется знаками дизъюнкции. Число произведений равно числу единиц ПФ.

2. Под каждым произведением записывается номер (двоичный набор), на котором ПФ равна единице. Над аргументом, стоящим напротив нуля, ставится инверсия.

Для записи ПФ в СовКНФ используется вспомогательная функция, которая называется конституентой нуля (КН). Обозначение:  .

.

КН – это ПФ  ‑аргументов, равная нулю только на одном

‑аргументов, равная нулю только на одном  ‑м наборе. КН представляет собой элементарную дизъюнкцию всех аргументов, взятых с инверсиями или без.

‑м наборе. КН представляет собой элементарную дизъюнкцию всех аргументов, взятых с инверсиями или без.

СовКНФ ПФ образуется следующим образом:

1. Записываются конъюнкции элементарных дизъюнкций всех аргументов. Число дизъюнкций равно числу нулей ПФ.

2. Под каждой дизъюнкцией записывается двоичное число номера набора, на котором ПФ равна нулю. Над аргументом, стоящим напротив единице, ставится инверсия.

Карта Карно – это разновидность табличного способа ПФ (таблицы истинности), которые позволяют просто осуществить операцию минимизации и найти минимальную ДНФ (МДНФ) и минимальную КНФ (МКНФ).

Число клеток в карте Карно равно числу наборов ПФ. Каждая клетка соответствует определенному набору. В карте Карно строке и столбцу, охваченным квадратной скобкой, соответствует прямое значение аргумента, т.е. логическая единица. На неохваченных – логический ноль.

Порядок минимизации ПФ с помощью карт Карно при поиске МДНФ:

1. ПФ представляется с помощью карт Карно. При поиске МДНФ нули можно не указывать.

2. Охватываются контурами «соседние» единицы карты. Число единиц в правильном контуре равно  (где

(где  ). При этом требуется, чтобы контуры были максимальны по числу охватываемых единиц, а число всех контуров – минимальным. При формировании контуров некоторые контуры могут охватывать единицы из других контуров.

). При этом требуется, чтобы контуры были максимальны по числу охватываемых единиц, а число всех контуров – минимальным. При формировании контуров некоторые контуры могут охватывать единицы из других контуров.

3. Для карт Карно трех переменных контур, содержащий одну единицу, заменяют произведением (простой импликантой), содержащей три буквы; две соседние единицы – двумя буквами; четыре соседние единицы – одной буквой; восемь единиц – ПФ константа «1».

4. Полученные произведения заменяют знаком дизъюнкции.

Порядок минимизации ПФ с помощью карт Карно при поиске МКНФ:

1. ПФ представляется в карте Карно ее нулями, единицы можно не указывать.

2. Образуются контуры, охватывающие нули.

3. Контуры, содержащие один ноль заменяются элементарной дизъюнкцией, cодержащей 4 буквы; 2 нуля – 3 буквы;4 нуля – 2 буквы;8 нулей – 1 буква.

4. Полученные элементарные дизъюнкции соединяются знаками конъюнкции.

Цель работы: изучение способов представления переключательных функций (ПФ), построение их логических схем и реализация на языке VHDL.

Исходные данные: ПФ, заданная номером (табл. 1.1).

Подготовка к работе: перед выполнением работы изучить теоретический материал по литературе и лекциям, выполнить пункты 1 – 6 задания для получения допуска к выполнению лабораторной работы.

Таблица 1.1. Варианты заданий

| № варианта | ||||||||||

| ПФ |

|

|

|

|

|

|

|

|

|

|

| № варианта | ||||||||||

| ПФ |

|

|

|

|

|

|

|

|

|

|

Задание:

1) перейти от задания ПФ номером к табличному способу задания ПФ;

2) найти СовДНФ и СовКНФ ПФ по ее таблице истинности;

3) с помощью карт Карно найти МДНФ и МКНФ ПФ;

4) построить в универсальном (булевом) базисе логические схемы (ЛС) ПФ, представленных в виде МДНФ и МКНФ;

5) построить временные диаграммы работы ЛС;

6) написать программу на VHDL, реализующую МДНФ и МКНФ заданной ПФ в редакторе Xilinx ISE;

7) провести моделирование написанной программы в редакторе HDL Bencher;

8) получить конфигурационную последовательность проекта для конкретной микросхемы ПЛИС и посмотреть ее в редакторе связей Floorplanner.

Содержание отчета:

1) название, цель работы, задание;

2) проектирование схемы в соответствии с планом задания (п.п. 1 – 6 задания);

3) результаты моделирования схемы в схемотехническом редакторе;

4) вид конфигурационной последовательности из редактора связей.

Пример выполнения работы.

Исходные данные:  .

.

1‑й этап. Переход от задания номером к табличному способу задания ПФ.

Номер функции необходимо представить в виде степеней двойки. Так:  . Каждой степени числа "2" соответствует определенный номер набора (табл. 1.2). Поэтому ПФ

. Каждой степени числа "2" соответствует определенный номер набора (табл. 1.2). Поэтому ПФ  на 0‑м, 1‑м, 3‑м, 4‑м и 7‑м наборах принимает единичные значения, на остальных – нулевые.

на 0‑м, 1‑м, 3‑м, 4‑м и 7‑м наборах принимает единичные значения, на остальных – нулевые.

Таблица 1.2. Табличное задание ПФ

| № набора |

|

|

| Вес набора |

|

| |||||

| |||||

| |||||

| |||||

| |||||

| |||||

| |||||

|

2‑й этап. СовДНФ и СовКНФ для ПФ, заданной в табл. 1.2, примут вид:

СовДНФ =  ; (1.1)

; (1.1)

СовКНФ =  . (1.2)

. (1.2)

3‑й этап. Нахождение МДНФ и МКНФ с помощью карт Карно.

Карты Карно для ПФ (1.1) и (1.2) показаны на рис. 1.2.

Рис. 1.2. Карты Карно для нахождения МДНФ и МКНФ функций (1.1) и (1.2)

Из карт Карно (см. рис. 1.1) найдены:

МДНФ =  ; (1.3)

; (1.3)

МКНФ =  . (1.4)

. (1.4)

4‑й этап. Построение ЛС для ПФ, представленных в виде МДНФ (1.3) и МКНФ (1.4) (рис. 1.3).

5‑й этап. Построение временных диаграмм для полученных ЛС (рис. 1.4).

6‑й этап. Написание программы на VHDL, реализующей МДНФ и МКНФ ПФ в редакторе Xilinx ISE.

Рис. 1.3. Логические схемы, соответствующие МДНФ (а) и МКНФ (б) ПФ

Рис. 1.4. Временная диаграмма для ПФ

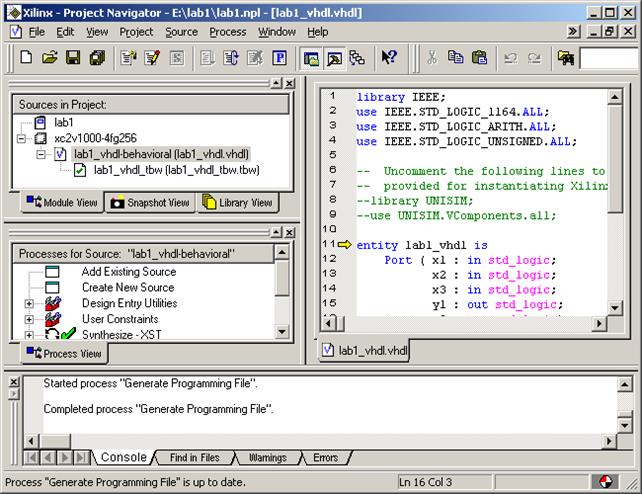

Для запуска пакета Xilinx ISE в меню Программы следует выбрать группу Xilinx ISE, в которой нужно выделить строку Project Navigator и щелкнуть на ней левой кнопкой мыши. При этом на экране монитора появится основное окно Навигатора проекта (рис. 1.5), которое содержит кроме стандартных элементов 4 встроенных окна:

– окно исходных модулей проекта (Sources in Project);

– окно необходимых процессов для выбранного исходного модуля (Processes for Source);

– окно консольных сообщений программных модулей (Console);

– окно редактора текстовых HDL‑описаний проекта.

В окне исходных модулей проекта (рис. 1.5) отображается иерархическая структура, состоящая из модулей, в которых содержится описание проектируемого устройства и описание тестовых воздействий, используемых в процессе моделирования. Каждый тип модуля имеет соответствующее графическое обозначение – пиктограмму.

Окно процессов (Processes for Source) (рис. 1.5) показывает маршрут обработки выделенного исходного модуля в процессе проектирования устройства. В данном окне подробно отображаются все этапы процесса разработки и программирования ПЛИС. Последовательность и содержание этапов определяются типом исходного модуля и серией ПЛИС.

Окно консольных сообщений (Console) (рис. 1.5) предназначено для вывода информации программных модулей пакета, работающих в консольном режиме. Здесь отображаются сообщения об ошибках и предупреждения.

Окно интегрированного текстового редактора (рис. 1.5) становится активным, если для проектируемого устройства или используемых библиотек выбран способ описания на языке HDL.

Рис. 1.5. Основное окно Навигатора проекта пакета Xilinx ISE

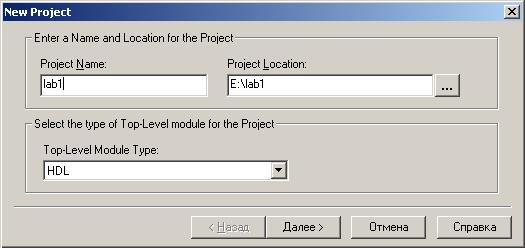

Для создания нового проекта следует выполнить команду File основного меню Навигатора проекта, а затем во всплывающем меню выбрать строку New Project. При этом появится диалоговое окно, показанное на рис. 1.6.

Рис. 1.6. Создание нового проекта в САПР Xilinx ISE 6

В открывшейся диалоговой панели (рис. 1.6) нужно определить исходные данные, необходимые для создания проекта:

– название проекта (Project Name);

– диск и каталог, в котором предполагается расположить проект (Project Location);

– тип модуля верхнего уровня (Top‑Level Module Type).

Для создания проекта на языке описания аппаратуры (в том числе на VHDL) необходимо в меню Top‑Level Module Type (см. рис. 1.6) выбрать строку HDL.

Процедура определения всех необходимых параметров создаваемого проекта завершается нажатием клавиши Далее, находящейся в нижней части панели установки параметров нового проекта (см. рис. 1.6). В результате этого на экране появляется следующее диалоговое окно (рис. 1.7).

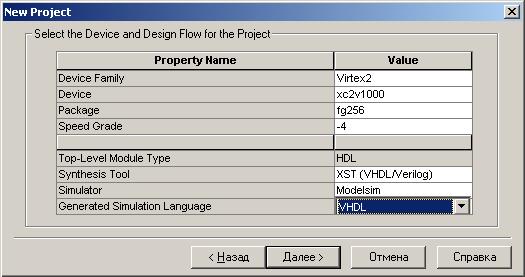

Рис. 1.7. Параметры создаваемого проекта

В окне (см. рис. 1.7) устанавливаются следующие параметры:

– серия ПЛИС, на базе которой разрабатывается устройство (Device Family);

– тип кристалла (Device), определяющий его логическую ёмкость;

– тип корпуса (Package);

– быстродействие (Speed Grade);

– средство синтеза (Synthesis Tool);

– средство моделирования (Simulator);

– язык программирования (Generated Simulation Language).

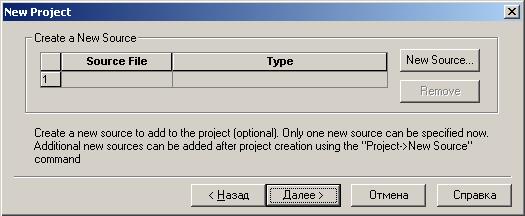

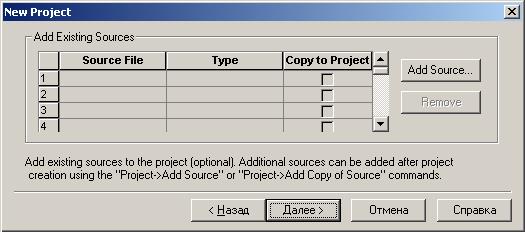

Установив соответствующие параметры проекта (см. рис. 1.7) необходимо нажать на кнопку Далее, после чего на экране появится окно (рис. 1.8) добавления новых модулей в проект при его создании. Нажав Далее появится окно (рис. 1.9) добавления существующих модулей в новый проект.

Рис. 1.8. Окно добавления новых модулей при создании проекта

Рис. 1.9. Окно добавления существующих модулей при создании проекта

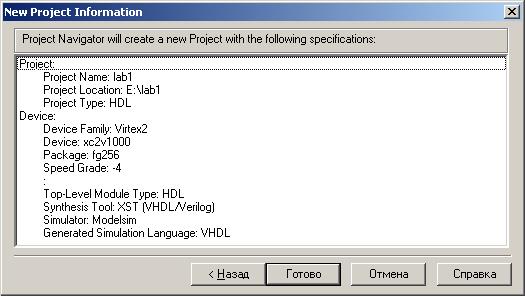

В результате нажатия в окне (см. рис. 1.9) кнопку Далее, на экране появится окно (рис. 1.10) информации о новом проекте (New Project Information). Нажав в окне (рис. 1.10) кнопку Готово, можно перейти к написанию программы.

Рис. 1.10. Окно информации о новом проекте

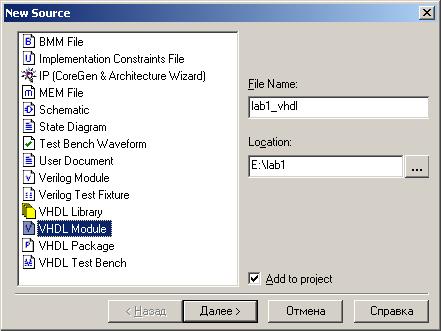

Для создания нового модуля исходного описания проекта следует выбрать команду New Source из раздела Project основного меню. В открывшейся диалоговой панели, показанной на рис. 1.11, необходимо выбрать тип нового модуля, записать его имя и указать место расположения файла на диске.

Для разработки функциональной схемы проекта следует в предложенном списке диалоговой панели выбрать тип создаваемого исходного модуля VHDL Module, щелкнув на соответствующей строке левой кнопкой мыши. Затем нужно активизировать поле редактирования названия модуля (файла) File Name и ввести текст имени с помощью клавиатуры. Расширение имени файла устанавливается автоматически в соответствии с выбранным типом модуля. Место расположения создаваемого модуля на диске указывается в поле редактирования Location диалоговой панели (рис. 1.11). По умолчанию предлагается рабочий каталог текущего проекта. Если флаг индикатора Add to project находится в установленном состоянии, то создаваемый модуль автоматически включается в состав текущего проекта. Установка значений всех необходимых параметров создаваемого модуля завершается нажатием клавиши Next (Далее), которая находится в нижней части диалоговой панели (рис. 1.11). При этом открывается информационная панель Define VHDL Source, показанная на рис. 1.12.

Рис. 1.11. Диалоговая панель установки параметров нового модуля проекта

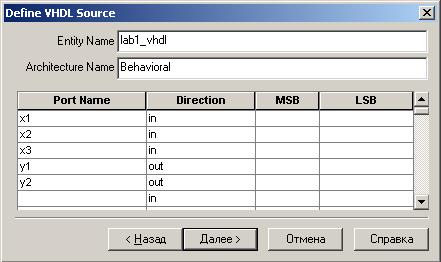

Рис. 1.12. Диалоговое окно задания сигналов ввода-вывода исходного модуля

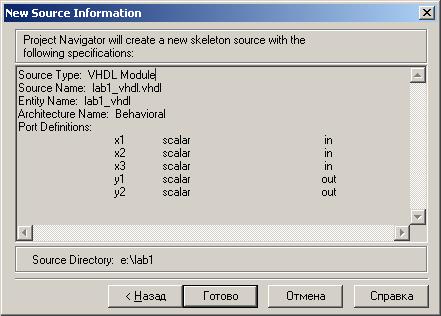

В диалоговом окне Define VHDL Source (см. рис. 1.12) задаются название модуля (поле Entity name), имя архитектуры (Architecture Name), а также входные и выходные сигналы модуля. В поле Port Name указываются названия входов и выходов, в поле Direction – их направление (in или out). Поля MSB и LSB задают разрядность многобитных сигналов (шин). На рис. 1.12 показано задание входных и выходных сигналов для ПФ в МДНФ и МКНФ. Следует отметить, что сигналы ввода-вывода в диалогом окне (см. рис. 1.12) вводить не обязательно. Их можно добавить на этапе разработки HDL‑описания. По завершении установок параметров в окне Define VHDL Source (см. рис. 1.12) следует нажать клавишу Далее. В результате этого появится окно New Source Information (рис. 1.13).

Рис. 1.13. Окно информации о новом исходном файле

Для перехода к редактированию HDL‑описания в окне (см. рис. 1.13) необходимо нажать клавишу Готово.

Разработанная программа на языке VHDL приняла вид:

library IEEE; -- Раздел описания библиотек

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity lab1_vhdl is -- Раздел объявления входных и выходных сигналов

Port (x1: in std_logic;

x2: in std_logic;

x3: in std_logic;

y1: out std_logic;

y2: out std_logic);

end lab1_vhdl;

architecture Behavioral of lab1_vhdl is -- описание переключательных функций

begin

y1 <= (x1 and x2) or ((not x1) and (not x2)) or (x2 and (not x3)); -- ПФ в виде МДНФ

y2 <= ((not x2) or x3) and ((not x1) or x2 or (not x3)); -- ПФ в виде МКНФ

end Behavioral; -- конец программы

Для запуска компиляции программы необходимо в окне Sources in Project выбрать файл *.vhd, а в окне Processes for Current Source двойным щелчком мыши запустить Synthesize. При отсутствии ошибок следует перейти к моделированию проекта.

7‑й этап. Моделирование программы в редакторе HDL Bencher.

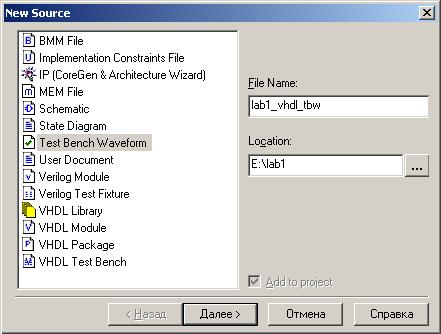

Для моделирования проекта необходимо создать тестовый вектор. Для этого следует выбрать команду New Source из раздела Project основного меню. В открывшейся диалоговой панели, показанной на рис. 1.14, необходимо выбрать тип нового модуля Test Bench Waveform, записать его имя (обычно его называют по имени vhdl-файла с добавлением суффикса _tbw на конце) и указать место расположения файла на диске.

Рис. 1.14. Диалоговая панель установки параметров тестового вектора исходного модуля проекта

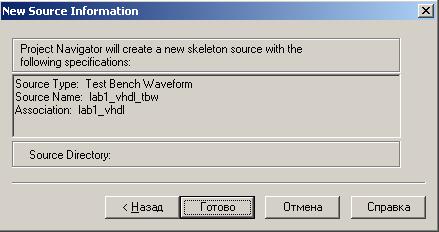

После нажатия клавиши Далее (см. рис. 1.14) появится меню (рис. 1.15), позволяющее установить взаимосвязь между тестовым вектором и vhdl‑модулем.

Рис. 1.15. Диалоговое окно установки взаимосвязи между тестовым вектором и исходным vhdl-описанием

Нажав клавишу Далее (рис. 1.15), пользователь увидит окно информации о тестовом векторе (рис. 1.16).

Рис. 1.16. Окно информации о новом тестовом векторе

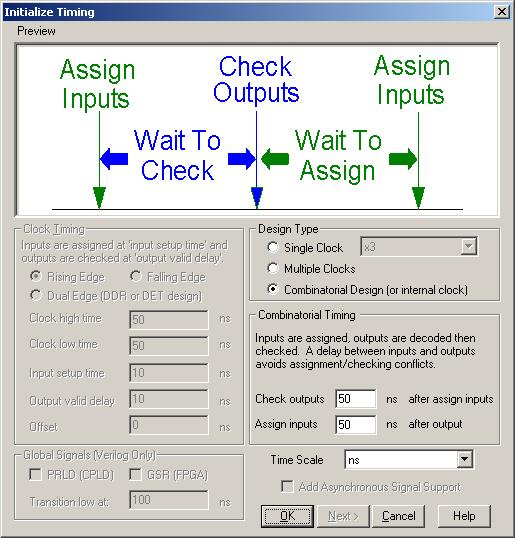

После нажатия клавиши Готово (см. рис. 1.16) появится меню временной инициализации Initialize Timing (рис. 1.17). Группа радиокнопок Design Type задает тип моделируемого проекта с точки зрения способа тактирования. Радиокнопка Single clock задает единственный сигнал тактирования. Радиокнопка Multiple clocks выбирает тактирование проекта несколькими частотными сигналами. Кнопка Combinatorial Design выбирается в случае моделирования проекта как логической схемы. Кнопки Rising Edge, Falling Edge и Dual Edge выбирают способ тактирования элементов памяти только по переднему, только по заднему, или по обоим фронтам. Поля Clock high time и Clock low time определяют длительного единичного и нулевого уровня тактовых сигналов. Поле Input setup time задает входную задержку срабатывания запоминающих элементов, а Output valid delay – выходную. Поле Time Scale задает единицу изменения времени.

Рис. 1.17. Меню временной инициализации

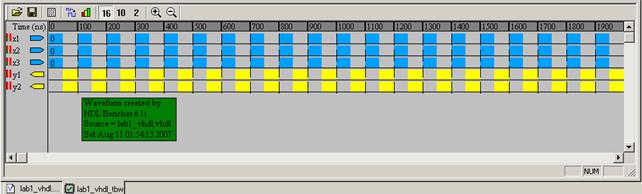

После установки всех необходимых параметров меню (см. рис. 1.17) следует нажать кнопку OK. В результате чего с целью определения входных сигналов запустится HDL Bencher (рис. 1.18). При помощи мыши и клавиатуры необходимо задать входные сигналы. При моделировании логических функций необходимо задать все наборы. Комбинация входных сигналов для функции трех переменных показана на рис. 1.19.

Рис. 1.18 Окно программы HDL Bencher

После задания значений входных сигналов тестовый вектор необходимо сохранить, нажав на пиктограмму Save Waveform, показанную на рис. 1.19 в виде дискеты. После этого необходимо закрыть тестовый вектор.

Рис. 1.19 Окно программы HDL Bencher с заданными входными сигналами

Для запуска проекта на моделирование необходимо в окне Sources in Project выбрать файл *.tbw, а в окне Processes for Source двойным щелчком мыши во вкладке ModelSim Simulator запустить Generate Expected Simulation Results. После чего на экране монитора появится окно программы HDL‑Bencher с результатами моделирования.

Результаты моделирования программы показаны на рис. 1.20.

Рис. 1.20. Результаты моделирования программы

8‑й этап. Получение конфигурационной последовательности проекта для конкретной микросхемы ПЛИС и просмотр размещения проекта внутри микросхемы в редакторе связей Floorplanner.

Для получения конфигурационной последовательности в окне Sources in Project необходимо сделать активным *.vhdl‑файл, а в окне Processes for Source запустить Generate Programming File.

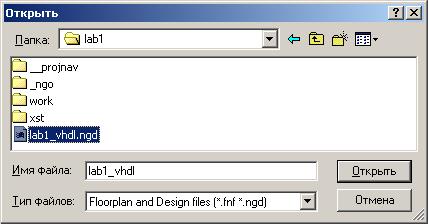

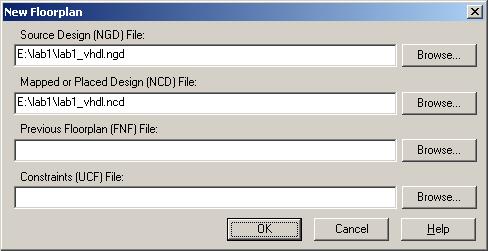

С целью просмотра размещения проекта внутри микросхемы необходимо в меню Программы выбрать вкладку Xilinx ISE 6, далее – Accessories, далее – Floorplanner. В открывшейся программе следует комбинацией клавиш Ctrl+O вызвать окно открытия файла (рис. 1.21). В этом окне следует выбрать файл с расширением *.ngd, имя которого совпадает с именем *.vhdl‑файла. После чего необходимо нажать на кнопку Открыть (рис. 1.21). В результате этого на экран появится диалоговое окно New Floorplan (рис. 1.22), на котором нужно нажать OK.

Рис. 1.21. Диалоговое окно открытия файла программы Floorplanner

Рис. 1.22. Диалоговое окно New Floorplan программы Floorplanner

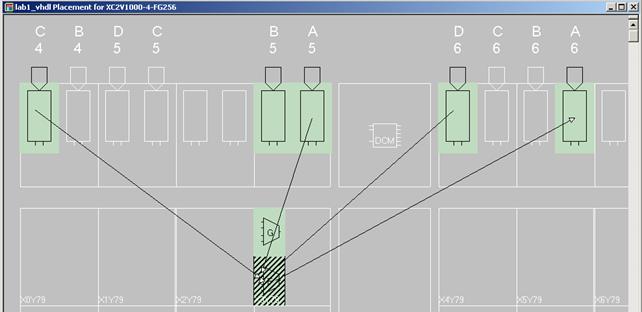

После этого откроется окно программы, показанное на рис. 1.23. В нем расположены подокна Design Hierarchy (структура проекта), Design Nets (связи проекта) и Placement (размещение). Для просмотра фрагмента топологии микросхемы необходимо в окне Design Hierarchy выбрать некоторый элемент (путем однократного нажатия на него левой клавиши мыши), затем сделать активным окно Placement и при помощи клавиш F8 (увеличить масштаб) и F7 (уменьшить масштаб) добиться желаемого уровня детализации (рис. 1.24).

На рис. 1.24 показаны 5 ножек микросхемы, 2 функциональных генератора F и G (реализующих СовДНФ и СовКНФ ПФ  ), а также связи, соединяющие функциональный генератор F с тремя входными ножками и одной выходной.

), а также связи, соединяющие функциональный генератор F с тремя входными ножками и одной выходной.

Контрольные вопросы:

1. Какие операции включает в себя маршрут проектирования цифровых устройств на базе ПЛИС фирмы Xilinx.

2. Какова структура макроса.

3. Какие существуют способы задания ПФ.

4. Что такое СовДНФ, СовКНФ, МДНФ, МКНФ.

5. Правило образования СовДНФ и СовКНФ.

6. Правило минимизации ПФ для нахождения МДНФ и МКНФ.

7. По картам Карно найти МДНФ и МКНФ ПФ 4‑х и 5‑ти переменных.

8. По таблице истинности перейти к заданию ПФ 3‑х переменных номером.

9. По заданной ПФ построить ее ЛС в универсальном базисе.

10. По заданной ПФ или ЛС написать программу на VHDL, её описывающую.

Рис. 1.23. Окно программы Floorplanner с загруженным проектом

Рис. 1.24. Фрагмент топологии микросхемы, реализующей ПФ

ЛАБОРАТОРНАЯ РАБОТА № 2

Изучение мультиплексора

Цель работы: изучение мультиплексора, способов его проектирования, построения логических схем в базисах Пирса и Шеффера, а также написание программы на языке VHDL, реализующей мультиплексор в базисах Пирса и Шеффера.

Краткие теоретические сведения. Мультиплексоры осуществляют подключение одного из входных каналов к выходному под управлением управляющего (адресующего) слова. Разрядности каналов могут быть различными, мультиплексоры для коммутации многоразрядных слов составляются из одноразрядных. Входы мультиплексора делятся на две группы: информационные и адресующие. Одноразрядный мультиплексор "2 в 1" (рис. 2.1) имеет 2 информационных входа и 1 адресный. m ‑разрядный мультиплексор "2 в 1" может быть построен на основе m одноразрядных мультиплексоров "2 в 1".

Рис. 2.1. Мультиплексор "2 в 1" одноразрядный (а) и 8‑разрядный (б)

Мультиплексор "2 в 1" может быть описан при помощи условного оператора if следующим образом:

if (s = 0)

then y = a;

else y = b.

Мультиплексор " n в 1" может быть построен как цельное устройство, или на основе нескольких мультиплексоров с меньшим числом входов. Наращивание размерности мультиплексоров возможно с помощью пирамидальной структуры из нескольких мультиплексоров. При этом первый ярус схемы представляет собой столбец, содержащий столько мультиплексоров, сколько необходимо для получения нужного числа информационных входов. Все мультиплексоры столбца адресуются одним и тем же кодом, составленным из соответствующего числа младших разрядов общего адресного кода. Старшие разряды адресного кода используются во втором ярусе, мультиплексор которого обеспечивает поочередную работу мультиплексоров первого яруса на общий выходной сигнал. Пример построения мультиплексора "4 в 1" на основе пирамидальной структуры, состоящей из мультиплексоров "2 в 1", показан на рис. 2.2.

Исходные данные: приведены в табл. 2.1.

Подготовка к работе: перед выполнением работы изучить теоретический материал по литературе и лекциям, выполнить пункты 1 – 8 задания для получения допуска к выполнению лабораторной работы.

Рис. 2.2. Мультиплексор "4 в 1", состоящий из трёх мультиплексоров "2 в 1"

Таблица 2.1. Варианты заданий для построения мультиплексора 3 в 1

| № варианта | Вид совершенной формы | Вид минимальной формы | Тип конечного базиса |

| 1, 5, 9, 13,17 | СовДНФ | МДНФ | Пирса |

| 2, 6, 10, 14, 18 | СовДНФ | МДНФ | Шеффера |

| 3, 7, 11, 15, 19 | СовКНФ | МКНФ | Пирса |

| 4, 8, 12, 16, 20 | СовКНФ | МКНФ | Шеффера |

Задание:

1) построить таблицу истинности мультиплексора "3 в 1" как цельного устройства;

2) найти СовДНФ или СовКНФ ПФ мультиплексора "3 в 1" по его таблице истинности;

3) с помощью карт Карно найти МДНФ или МКНФ ПФ мультиплексора "3 в 1";

4) перейти от МДНФ или МКНФ ПФ мультиплексора "3 в 1" к базису Пирса или Шеффера;

5) построить в универсальном базисе логическую схему мультиплексора "3 в 1" для его ПФ, заданной в виде МДНФ или МКНФ.

6) построить в базисе Пирса или Шеффера ЛС мультиплексора "3 в 1".

7) построить временные диаграммы работы мультиплексора "3 в 1";

8) написать программу, описывающую работу мультиплексора "3 в 1" в базисе Пирса или Шеффера на языке VHDL;

9) провести моделирование мультиплексора "3 в 1" в HDL Bencher;

10) получить конфигурационную последовательность проекта, реализующего мультиплексор "3 в 1" для конкретной микросхемы ПЛИС и посмотреть ее в редакторе связей Floorplanner.

Содержание отчета:

1) название, цель работы, задание;

2) проектирование схемы в соответствии с планом задания (п.п. 1 – 8 задания);

3) результаты моделирования схемы мультиплексора "3 в 1" в схемотехническом редакторе.

Пример выполнения работы.

Исходные данные: мультиплексор "2 в 1", вид совершенной формы – СовДНФ, вид минимальной формы – МДНФ, тип конечного базиса – Шеффера.

1‑й этап. Построение таблицы истинности для ПФ мультиплексора "2 в 1" (табл. 2.2).

Таблица 2.2. Таблица истинности для ПФ мультиплексора "2 в 1" ( – адресный вход,

– адресный вход,  и

и  – информационные входы,

– информационные входы,  – выходной сигнал)

– выходной сигнал)

| № набора |

|

|

|

|

2‑й этап. Нахождение СовДНФ и ПФ мультиплексора "2 в 1" по его таблице истинности (см. табл. 2.2):

СовДНФ =  . (2.1)

. (2.1)

3‑й этап. Нахождение МДНФ ПФ мультиплексора "2 в 1" с помощью карт Карно:

МДНФ =  . (2.2)

. (2.2)

4‑й этап. Переход от МДНФ ПФ мультиплексора "2 в 1" к базису Шеффера.

Для осуществления перехода от ПФ, заданной в универсальном базисе, в базис Шеффера или Пирса, необходимо воспользоваться законами де Моргана:

, (2.3)

, (2.3)

, (2.4)

, (2.4)

, (2.5)

, (2.5)

, (2.6)

, (2.6)

а также правилами перехода к базисам Пирса или Шеффера:

, (2.7)

, (2.7)

. (2.8)

. (2.8)

Применив выражение (2.4) для ПФ (2.2), получим:

. (2.9)

. (2.9)

Применив к ПФ (2.9) правило перехода к базису Шеффера (2.8), найдем:

. (2.10)

. (2.10)

5‑й и 6‑й этапы. Построение ЛС мультиплексора "2 в 1" в универсальном базисе (для ПФ (2.2)) и базисе Шеффера (для ПФ (2.10)) (рис. 2.3).

7‑й этап. Построение временных диаграмм для мультиплексора "2 в 1" (рис. 2.4).

Рис. 2.3. Логические схемы мультиплексора "2 в 1" в универсальном базисе (а) и базисе Шеффера (б)

Рис. 2.4. Временные диаграммы работы мультиплексора "2 в 1"

8‑й этап. Программа на VHDL, реализующая мультиплексор "2 в 1" в базисе Шеффера, приняла вид:

library IEEE; -- Раздел описания библиотек

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity lab2_vhdl is -- Раздел объявления входных и выходных сигналов

Port (a: in std_logic;

b: in std_logic;

s: in std_logic;

y: out std_logic);

end lab2_vhdl;

architecture Behavioral of lab2_vhdl is -- описание мультиплексора

begin

y <= (not ((not (s and b)) and (not ((not s) and a)))); -- ПФ в базисе Шеффера

end Behavioral; -- конец программы

9‑й этап. Моделирование мультиплексора "2 в 1" в HDL Bencher (рис. 2.5).

10‑й этап. Получение конфигурационной последовательности мультиплексора "2 в 1" для конкретной микросхемы ПЛИС и просмотр размещения проекта внутри микросхемы в редакторе связей Floorplanner (рис. 2.6).

На рис. 2.6 показан функциональный генератор G (реализующий ПФ мультиплексора "2 в 1"), три входные ножки (L5, K5 и L6) и одна выходная (K6).

Контрольные вопросы:

1. Каково назначение мультиплексора.

2. Построить ЛС мультиплексора " n в 1" в виде МДНФ и МКНФ.

3. Построить m ‑разрядный мультиплексор " n в 1".

4. Построить ЛС мультиплексора " n в 1" в виде пирамидальной структуры на основе заданных мультиплексоров с меньшим числом информационных входов.

5. Преобразовать заданную ПФ универсального базиса в базисы Пирса и Шеффера.

6. Построить в базисах Пирса и Шеффера ЛС заданных ПФ.

7. По заданной в базисе Пирса или Шеффера ПФ (ЛС) написать программу на языке VHDL, её описывающую.

Рис. 2.5. Результаты моделирования мультиплексора "2 в 1"

Рис. 2.6. Результаты размещения мультиплексора "2 в 1" в микросхеме XC2V40-4-CS144

ЛАБОРАТОРНАЯ РАБОТА № 3