СОДЕРЖАНИЕ

1 МИКРОПРОЦЕССОРНЫЙ КОМПЛЕКТ КР580. 4

1.1 МП ВМ80А. Структура. Основные режимы функционирования. 4

1.2 Функционирование МП.. 6

1.3 Особые режимы функционирования. 10

1.4 Непрограммируемые интерфейсные БИС.. 13

1.5 Системный контроллер ВК28. 18

1.6 Интерфейс и классификация интерфейсов. 20

1.7 Параллельный адаптер ВВ55. 20

1.8 Последовательный адаптер ВВ51А.. 23

1.9 КПДП ВТ57. Назначение. Структура. 32

1.10 КПП ВН59. Назначение. Структура. 42

1.11 Контроллер клавиатуры и индикации ВВ 79. 49

1.12 Контроллер видеотерминала КР580ВГ75. 53

1.13 Особенности МП К1821ВМ8085А.. 60

2 МИКРОКРНТРОЛЛЕР МК51. 70

2.1. Структурная схема МК51. 70

2.1.1. Арифметическо-логическое устройство. 70

2.1.2. Резидентная память. 72

2.1.3. Устройство управления и синхронизации. 75

2.2. Порты ввода/вывода информации. 77

2.3. Таймер/счетчик. 82

2.4. Последовательный интерфейс. 86

2.5. Система прерываний. 86

1 МИКРОПРОЦЕССОРНЫЙ КОМПЛЕКТ КР580

1.1 МП ВМ80А. Структура. Основные режимы функционирования

Микросхема КР580ВМ80А представляет собой 8-разрядное центральное процессорное устройство (ЦПУ) параллельной обработки данных. Устройство не обладает возможностью аппаратного наращивания разрядности обрабатываемых данных, но позволяет осуществлять это программным способом. Структурная схема КР580ВМ80А представлена на рис. 1.1. Рассмотрим назначение основных узлов и принцип их взаимодействия.

Арифметическо-логическое устройство (АЛУ) обеспечивает выполнение арифметических, логических операций и операций сдвига над двоичными данными, представленными в дополнительном коде, или над двоично-десятичными данными. Устройство содержит схему десятичной коррекции, позволяющую производить операции десятичной арифметики По результатам операций в АЛУ формируется ряд признаков, которые записываются в регистр условий. Признак переноса С устанавливается в единицу, если в результате выполнения команды появляется перенос из старшего разряда. Дополнительный признак переноса С1 устанавливается в единицу при возникновении переноса из третьего разряда. Используется в командах десятичной арифметики. Признак четности Р устанавливается в единицу, если число единиц в разрядах результата четное, Признак нуля Z устанавливается в единицу, если результат равен нулю. Признак знака S указывает знак числа и равен единице, если число отрицательное, или нулю, если число положительное.

Блок регистров производит прием, хранение и выдачу различной информации, участвующей в процессе выполнения программы, и содержит счетчик команд, указатель стека, регистры общего назначения, регистры временного хранения и регистр адреса. Шестнадцатиразрядный счетчик команд хранит текущий адрес команды. Содержимое счетчика команд автоматически увеличивается после выборки каждого байта команды. Шестнадцатиразрядный указатель стека содержит начальный адрес памяти, используемый для хранения и восстановления содержимого программно-доступных регистров ЦПУ. Содержимое указателя стека уменьшается, когда данные загружаются в стек, и увеличивается, когда данные выбираются из стека. Восьмиразрядные регистры общего назначения В, С, D, Е, Н, L могут применяться как накопители (обрабатываемые данные находятся в самом регистре) и указатели (16-разрядный адрес операнда определяется содержимым пары регистров). Регистры временного хранения W, Z используются для приема и временного запоминания второго и третьего байтов команд переходов, передаваемых с внутренней магистрали ЦПУ в счетчик команд. Эти регистры являются программно-недоступными, Шестнадцатиразрядный регистр адреса принимает и хранит в течение одного машинного цикла адрес команды или операнда и выдает его через буфер адреса на однонаправленную выходную магистраль А0 - А15. Буфер адреса выполнен в виде выходных формирователей, имеющих на выходе состояние «Выключено» (третье состояние).

Рисунок 1.1 - Структурная схема КР580ВМ80А

Схема синхронизации и управления состояниями ЦПУ формирует машинные такты и циклы, которые координируют выполнение всех команд, и вырабатывает сигнал SYNC «Синхронизация», определяющий начало каждого машинного цикла. Для исполнения команды требуется от одного до пяти машинных циклов. Каждый цикл может состоять из 3 - 5 тактов (Т1 - Т5), длительность каждого из них соответствует периоду следования тактовых импульсов Ф1, Ф2. Центральное процессорное устройство может находиться в трех состояниях (ожидание, захват и останов), продолжительность которых составляет целое число тактов и зависит от внешних управляющих сигналов.

Устройство управления формирует комплекс управляющих сигналов, организующих выполнение поступившей в ЦПУ команды, и состоит из регистра команд, программируемой логической матрицы (ПЛМ) и схемы управления узлами. Восьмиразрядный регистр команд осуществляет прием и хранение команды, поступающей по магистрали данных. Программируемая логическая матрица дешифрирует код операции команды и формирует микрооперации в соответствии с микропрограммой выполнения команды. Схема управления узлами вырабатывает для различных узлов ЦПУ необходимые управляющие сигналы, Восьмиразрядный буфер данных обеспечивает ввод команд и данных в ЦПУ, вывод данных и состояния ЦПУ через формирователи, имеющие на выходе состояние «Выключено».

Назначение выводов КР580ВМ80А приведено в табл. 1.1.

Таблица 1.1

| Номер вывода | Обозначение | Назначение |

| 25 - 27, 29 - 35, 1, 40, 37 - 39, | А0 - А 15 | Шина адреса |

| 10, 9, 8, 7, 3 - 6 | D0 - D7 | Шина данных |

| GND | Общий | |

| Ucc | -5 В | |

| RESET | Установка | |

| HOLD | Захват шин | |

| INT | Прерывание | |

| 15, 22 | Ф2, Ф1 | Фаза |

| INT A | Разрешение прерывания | |

| DBIN | Прием | |

| WR | Запись (выдача) | |

| SYNC | Синхронизация | |

| UCC2 | +5 В | |

| HLDA | Подтверждение захвата | |

| READY | Готовность | |

| WAIT | Ожидание | |

| Ucc3 | + 12 В |

1.2 Функционирование МП

Микропроцессор КР580ВМ80А может осуществлять синхронный и асинхронно-синхронный обмены информацией с памятью и внешними устройствами за один или несколько машинных циклов. Кроме того, его подсистема прерываний может инициировать асинхронно-синхронный обмен по прерыванию. При обработке большинства команд микропроцессор осуществляет обмены с памятью - извлекает код команды и операнды, засылает в память содержимое регистров и лишь только две команды IN и OUT предназначены для проведения обмена с внешними устройствами. Обмен с памятью инициируется также при начальной установке микропроцессора.

Начальная установка. При одновременном включении питания - 5, +5 и 12В (или последовательном в указанном порядке) и поступлении на микропроцессор серий тактовых импульсов F1 и F2, все регистры и флаги микропроцессора устанавливаются в произвольные состояния. При поступлении на вход RESET сигнала высокого уровня длительностью не менее 3 тактов счетчик команд PC, триггер разрешения прерывания (выход INTE), а также триггер подтверждения захвата (выход HLDA) сбрасываются, и микропроцессор начинает выборку из памяти команды, расположенной по нулевому адресу.

Микропроцессор выполняет различные команды за различное время в течение от 1 до 5 машинных циклов (M1 - М5) Первый цикл обычно состоит из 4 - 5 машинных тактов, а последующие - из 3. Таким образом, в зависимости от типа выполняемого машинного цикла микропроцессор последовательно проходит устойчивые состояния  ,

,  ,

,  (

( или

или  ,

,  для первого цикла команды), в каждом из которых он находится в течение 1 машинного такта. Кроме того, микропроцессор может находиться неограниченное время в следующих устойчивых состояниях: ожидания, захвата, останова.

для первого цикла команды), в каждом из которых он находится в течение 1 машинного такта. Кроме того, микропроцессор может находиться неограниченное время в следующих устойчивых состояниях: ожидания, захвата, останова.

В зависимости от выполняемой команды микропроцессор проходит через последовательность различных машинных циклов (табл. 1.2), о каждом из которых он посылает на шину данных в первом такте  цикла информацию - слово состояния, структура которого следующая: D0 (INTA) - подтверждение запроса на прерывание; D1 (

цикла информацию - слово состояния, структура которого следующая: D0 (INTA) - подтверждение запроса на прерывание; D1 ( ) - запись в память или вывод во внешнее устройство; D2 (STACK) - операции со стеком; D3 (HLTA) - подтверждения останова после выполнения команды HLT; D4 (OUT) - вывод; D5 (M1) - первый цикл команды; D6 (INP) - ввод; D7 (MEMR) - чтение из памяти.

) - запись в память или вывод во внешнее устройство; D2 (STACK) - операции со стеком; D3 (HLTA) - подтверждения останова после выполнения команды HLT; D4 (OUT) - вывод; D5 (M1) - первый цикл команды; D6 (INP) - ввод; D7 (MEMR) - чтение из памяти.

Таблица 1.2

| Слово состояния | M1 | M2 | M3 | M4 | M5 | M6 | M7 | M8 | M9 | M10 | |

| Извлечение команды | Чтение из памяти | Запись в память | Чтение из стека | Запись в стек | Ввод | Вывод | Подтверждение пребывания | Подтверждение останова | Подтверждение прерывания во время останова | ||

| D0 | INTA | ||||||||||

| D1 |

| ||||||||||

| D2 | STACK | ||||||||||

| D3 | HLTA | ||||||||||

| D4 | OUT | ||||||||||

| D5 | M1 | ||||||||||

| D6 | INP | ||||||||||

| D7 | MEMR |

Различают следующие циклы:  - прием первого байта (цикл извлечения команды);

- прием первого байта (цикл извлечения команды);  - чтение из ЗУ по адресу, расположенному в паре регистров (ВС, DE, HL) или счетчике команд PC;

- чтение из ЗУ по адресу, расположенному в паре регистров (ВС, DE, HL) или счетчике команд PC;  - запись в ЗУ по адресу, расположенному в паре регистров (ВС, DE, HL);

- запись в ЗУ по адресу, расположенному в паре регистров (ВС, DE, HL);

Рисунок 1.2 - временная диаграмма входных и выходных сигналов микропроцессора

- чтение из стека - области ЗУ, на которую указывает содержимое SP;

- чтение из стека - области ЗУ, на которую указывает содержимое SP;  - запись в стек - область ЗУ, на которую указывает содержимое SP;

- запись в стек - область ЗУ, на которую указывает содержимое SP;  - ввод-загрузка аккумулятора из внешнего устройства;

- ввод-загрузка аккумулятора из внешнего устройства;  - вывод-сохранение содержимого аккумулятора во внешнем устройстве;

- вывод-сохранение содержимого аккумулятора во внешнем устройстве;  - прерывание-переход на обслуживание запроса от внешнего источника;

- прерывание-переход на обслуживание запроса от внешнего источника;  - останов;

- останов;  - прерывание во время останова - переход на обслуживание запроса от внешнего источника из состояния останова. Все множество допустимых циклов микропроцессора КР580ВМ80А можно условно разбить на три группы: чтение (ввода) -

- прерывание во время останова - переход на обслуживание запроса от внешнего источника из состояния останова. Все множество допустимых циклов микропроцессора КР580ВМ80А можно условно разбить на три группы: чтение (ввода) -  ,

,  ,

,  ,

,  ,

,  ,

,  (временная диаграмма входных и выходных сигналов микропроцессора изображена на рис. 1.2, а); записи (вывода)

(временная диаграмма входных и выходных сигналов микропроцессора изображена на рис. 1.2, а); записи (вывода)  ,

,  ,

,  (рис. 1.2,б); останова

(рис. 1.2,б); останова  . В циклах группы чтения во втором такте

. В циклах группы чтения во втором такте  на выходе DBIN появляется сигнал высокого уровня, по которому микропроцессор выполняет чтение информации из памяти или внешних устройств. В циклах группы записи в такте

на выходе DBIN появляется сигнал высокого уровня, по которому микропроцессор выполняет чтение информации из памяти или внешних устройств. В циклах группы записи в такте  на выходе микропроцессора

на выходе микропроцессора  появляется сигнал отрицательной полярности, по которому происходит запись информации в память или внешние устройства. В циклах первой группы М1, М8, М10 информация с шины данных вводится в регистр команд IR, в

появляется сигнал отрицательной полярности, по которому происходит запись информации в память или внешние устройства. В циклах первой группы М1, М8, М10 информация с шины данных вводится в регистр команд IR, в  - в аккумулятор А или в один из регистров общего назначения (В, С, D, E, H, L, W, Z), в

- в аккумулятор А или в один из регистров общего назначения (В, С, D, E, H, L, W, Z), в  - в пару регистров (ВС, DE, HL или PSW), в

- в пару регистров (ВС, DE, HL или PSW), в  - в аккумулятор А. В цикле второй группы

- в аккумулятор А. В цикле второй группы  информация на шину данных выводится из аккумулятора или одного из регистров общего назначения, в

информация на шину данных выводится из аккумулятора или одного из регистров общего назначения, в  - из регистра пары (ВС, DE, HL или PSW); в

- из регистра пары (ВС, DE, HL или PSW); в  - из аккумулятора. Следует отметить, что в циклах первой группы после такта

- из аккумулятора. Следует отметить, что в циклах первой группы после такта  , в котором может завершаться чтение, могут следовать такты

, в котором может завершаться чтение, могут следовать такты  и

и  , или

, или  следующего цикла, а в циклах второй группы вслед за

следующего цикла, а в циклах второй группы вслед за  , в котором осуществляется запись, всегда следует

, в котором осуществляется запись, всегда следует  следующего цикла. При выполнении любой команды последовательность циклов обмена, инициируемая микропроцессором, начинается циклом

следующего цикла. При выполнении любой команды последовательность циклов обмена, инициируемая микропроцессором, начинается циклом  , в котором происходит извлечение кода команды.

, в котором происходит извлечение кода команды.

Цикл извлечения команды. В первом такте  по переднему фронту F2 на выходе SYNC появляется сигнал высокого уровня, индицируя первый такт машинного цикла (рис. 1.3). Кроме того, на шине данных в этом такте появляется слово состояния, у которого в разрядах D1, D5, D7 записаны единицы. По переднему фронту F2 в этом такте на адресной шине устанавливается адрес ячейки памяти, который поступил в буфер адреса из счетчика команд микропроцессора.

по переднему фронту F2 на выходе SYNC появляется сигнал высокого уровня, индицируя первый такт машинного цикла (рис. 1.3). Кроме того, на шине данных в этом такте появляется слово состояния, у которого в разрядах D1, D5, D7 записаны единицы. По переднему фронту F2 в этом такте на адресной шине устанавливается адрес ячейки памяти, который поступил в буфер адреса из счетчика команд микропроцессора.

Во втором такте  на выходе микропроцессора DBIN появляется сигнал высокого уровня длительностью в один такт, по которому обычно происходит чтение памяти и внешних устройств. В этом такте микропроцессор опрашивает сигналы на входах READY, HOLD и триггере HLTA. В зависимости от значения сигналов на этих выводах микропроцессор переходит в различные состояния: ожидания, захвата или останова. Если на выводы READY, HOLD поступили сигналы 1, 0, а триггер HLDA установлен в «0», то микропроцессор переходит в состояние

на выходе микропроцессора DBIN появляется сигнал высокого уровня длительностью в один такт, по которому обычно происходит чтение памяти и внешних устройств. В этом такте микропроцессор опрашивает сигналы на входах READY, HOLD и триггере HLTA. В зависимости от значения сигналов на этих выводах микропроцессор переходит в различные состояния: ожидания, захвата или останова. Если на выводы READY, HOLD поступили сигналы 1, 0, а триггер HLDA установлен в «0», то микропроцессор переходит в состояние  . В третьем такте может выполняться или завершаться чтение памяти, после чего шина данных переходит в высокоимпедансное состояние. Следует отметить, что обычно до четвертого такта

. В третьем такте может выполняться или завершаться чтение памяти, после чего шина данных переходит в высокоимпедансное состояние. Следует отметить, что обычно до четвертого такта  уже изменяется значение счетчика команд и, таким образом, в нем находится адрес новой команды, который поступает на адресные шины в первом такте следующего машинного цикла.

уже изменяется значение счетчика команд и, таким образом, в нем находится адрес новой команды, который поступает на адресные шины в первом такте следующего машинного цикла.

В четвертом такте  код команды, поступившей в регистр команд, дешифрируется - определяется, сколько циклов и тактов требуется для выполнения команды, которая затем отрабатывается микропроцессором в течение данного или последующего пятого такта

код команды, поступившей в регистр команд, дешифрируется - определяется, сколько циклов и тактов требуется для выполнения команды, которая затем отрабатывается микропроцессором в течение данного или последующего пятого такта  . Если команда двух- или трехбайтная, то выполнение ее происходит в следующих машинных циклах после извлечения оставшихся байтов. Следует отметить, что по переднему фронту F2 на выводах адресной шины в такте

. Если команда двух- или трехбайтная, то выполнение ее происходит в следующих машинных циклах после извлечения оставшихся байтов. Следует отметить, что по переднему фронту F2 на выводах адресной шины в такте  появляется неопределенное значение, а в такте

появляется неопределенное значение, а в такте  эти выводы переводятся в высокоимпедансное состояние.

эти выводы переводятся в высокоимпедансное состояние.

Рисунок 1.3 - Диаграмма цикла извлечения команды

1.3 Особые режимы функционирования

Если в такте  любого из циклов микропроцессора (за исключением

любого из циклов микропроцессора (за исключением  ,

,  ,

,  ) на вход READY подается сигнал низкого уровня, микропроцессор переходит в состояние «ожидание». Если на вход HOLD подается сигнал высокого уровня, микропроцессор переходит в состояние «захват». Если проверяемый в такте

) на вход READY подается сигнал низкого уровня, микропроцессор переходит в состояние «ожидание». Если на вход HOLD подается сигнал высокого уровня, микропроцессор переходит в состояние «захват». Если проверяемый в такте  внутренний триггер (HLTA) микропроцессора установлен в «1» в результате выполнения команды HLT, микропроцессор переходит в состояние останова, наступаемое после прохождения цикла

внутренний триггер (HLTA) микропроцессора установлен в «1» в результате выполнения команды HLT, микропроцессор переходит в состояние останова, наступаемое после прохождения цикла  . Если на входе INT, который проверяется в последнем цикле выполняемой команды, - сигнал высокого уровня (запрос на прерывания от внешнего устройства) микропроцессор переходит к обслуживанию подпрограмм обработки прерываний, наступаемому после прохождения цикла

. Если на входе INT, который проверяется в последнем цикле выполняемой команды, - сигнал высокого уровня (запрос на прерывания от внешнего устройства) микропроцессор переходит к обслуживанию подпрограмм обработки прерываний, наступаемому после прохождения цикла  или

или  .

.

Следует подчеркнуть, что переход в состояние «ожидание» происходит в машинном цикле между состояниями  и

и  . Переход в состояние «захват» должен выполняться в промежутках между машинными циклами. Переход к обслуживанию прерывания происходит по окончанию выполнения текущей команды, т. е. между командами.

. Переход в состояние «захват» должен выполняться в промежутках между машинными циклами. Переход к обслуживанию прерывания происходит по окончанию выполнения текущей команды, т. е. между командами.

Состояние «ожидание» предназначено для согласования работы микропроцессора с медленно действующими памятью или внешними устройствами, которые не успевают выставить данные на входы микропроцессора D0 - D7 во время действия сигнала DBIN в циклах чтения или принять их во время действия сигнала  в циклах записи. При этом внешний модуль участвует в формировании сигнала высокого уровня на входе READY микропроцессора, который после такта

в циклах записи. При этом внешний модуль участвует в формировании сигнала высокого уровня на входе READY микропроцессора, который после такта  переходит в состояние ожидания

переходит в состояние ожидания  (рис. 1.4). По каждому F2 в этом состоянии происходит опрос сигнала на входе READY. Если на нем появляется сигнал высокого уровня, то по переднему фронту F1 микропроцессор выходит из состояния ожидания и переходит в такт

(рис. 1.4). По каждому F2 в этом состоянии происходит опрос сигнала на входе READY. Если на нем появляется сигнал высокого уровня, то по переднему фронту F1 микропроцессор выходит из состояния ожидания и переходит в такт  во время которого он по сигналу DBIN принимает данные от внешнего модуля. Следует отметить, что в состоянии ожидания микропроцессор на выходе WAIT выставляет сигнал высокого уровня, а на остальных выходах сигналы не изменяются. Если микропроцессор перешел в состояние ожидания во время выполнения цикла записи (чтения), то сигнал низкого (высокого) уровня на выходе

во время которого он по сигналу DBIN принимает данные от внешнего модуля. Следует отметить, что в состоянии ожидания микропроцессор на выходе WAIT выставляет сигнал высокого уровня, а на остальных выходах сигналы не изменяются. Если микропроцессор перешел в состояние ожидания во время выполнения цикла записи (чтения), то сигнал низкого (высокого) уровня на выходе  (DBIN) поддерживается в этом состоянии.

(DBIN) поддерживается в этом состоянии.

Состояние «захват». По сигналу высокого уровня, поступающего от внешних устройств или пульта оператора на вход HOLD, микропроцессор переходит в состояние «захват». Состояние «захват» предназначено для того, чтобы внешнее устройство могло считывать или записывать информацию непосредственно в память системы, минуя микропроцессор, благодаря чему существенно повышается скорость обмена, который происходит по инициативе внешнего устройства. Такой обмен называется контроллерным. Контроллер, управляющий обменом информации между внешним устройством и памятью системы, реализует режим прямого доступа. Состояние «захват» похоже на состояние «ожидание». Сигналы на выводах микропроцессора также не изменяются, однако выводы шин данных и адреса микропроцессора в состоянии «захват» переходят в высокоимпедансное состояние, предоставляя их внешнему устройству для обмена.

Рисунок 1.4 - Диаграмма состояния «ожидания»

Переход микропроцессора в состояние «захват» осуществляется по-разному в зависимости от типа машинного цикла.

Если запрос на захват появился во время выполнения операции ввода или чтения, то по переднему фронту F1 в третьем такте на выходе HLDA появляется высокий уровень, подтверждающий состояние «захват». Выводы D0 - D7 микропроцессора в третьем такте переходят в высокоимпедансное состояние, а выводы А0 - А15 - в такте, следующем за третьим. Если выполнялся цикл извлечения команды, который состоит из четырех или пяти тактов, то микропроцессор завершает выполнение этого цикла с «отключенными» выводами D0 - D7, А0 - А15

Если выполнялась операция записи или вывода, сигнал на выходе HLDA появляется в такте, следующем за третьим. Это дает возможность микропроцессору завершить процесс записи данных перед переходом в состояние «захват». Выводы D0 - D7 и А0 - А15 также переходят в высокоимпедансное состояние в такте, следующем за третьим. При появлении низкого потенциала на входе HOLD микропроцессор по переднему фронту F1 выходит из состояния «захват» и переходит к первому такту следующего цикла.

Состояние «останов» похоже на состояние «ожидание», только оно происходит в результате выполнения команды HLT, т. е. переход в это состояние происходит программно. Из состояния «останов» можно перейти в состояние «захват» и обратно. Микропроцессор может также обслужить запрос на прерывание от внешнего устройства, однако выйти из состояния «останов», можно, только осуществив начальную установку путем отключения и включения питания или подачей сигнала с пульта управления (рис. 1.5).

Прерывания. Режим прерывания может наступить при подаче на вход INT сигнала высокого уровня. Как уже отмечалось, сигнал на этом входе проверяется в последнем цикле выполнения команды по F2. Однако запрос на прерывание может быть обслужен, если триггер прерывания микропроцессора (выход INTE) установлен в «1». Обычно этот триггер по сигналу RESET сбрасывается в "0" и запрещает прерывание. Разрешить прерывание можно программным путем по команде EI. Микропроцессор сообщает другим модулям о переходе к прерыванию словом состояния с единицами в разрядах D0, D1, D5. После перехода в режим прерывания микропроцессор выполняет команду вызова подпрограммы прерывания, поступающую по шине данных от внешних устройств (рис. 1.6). При этом счетчик команд не увеличивается на единицу, команда вызова подпрограммы должна сохранить его состояние в стеке, а после выполнения прерывания восстановить его содержимое. Для перехода к подпрограммам обработки прерывания могут использоваться команды RST или CALL.

Рисунок 1.5 - Диаграмма состояния «останов»

Рисунок 1.6 - Диаграмма прерываний

Например, при передаче на шину данных объектного кода RST101 (11110111) происходит переход по адресу 0028Н (0000000000101000). Выход из прерывания происходит по команде RET. Из всех особых состояний микропроцессора наиболее приоритетным является состояние «ожидания». Если на вход READY подается сигнал низкого уровня, то микропроцессор несмотря на наличие каких-либо других сигналов, например запроса на захват или прерывание, перейдет в состояние ожидания. Когда на вход READY подан сигнал высокого уровня, в случае если подан запрос на прерывание, запрос на захват не будет обслужен. В режиме обслуживания запроса на прерывание невозможен переход в состояние «захват» и наоборот. В состоянии «захват» запрос на прерывание обслуживаться не будет. Запросы на прерывание и захват могут быть, обслужены в состоянии «останов». В этом состоянии запрос на захват не будет удовлетворяться, если подан запрос на прерывание. После получения подтверждения прерывания микропроцессор может перейти в состояние «захват».

1.4 Непрограммируемые интерфейсные БИС

Восьмиразрядные буферные регистры (БР) КР580ИР82, КР580ИР83 используются для организации запоминающих буферов, адресных защелок, портов ввода - вывода, мультиплексоров и т. п. Буферные регистры состоят из восьми информационных триггеров (Т) с выходными схемами (SW) с тремя состояниями, общими сигналами записи информации STB и управления выходными схемами  . В буферном регистре ИР82 (рис. 1.7) к выходным схемам подключены прямые выходы информационных триггеров, в БР ИР83 (рис. 1.8) - инверсные.

. В буферном регистре ИР82 (рис. 1.7) к выходным схемам подключены прямые выходы информационных триггеров, в БР ИР83 (рис. 1.8) - инверсные.

Назначение выводов DI7 - DI0 - линии входных данных; D07 - D00 - линии выходных данных; STB - стробирующий сигнал;  - разрешение выдачи данных.

- разрешение выдачи данных.

При сигнале высокого уровня на входе STB состояние входных линий DI7 - DI0 передается на выходные линии D07 - D00. Запоминание (защелкивание) в информационных триггерах осуществляется при переходе сигнала STB от высокого уровня к низкому (по срезу сигнала STB). Сигнал  управляет выходными буферами: при

управляет выходными буферами: при  = 0 буфер отпирается, при

= 0 буфер отпирается, при  = 1 он устанавливается в Z-состояние. Сигнал

= 1 он устанавливается в Z-состояние. Сигнал  не влияет ни на состояния информационных триггеров, ни на функцию записи.

не влияет ни на состояния информационных триггеров, ни на функцию записи.

Рисунок 1.7 - Функциональная схема БР ИР82 (а) и его условное графическое обозначение (б)

Рисунок 1.8 - Функциональная схема БР ИР83 (а) и его условное графическое обозначение (б)

Малый входной ток и достаточно большой выходной позволяют использовать эти элементы в качестве развязывающих буферов-защелок либо шинных формирователей. В качестве шинных формирователей БР используют, подключая STB через резистор сопротивлением 1 кОм к шине питания (+ 5 В), а вход  - к общей шине, что делает БР «прозрачным». Временная диаграмма работы БР ИР82/83 приведена на рис. 1.9

- к общей шине, что делает БР «прозрачным». Временная диаграмма работы БР ИР82/83 приведена на рис. 1.9

Рисунок 1.9 - Временные диаграммы работы БР ИР82/83

Восьмиразрядные шинные формирователи (ШФ) КР580ВА86, КР580ВА87 применяют как буферные устройства шины данных в микропроцессорных системах. Большая выходная мощность и простота управления позволяют использовать их для построения двунаправленных согласующих буферов межмодульной связи либо как простые усилительные каскады. Полная конструктивная совместимость с БР ИР82/83 допускает взаимозаменяемость при однонаправленной передаче.

Формирователь состоит из восьми одинаковых функциональных блоков с общими сигналами управления Т и  . Функциональные блоки состоят из двух усилителей-формирователей с z-состояниями на выходах, схема включения которых обеспечивает разнонаправленную передачу. Формирователь ВА86 (рис. 1.10) не инвертирует данные, а ВА87 (рис. 1.11) инвертирует.

. Функциональные блоки состоят из двух усилителей-формирователей с z-состояниями на выходах, схема включения которых обеспечивает разнонаправленную передачу. Формирователь ВА86 (рис. 1.10) не инвертирует данные, а ВА87 (рис. 1.11) инвертирует.

Назначение выводов ШФ:

А7 - А0 - вход/выход линий данных. В зависимости от состояния входа Т они могут быть входными, если на Т - сигнал высокого уровня, и выходными, если на Т - сигнал низкого уровня.

В7 - В0 - вход/выход линий данных. Они являются входными, если на Т - сигнал низкого уровня, и выходными, если на Т - сигнал высокого уровня.

Т - входной сигнал управления направлением передачи. При Т = 0 осуществляется передача от В к А (режим В→А), при Т = 1 - от А к В. Сигнал Т выбирает верхний или нижний усилитель-формирователь, разрешая соответствующую передачу.

- входной сигнал разрешения передачи. При

- входной сигнал разрешения передачи. При  = 0 снимается z-состояние с выхода усилителя-формирователя, выбранного по входу. Т. Переход в z-состояние и наоборот не дает отрицательных выбросов на выходах ИС.

= 0 снимается z-состояние с выхода усилителя-формирователя, выбранного по входу. Т. Переход в z-состояние и наоборот не дает отрицательных выбросов на выходах ИС.

Рисунок 1.10 - Функциональная схема ШФ ВА86 (а) и его условное графическое обозначение (б)

Рисунок 1.11 - Функциональная схема ШФ ВА87 (а) и его условное графическое обозначение (6)

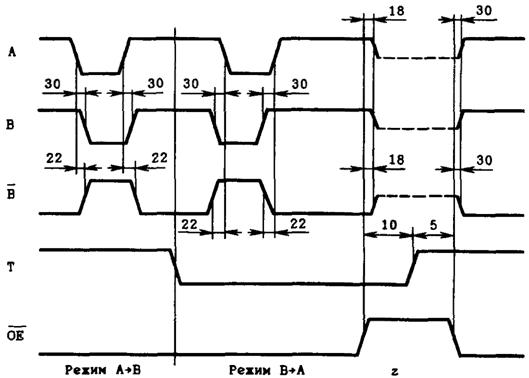

Рисунок 1.12 - Временные диаграммы работы ШФ ВА86/87

Основные достоинства ШФ: большой выходной ток при малом входном токе и отсутствие шума на выходе при переключениях. Временная диаграмма работы ШФ приведена на рис. 1.12.

1.5 Системный контроллер ВК28

Системные контроллеры КР580ВК28 и КР580ВК38

Микросхемы КР580ВК28 и КР580ВК38 выполняют функции системного контроллера и шинного формирователя, осуществляют формирование управляющих сигналов обращения к ОЗУ или к устройствам ввода/вывода (УВВ) и обеспечивают прием и передачу 8-разрядной информации между шиной данных микропроцессора и системной шиной.

Отличие микросхемы КР580ВК28 от микросхемы КР580ВК38 состоит в формировании сигналов  ,

,  . Микросхема КР580ВК28 формирует эти сигналы относительно сигнала

. Микросхема КР580ВК28 формирует эти сигналы относительно сигнала  «Запись», а микросхема КР580ВК38 - относительно сигнала

«Запись», а микросхема КР580ВК38 - относительно сигнала  «Строб состояния», что позволяет при применении в микропроцессорной системе микросхемы КР580ВК38 использовать ЗУ и УВВ с более широким диапазоном быстродействия. Структурная схема КР580ВК28 и КР580ВК38 представлена на рис. 1.13. Двунаправленный шинный формирователь осуществляет буферирование 8-разряд ной шины данных и автоматический контроль направления передачи данных. Подключение системного контроллера к шине данных микропроцессора осуществляется с помощью двунаправленных выводов D0 - D7, к системной шине - с помощью двунаправленных выводов DB0 - DB7. При необходимости с помощью сигнала

«Строб состояния», что позволяет при применении в микропроцессорной системе микросхемы КР580ВК38 использовать ЗУ и УВВ с более широким диапазоном быстродействия. Структурная схема КР580ВК28 и КР580ВК38 представлена на рис. 1.13. Двунаправленный шинный формирователь осуществляет буферирование 8-разряд ной шины данных и автоматический контроль направления передачи данных. Подключение системного контроллера к шине данных микропроцессора осуществляется с помощью двунаправленных выводов D0 - D7, к системной шине - с помощью двунаправленных выводов DB0 - DB7. При необходимости с помощью сигнала  «Управление системной шиной» выводы DB0 - DB7 системного контроллера могут быть переведены в состояние «Выключено».

«Управление системной шиной» выводы DB0 - DB7 системного контроллера могут быть переведены в состояние «Выключено».

Риcунок 1.13 - Структурная схема КР580ВК28 и КР580ВК38

Таблица 1.3

| Номер вывода | Обозначение | Назначение |

| 6, 8, 10, 12, 15 17, 19, 21 | D0-D7 | Шина данных |

| 5, 7, 9, 11, 13, 16, 18, 20 | DB0-DB7 | Системная шина |

| Строб состояния | |

| HLDA | Подтверждение захвата | |

| Запись | |

| DBIN | Прием | |

| GND | Общий | |

| Управление системной шиной | |

| Подтверждение прерывания | |

| MFMR | Чтение памяти | |

| I/OR | Чтение УВВ | |

| Запись в память | |

| Запись в УВВ | |

| Ucc | +5 В |

Регистр состояния выполнен на шести D-триггерах и предназначен для хранения информации о состоянии микропроцессора, поступающей по шине данных D0 - D7 Запись в регистр состояния осуществляется по сигналу  , поступающему в начале каждого машинного цикла.

, поступающему в начале каждого машинного цикла.

Декодирующая матрица в зависимости от режима работы микропроцессора, зафиксированного в регистре состояния, и входных управляющих сигналов HLDA,  , DBIN формирует сигнал

, DBIN формирует сигнал  «Подтверждение прерывания» или сигналы чтения/записи при обращении к ОЗУ или УВВ. Назначение выводов микросхем КР580ВК28 и КР580ВК38 приведено в табл. 1.3.

«Подтверждение прерывания» или сигналы чтения/записи при обращении к ОЗУ или УВВ. Назначение выводов микросхем КР580ВК28 и КР580ВК38 приведено в табл. 1.3.

1.6 Интерфейс и классификация интерфейсов

Интерфейсы предназначены для организации взаимодействия между микросхемами, организующими функциональные модули при построении вычислительной системы. Интерфейсы регламентируют правило взаимодействия между всеми функциональными модулями микропроцессорной системы, устанавливают взаимодействие и определяют протоколы и порядок обмена информацией.

Конфигурации интерфейсов разработаны исходя из следующих требований:

1) получение нужного быстродействия и организации стандартного обмена информацией между блоками вычислительной системы независимо от их быстродействия;

2) простота наращивания структуры многопроцессорного комплекса и возможность доступа для диагностики;

3) широкая область применения.

Электрические соединения между выводами микросхем выполняются электрическими связями или линиями. Эти линии сгруппированы по определенному функциональному назначению образуют шину адреса, шину данных и шину управления. Совокупность шин образует магистраль. В зависимости от функционального назначения интерфейсы классифицируются по следующим принципам:

- по способу создания функциональных модулей;

- по способу передачи данных - параллельный, последовательный и последовательно-параллельный;

- по режиму передачи данных - односторонние, 2-х сторонние, одновременная или поочередная передача (дуплекс или полудуплекс).

- по принципу обмена информацией - синхронный и асинхронный.

1.7 Параллельный адаптер ВВ55

Любое устройство должно быть тем или иным образом связано с внешним миром. В микропроцессорной технике эту роль выполняют периферийные адаптеры. С их помощью центральный процессор получает данные, требующие той или иной обработки, управляет различными устройствами.

Программируемый периферийный адаптер (ППА) КР580ВВ55 представляет собой три канала ввода/вывода A, B и C по 8 бит каждый. Существует три режима работы микросхемы. В режиме 0 три упомянутых канала могут быть независимо друг от друга запрограммированы на ввод или вывод информации. Режим 1 позволяет передавать информацию по каналам A и B, используя отдельные биты канала C для управления обменом данными. В режиме 2 канал A приобретает свойство двунаправленной шины, управляемой опять же отдельными битами канала C. Кроме того, возможны установка и сброс отдельных битов канала C. Микросхема выпускается в 40-выводном DIP-корпусе.

Основные особенности микросхемы:

- 3 канала ввода/вывода, 8 бит каждый;

- 3 режима работы (1 - статический ввод/вывод, 2 - тактируемый ввод/вывод, 3 - двунаправленный ввод/вывод);

- раздельное программирование каждого канала на ввод или вывод.

Структурная схема программируемого периферийного адаптера представлена на рис. 1.14.

Рисунок 1.14 - Структурная схема программируемого периферийного адаптера КР580ВВ55

ППА структурно разбит на две группы (A и B). Группа A включает в себя канал A и старшую тетраду канала C. Группа B состоит из канала B и младшей тетрады канала C. Доступ к каналам ввода/вывода и регистру управления осуществляется с помощью логики чтения-записи в соответствии с табл. 1.4.

Таблица 1.4 - Доступ к каналам ввода/вывода и регистру управляющего слова

| A1 | A0 |

|

|

Поиск по сайту©2015-2024 poisk-ru.ru

Все права принадлежать их авторам. Данный сайт не претендует на авторства, а предоставляет бесплатное использование. Дата создания страницы: 2017-12-07 Нарушение авторских прав и Нарушение персональных данных |

Поиск по сайту: Читайте также: Деталирование сборочного чертежа Когда производственнику особенно важно наличие гибких производственных мощностей? Собственные движения и пространственные скорости звезд |