Комбинационные узлы (узлы комбинационного типа) — функциональные узлы, логическое состояние выходов которых зависит только от комбинации логических сигналов на входе в данный момент времени, т.е. логическое состояние однозначно определяется комбинацией входных переменных в данный момент времени.

Сумматоры (цифровые или двоичные сумматоры)

Двоичный сумматор — логическая схема, выполняющая арифметическое сложение чисел в двоичном коде, т.е. арифметическое сложение с помощью булевых операций.

Логическое сложение — дизъюнкцию будем обозначать символом «V», а арифметическое сложение «+», + сумма по модулю 2.

Логическое сложение — дизъюнкцию будем обозначать символом «V», а арифметическое сложение «+», + сумма по модулю 2.

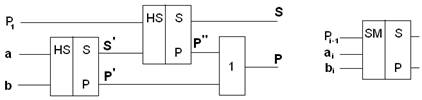

Полусумматор – схема, выполняющая сложение двух одноразрядных чисел.

Полусумматор – схема, выполняющая сложение двух одноразрядных чисел.

| a + | b | P, | S |

0 0

| |||

S – сумма в том же разряде,

P – перенос в следующий разряд,

S = a + b,

S = a + b,

P = ab.

Полный одноразрядный сумматор – схема выполняющая сложение двух одноразрядных чисел с учетом переноса из младшего разряда.

P' = ab, S'= a + b,

P' = ab, S'= a + b,

S = P-1 + a + b =

S = P-1 + a + b =

=abp + abp + abp +

=abp + abp + abp +

+abp,

P''= (a + b)P-1, P = ab v (a + b)P-1 = ab v (ab)(a v b)P-1 = ab v (a v b)P-1 =

P''= (a + b)P-1, P = ab v (a + b)P-1 = ab v (ab)(a v b)P-1 = ab v (a v b)P-1 =

= ab v aP-1 v bP-1

| P-1 | a | b | P' | S' | P'' | P | S |

|

В реальности существует много схем сумматоров, т.к. булевые выражения позволяют различные упрощения и преобразования.

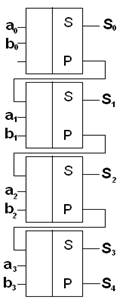

Полный многоразрядный сумматор в параллельном коде (параллельный)

|

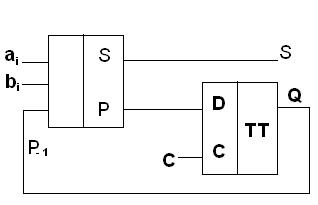

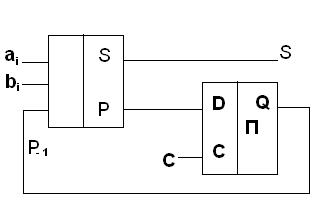

В последовательном коде (последовательный)

На вход подается ai, bi – т.е. Функция 2-х аргументов, но аргументы меняются со временем.

(a0,b0)(a1,b1)...

В схеме используется D –

триггер, задерживающий на

один такт передающуюся

через него информацию.

Компараторы (цифровые, или двоичные)

Схемы сравнения двух кодов(a0a1..am) и (b0b1...bm) и формирования признака результата сравнения в виде логической 1 на одном из выходов, если A = B, A > B, A < B и т.д.

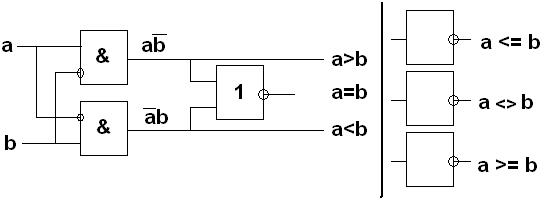

Одноразрядные компараторы – схемы сравнения одноразрядных чисел.

Полные компараторы

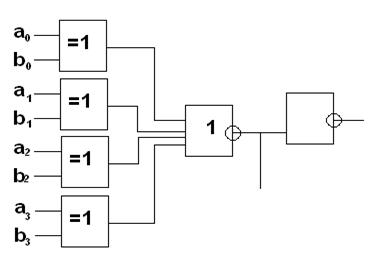

Многоразрядный компаратор

Многоразрядный компаратор

(пример компаратора, производящего сравнение равно\не равно)

| |||

|

Логическая функция многоразрядного компаратора (равно/не равно)

y = a0 + b0 v a1 + b1 v a2 + b2 v...

y = a0 + b0 v a1 + b1 v a2 + b2 v...

(a0 + b0)+(a1 + b1)+... = Σ(ai + bi), где Σ – дизъюнкция (логическая сумма)

(a0 + b0)+(a1 + b1)+... = Σ(ai + bi), где Σ – дизъюнкция (логическая сумма)

Обозначение компараторов:

В следующих схемах под двоичным кодом будем понимать любую комбинацию 0 и 1, это может быть число в двоичном виде, номер команды, устройства, адрес, выраженный двоичным числом.

Шифратор

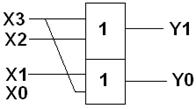

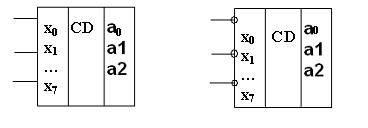

Шифратор – схема, преобразующая сигнал на одном из входов в двоичный код (номера входной линии) на выходе.

Проще: имеется несколько входов, каждому входу присваивается номер 0,1,2,... имеется несколько выходов, каждый соответствует нулевому, первому, второму,… разряду числа (номера). Логическая единица может быть подана только на одном из входов, на выходе должен быть двоичный код номера этой линии. Если выходов n, то входов может быть 2n.

Для простоты рассмотрим четырехвходовой шифратор.

| x0 | x1 | x2 | x3 | y1 | y0 |

| ||

Шифраторы могут иметь противоположную логику. Например, на всех входах 1 кроме одного, на котором 0, на выходе двоичный код номера линий, где подан 0. Тогда логическая функция: y0 = x1 + x3, y1= x2 + x3.

Шифраторы могут иметь противоположную логику. Например, на всех входах 1 кроме одного, на котором 0, на выходе двоичный код номера линий, где подан 0. Тогда логическая функция: y0 = x1 + x3, y1= x2 + x3.

Шифратор используются во многих блоках PC. Например, клавиатура: нажимается клавиша, соответственно на линии появляется 1, которая передается как двоичный код этой клавиши (преобразуется шифратором в двоичный код клавиши.)

Для восьмивходового шифратора логическая функция выглядит следующим образом:

Y0 = X1 + X3 + X5 + X7

Y1 = X2 + X3 + X6 + X7

Y2 = X4 + X5 + X6 + X7

Обозначения шифратора

Дешифратор

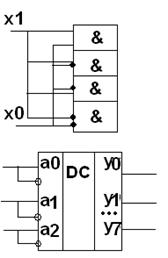

Дешифратор – схема, преобразующая параллельный код на входах в сигнал на одном из выходов.

Проще: имеется несколько входов, каждый вход соответствует двоичному разряду. Имеется несколько выходов, каждому выходу приписывается определенный номер, при подаче на вход двоичного кода на одном из выходов, чей номер соответствует поданному на вход двоичному коду, появляется логическая единица, на остальных нули. Если входов n, выходов 2n.

| x1 | x0 | y0 | y1 | y2 | y3 |

|

y0=x1x0 y0=x1x0

| ||||||

y1=x1x0 y1=x1x0

| ||||||

y2=x1x0 y2=x1x0

| ||||||

| y3=x1x0 |

Если 3 входа и 8 выходов

| x2 | x1 | x0 | y0 | y1 | y2 | … | y7 | |

| … | _ _ _ y0= x2x1x0 | |||||||

| … | _ _ y1=x2x1x0 | |||||||

| … | _ _ y2=x2x1x0 | |||||||

| и т.д. |

3.5 Мультиплексор(селектор) – MX, MS

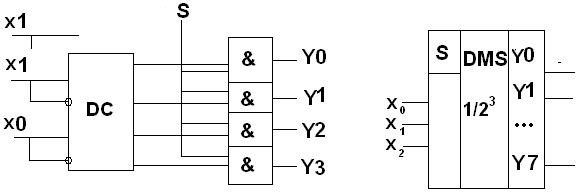

Схема, подключающая один или несколько входов к единственному выходу

Проще: имеется несколько входов (информационных), имеющий номер, несколько управляющих входов и один выход. При подаче на управляющие входы двоичного кода номера конкретного информационного входа, этот вход будет подключен к выходу, остальные отключены.

На 4 информационных и 2 управляющих входа:

y = D0x1x0 + D1x1x0 + D2x1x0 + D3x1x0

y = D0x1x0 + D1x1x0 + D2x1x0 + D3x1x0

На 8 информационных и 4 управляющих входа:

y = D0x2x1x0 + D1x2x1x0 + D2x2x1x0 + D3x2x1x0 + D4x2x1x0 + D5x2x1x0 + D6x2x1x0 + D7x2x1x0

y = D0x2x1x0 + D1x2x1x0 + D2x2x1x0 + D3x2x1x0 + D4x2x1x0 + D5x2x1x0 + D6x2x1x0 + D7x2x1x0

В общем случае k управляющих и 2k информационных входов и один выход.

Демультиплексор

Схема, подключающая единственный вход к одному или нескольким выходам.

Проще: имеется один информационный вход, несколько управляющих входов и несколько выходов имеющих свой номер. При подаче двоичного кода на управляющий вход, информационный вход будет подключен к тому выходу, чей номер совпадает с поданным двоичным кодом.

2 управляющих входа, 4 выхода: y0=Sx1x0, y1=Sx1x0, y2=Sx1x0, y3=Sx1x0.

2 управляющих входа, 4 выхода: y0=Sx1x0, y1=Sx1x0, y2=Sx1x0, y3=Sx1x0.

3 управляющих входа, 9 выходов:

3 управляющих входа, 9 выходов:

y0=Sx2x1x0, y1=Sx2x1x0, y2=Sx2x1x0, y3=Sx2x1x0, y4=Sx2x1x0, y5=Sx2x1x0 y6=Sx2x1x0, y7=Sx2x1x0.

y0=Sx2x1x0, y1=Sx2x1x0, y2=Sx2x1x0, y3=Sx2x1x0, y4=Sx2x1x0, y5=Sx2x1x0 y6=Sx2x1x0, y7=Sx2x1x0.

Иногда используется как дешифратор, а S – это разрешающий вход, при S = 1 шифратор подключается, при S=0 шифратор отключается, можно на S например подавать синхронизирующие импульсы.

Важное замечание:

Логические функции всех устройств – одинаковы для всех схем, но сами схемы могут быть и бывают различные. Здесь выбраны наиболее простые для понимания, но не для технической реализации.