Основной характеристикой комбинационных логических схем КЛС является передаточная характеристика (ПХ) – зависимость выходного напряжения от величины входного на одном из входов при неизменном напряжении на остальных входах, которое не влияет на выходное.

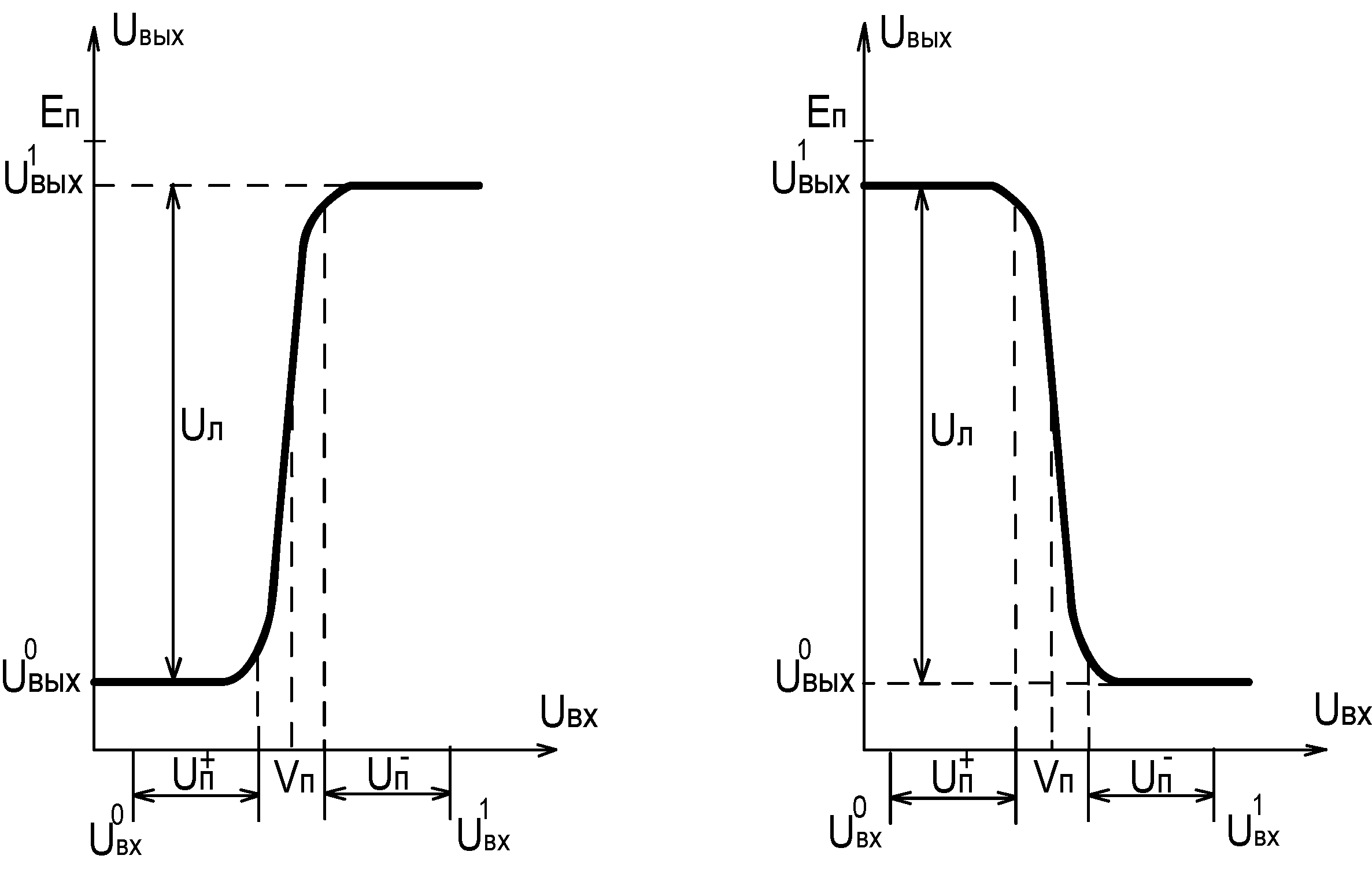

На рис.7. приведены типичные ПХ для схемы без инверсии и с инверсией.

По ПХ можно определить несколько важных параметров цифровых микросхем:

U0ВХ и U1ВХ – входные сигналы, соответствующие уровню «0» и «1»;

VП – средний порог переключения;

U+П и U-П – уровни положительной и отрицательной помехи, не приводящий к срабатыванию схемы;

U0ВЫХ и U1ВЫХ – выходные напряжения, соответствующие уровням «0» и «1»;

UЛ = U1ВЫХ - U0ВЫХ – логический перепад.

Рис.7. Переходная характеристика для схемы без инверсии (а) и с инверсией (б).

| ДШ |

| А |

| В |

Спроектировать и построить схему дешифратора 2 в 4 рис.8. Он имеет два входа А и В и четыре выхода, поэтому для проектирования можно использовать 4 двухвходовые схемы. На макете расположены схемы К561ЛА7 4(2И-НЕ) Рис.8. Дешифратор 2 в 4. и К561ЛЕ5 4(2ИЛИ-НЕ), в зависимости от заданного варианта таблицы 2 или 3 необходимо использовать одну из них.

Таблица 2.

| Вход | Вариант 1 | Вариант 2 | Вариант 3 | Вариант 4 | Вариант 5 | Вариант 6 | |||||||||||||||||||

| Выходы | Выходы | Выходы | Выходы | Выходы | Выходы | ||||||||||||||||||||

| А | В | ||||||||||||||||||||||||

Таблица 3.

| Вход | Вариант 7 | Вариант 8 | Вариант 9 | Вариант 10 | Вариант 11 | Вариант 12 | |||||||||||||||||||

| Выходы | Выходы | Выходы | Выходы | Выходы | Выходы | ||||||||||||||||||||

| А | В | ||||||||||||||||||||||||

В вариантах таблицы 2 лучше использовать схему 2ИЛИ-НЕ рис.5. В поле выходов имеется 16 точек проектирования из них четыре «1», можно проектировать или по «1» или по «0», «1» меньше. Однозначное соответствие входных и выходных сигналов в схеме 2ИЛИ-НЕ при «1» на выходе (смотри таблицу истинности рис.5.). При этом на оба входа необходимо подавать «0», но во входном коде могут быть «1», поэтому необходимо на оба входа поставить инверторы. Для вариантов по таблице 3 предпочтительно использовать схему 2И-НЕ рис.3.,т.к. эти варианты легче проектировать по «0», их меньше в поле выходов. Однозначное соответствие входных и выходных сигналов в схеме 2И-НЕ при «0» на выходе (смотри таблицу истинности рис.3.). Предварительная принципиальная схема для проектирования «болванка» приведена на рис.9. Необходимо перерисовать ее в черновик и спроектировать для своего варианта соединив входы Д2 с

_ _

точками А, А, В, В. На схеме у элементов проставить № выводов согласно условно графическому изображению микросхем рис.4 или 6. Вместо? в элементах Д2 проставить значок 1 или &.

| ГТИ |

| D1 |

| _ A |

| _ B |

| B |

| A |

| ? |

| D2 |

Рис.9. «Болванка» схемы дешифратора.

В схеме необходимо добавить связи между входами и выходами, чтобы получить на выходе «1» или «0» при коде на входах А и В соответствующего варианта. Поставить № выводов входов и выходов и тип схемы. Построить синхронные диаграммы работы дешифратора.

| А |

| В |

| t |

| t |

| t |

| t |

| t |

| t |

Рис.10. Синхронные графики работы дешифратора.

За период сигнала В происходят все возможные ситуации входных сигналов.

Изучить раздел конспекта лекций «Комбинационная логика».

Порядок выполнения лабораторной работы.

1. Построение переходной характеристики ПХ логического элемента.

По заданным вариантом параметрам построить упрощенную ПХ. Параметры даны с разбросом V±∆ и Kmin-Kmak

| Uп |

| Uвх |

| Uп |

| Uвых |

| ∆Uвых |

| ∆Uвх |

| V |

К=∆Uвых/∆Uвх

Рис.11.Пример построения упрощенной ПХ.

ПХ имеет три области: ограничение по 0, ограничение по UП и линейная

Группа 3270 UП=9 В, с инверсией.

| Вариант | |||||||||

| V±∆ В | 3.5±1 | 4±2 | 4.5±2 | 5±1.5 | 5.5±1.5 | 6±1,5 | 4±1 | 4,5±1,5 | 5±2 |

| Kmin-Kmax | 15- 50 | 20 -45 | 10- 40 | 15 - 45 | 20 - 55 | 10 – 50 | 10- 30 | 15-40 | 20-50 |

| ∆Uвых В | 0.4UП | 0.45UП | 0.5UП | 0.55UП | 0.6UП | 0.5UП | 0,45 UП | 0,4 UП | 0,5UП |

Группа 3271 UП=12 В, без инверсии.

| Вариант | |||||||||

| V±∆ В | 5±1 | 5.5±2 | 6±1.5 | 6.5±2 | 7±2.5 | 7.5±2 | 5±1,5 | 6±1 | 7±2 |

| Kmin-Kmax | 15 - 45 | 20 - 50 | 14 – 40 | 20 - 45 | 20- 55 | 10 – 50 | 15- 40 | 20- 50 | 25- 45 |

| ∆Uвых В | 0.4UП | 0.5UП | 0.55 UП | 0.6UП | 0.45UП | 0.65UП | 0,4 UП | 0,45 UП | 0,5UП |

Необходимо построить три графика ПХ. В точке с координатами (V,∆Uвых) проводим прямую с наклоном соответствующим Кмак, а в точках с координатами (V±∆,∆Uвых) проводим прямые с наклоном соответствующим Кмин.

2. Разработать схему дешифратора по таблице истинности и нарисовать синхронные диаграммы работы.

Группа 3270.

| Вариант | ||||||

| № таб.2,3 |

Группа 3271.

| Вариант | ||||||

| № таб.2,3 |

Отчет оформляется на листах А4 в рукописном или компьютерном исполнении. Отчет должен содержать титульный лист, цель работы, данные варианта, схемы, формулы, расчеты, графики, вывод о проделанной работе.

ЛАБОРАТОРНАЯ РАБОТА № 9.

“ИЗУЧЕНИЕ СЧЕТЧИКОВ НА МИКРОСХЕМАХ СЕРИИ 561.”

Цель работы: Изучение принципов построения, структуры и способов включения разных типов счетчиков.

ОСНОВНАЯ ЧАСТЬ.

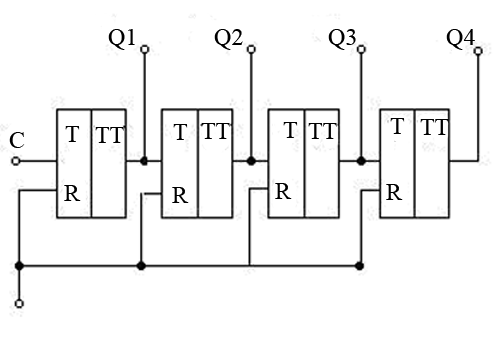

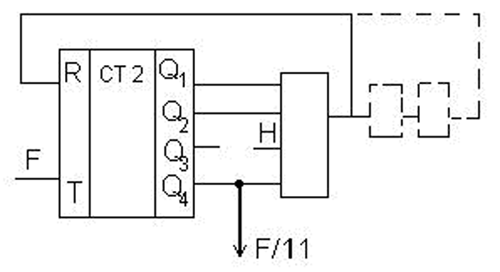

Цифровой счетчик - электронное устройство, состоящее из триггеров и производящее счет импульсов поступающих на вход. Количество импульсов отображается двоичным кодом на выходе счетчика. Основным параметром счетчика является модуль счета Ксч – максимальное число входных импульсов, которое может сосчитать счетчик, после чего возвращается в исходное состояние. Ксч - зависит от разрядности счетчика, т.е. количества триггеров, входящих в счетчик. Каждый триггер содержит информацию о значении соответствующего ему разряда двоичного числа или выходного кода. По структурной организации счетчики делятся на последовательные, параллельные и параллельно - последовательные. В переводной а иногда в отечественной литературе последовательные счетчики называют асинхронными, а параллельные синхронными. В последовательном счетчике триггеры соединены последовательно, так что каждый последующий триггер (разряд) срабатывает после переключения предыдущего. Входная последовательность подается только на первый триггер. Ксч = 2m, где m количество триггеров в счетчике (рис.1.).

Рис.1. Схема 4Х разрядного последовательного счетчика.

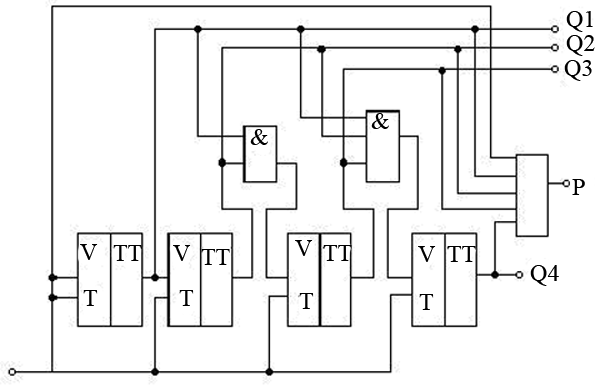

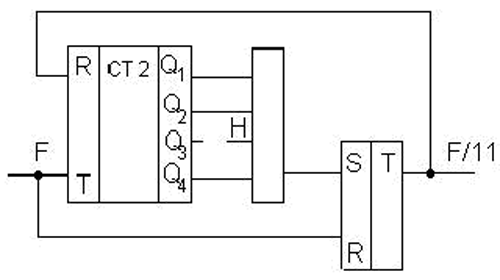

У последовательных счетчиков низкое быстродействие, т.к. mй разряд срабатывает только через время tm = m*tср.т после подачи входного импульса, где tср.т - время задержки срабатывания триггера. В моменты переключения возможны неправильные показания счетчика, это необходимо учитывать при проектировании систем на последовательных счетчиках. В параллельном счетчике входной сигнал подается на все триггеры счетчика одновременно, поэтому все разряды которые должны сработать, срабатывают одновременно (рис.2.).

Рис.2. Схема 4Х разрядного параллельного счетчика.

Разрешение на переключение задает элемент И на входе каждого разряда. Триггер разряда переключается при наличии "I" на всех предыдущих разрядах. Синхронные счетчики имеют большее быстродействие, чем асинхронные. При наличии "I" на выходе всех триггеров формируется сигнал переноса Р. Ксч = 2m.

Разновидностью параллельных счетчиков являются счетчики на регистрах сдвига с обратной связью (рис.3.). У такого счетчика Ксч = 2m. При подаче входных импульсов разряды счетчика последовательно, начиная с первого, заполняются "I", а после m входных импульсов заполняется "0", после 2m входных импульсов цикл повторяется. Код на выходе такого счетчика соответствует коду Джонсона (рис.3.) в зависимости от количества входных импульсов.

Рис.3. Схема 4Х разрядного кольцевого счетчика.

Счетчики могут быть суммирующие, вычитающие и реверсивные. В суммирующих при каждом импульсе на входе выходной код увеличивается на единицу, в вычитающих уменьшается на единицу. Реверсивный может работать в режимах прямого и обратного счета. Некоторые счетчики могут работать либо как двоичные, или как двоично - десятичные (Ксч = 10). Частота сигнала на выходе последнего разряда счетчика в Ксч раз меньше частоты входного сигнала fвых = fвх/Ксч или Твых = Ксч*Твх. Счетчик делит входную частоту в Ксч раз.

Делитель электронное устройство, имеющее частоту выходной последовательности в Кд раз меньше, чем частота на входе. Делители формируют на основе двоичных счетчиков, они имеют один вход и один выход. Рассмотрим два способа

А) С использованием схемы И (рис.4.). К входам схемы И

подсоединяются те разряды счетчика, на которых будет "I" при достижении выходным кодом числа Кд. Например: Кд = Ксч = 11, выходной код 1011 с входами схемы И соединяются первый, второй и четвертый разряды счетчика (рис.4.). Выход схемы И соединяется со входом обнуления R счетчика. При достижении на выходе счетчика кода 1011 на выходе схемы И появится "I" и обнулит счетчик. Цикл счета до 11 повторится. Выходное напряжение можно снимать с выхода 4-го разряда или с выхода схемы И. Необходимо отметить, что в этой схеме длительность импульса обнуления будет равна времени задержки срабатывания схемы И (tз.ср) очень мало, что может привести к сбоям в работе делителя. Поэтому иногда ставят в цепь обнуления последовательно несколько (n) элементов типа повторитель или инвертор, тогда время обнуления t0 = tз.ср * n. Можно применить схему на рис.4.б. с дополнительным триггером, делающую t0 = Твх.

Рис.4. Схемы делителей со схемой И.

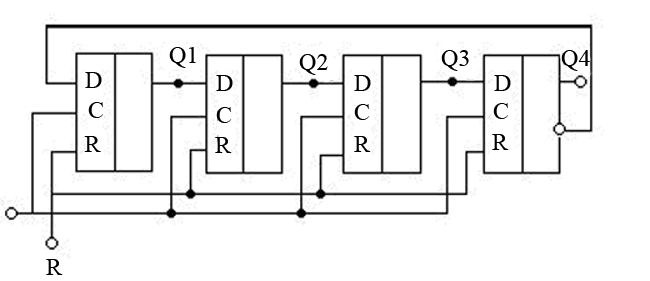

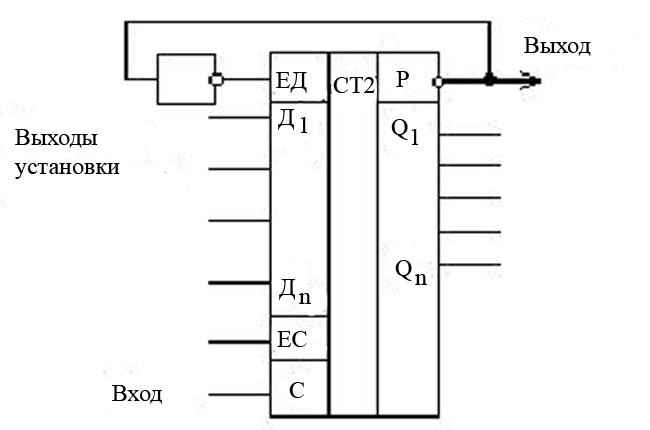

Б) Делитель с предварительной установкой исходного состояния (рис.5.). В таких счетчиках имеются входы предварительной установки Д1 - Дn код с которых переписывается в счетчик при подаче на вход записи ЕД "I". Когда на входе ЕД низкий уровень "0" или L счетчик работает в счетном режиме до заполнения всех разрядов единицами. В этот момент на выходе переноса Р появляется L, а после инвертора

Рис.5. Схема делителя с предустановкой.

на ЕД высокий уровень (Н), происходит перезапись входного кода. Чтобы делил на КД необходимо установить входной код 2m -КД для суммирующего счетчика. Вычитающий счетчик требует входной код равный КД, после записи которого и перехода счетчика в счетный режим выходной код его будет уменьшаться до "0" во всех разрядах при этом на выходе переноса возникает уровень "0"(L), что приводит к записи входного кода и повторению цикла счета. Выходом делителя является выход переноса Р. В данной работе исследуются три счетчика из серии К561. Эта серия является функционально полной серией, т.е. на элементах, входящих в нее можно построить практически любое цифровое устройство. Серия К561 изготовляется по КМОП технологии, поэтому имеет малое статическое потребление, высокую помехоустойчивость, логический "0" - нулевое напряжение, логическая "I" напряжение питания Uп, при максимальной частоте переключений 2МГц. Дальнейшее развитие КМОП технологии серия К1554 имеет частоту переключения 100 МГц. Напряжение питания микросхем серии К561 может выбираться от 3 до 18 вольт.

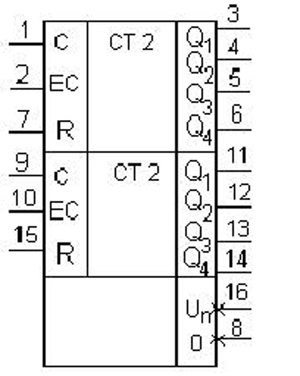

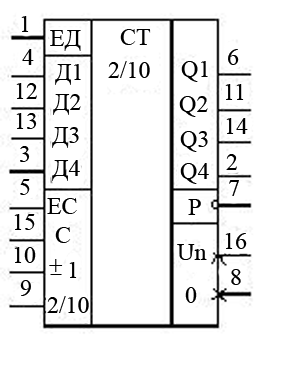

Микросхема К561 ИЕ10. Содержит два синхронных четырех разрядных двоичных счетчика (рис.6.).

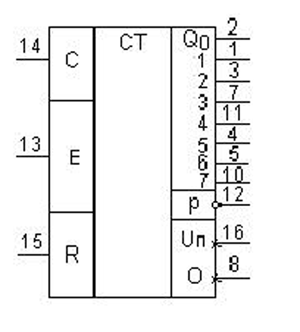

К561ИЕ10 К561ИЕ14 К561ИЕ9

Рис.6.Условно графическое изображение счетчиков.

Каждый счетчик состоит из 4-х Д триггеров. Входы С и ЕС (такт и разрешение такта) взаимозаменяемы и отличаются противоположными активными уровнями. Если на С подается входная последовательность, то на ЕС необходимо подавать высокий уровень Н (это "I" иначе Uп), тогда каждое приращение выходного кода будет происходить синхронно с положительным перепадом входного сигнала (переход от "0" к "I" или от L к Н или Г). При низком уровне L на входе ЕС входная тактовая частота не проходит на триггеры и выходной код не меняется, т.е. вход ЕС можно использовать для стробирования входной последовательности. Если входную тактовую частоту подавать на вход ЕС, то стробирование будет по входу С, причем активным будет низкий уровень. При этом изменение выходного кода будет синхронно с отрицательным Г фронтом напряжения на входе ЕС. При подаче уровня Н на вход сброса R, выходы всех триггеров принимают уровень L (обнуляются). В таблице 1 приведены логические состояния и импульсные переходы счетчика К561ИЕ10. Оба счетчика микросхемы могут работать параллельно или их можно каскадировать включать последовательно. Для этого выход Q3 первого счетчика следует соединить со входом ЕС последующего, подав на его тактовый вход С уровень L. При этом получается восьми разрядный асинхронный счетчик. Микросхема К561ИЕ14 - четырехразрядный синхронный реверсивный счетчик (рис. 6). Может работать как двоичный или как десятичный, на вход 2/10 в первом случае подается уровень Н, для десятичного счета уровень L. Входная последовательность импульсов подается на вход С. Вход ЕС (запрет такта или вход переноса) или L уровне позволяет входной последовательности проходить на счетчик, при уровне Н на входе ЕС счета не происходит. Для изменения модуля счета используются входы предварительной установки Д1-Д4 и вход разрешения записи ЕД. При подаче Н уровня на вход ЕД код, присутствующий на входах Д1-Д4 переписывается в соответствующие разряды счетчика Q1-Q4. Если на входах Д1-Д4 присутствует L уровень ("0"), то вход ЕД будет выполнять роль R входа. Если на входах ЕС и ЕД уровень L (счетный режим), то при каждом положительном перепаде напряжения на входе С код на выходе счетчика будет меняться на единицу в зависимости от напряжения на входе Больше/Меньше (+1/-1). При Н уровне счетчик увеличивает код и уменьшает если уровень L. Выход переноса Р имеет Н уровень, но переключается в L уровень когда в режиме +1 код достигает максимального значения (1111) или в режиме -1 выходной код становится минимальным (0000). Счетчики К561ИЕ14 можно включать синхронно: входы С объединяются, вход переноса Р предыдущего соединения со входом переноса ЕС последующего или асинхронно: выход переноса Р предыдущего соединения со входом С последующего, а на вход ЕС последующего подается L уровень. Логические состояния и импульсные переходы счетчика приведены в таблице 2. Микросхема К561ИЕ9 счетчик делитель на 8 (рис.6.). Интегральная схема ИС имеет в основе высокоскоростной синхронный счетчик Джонсона на четырех триггерах. При L уровне на выходе Е (разрешение счета) счетчик меняет код синхронно с положительным фронтом (перепадом) входных импульсов по входу С (тактовый). При Н уровне на входе Е счет прекращается. Внутренний дешифратор переводит состояние триггеров в восемь выходных сигналов от 0 до 7. Высокий Н уровень присутствует только на одном из этих выходов в зависимости от количества входных импульсов. В процессе работы счетчика на выходе переноса Р формируется последовательность импульсов со скважностью Q = 2 и частотой, равной fвх/8. При высоком уровне на входе сброса R на выходах Q0 и Р появляются уровни Н, на других выходах Q1-Q7 уровень L. Положительные фронты импульсов выхода переноса Р используются как тактовая последовательность для последующего счетчика ИЕ9. Таким образом двухкаскадное соединение получается асинхронным. Логические состояния и импульсные переходы счетчика К561ИЕ9 сведены в таблицу 3. На рис. 8 приведены функциональные схемы приведенных выше счетчиков. Для подготовки к работе необходимо составить схемы включения счетчика К561ИЕ10 для работы от положительного и от отрицательного фронта входного сигнала. Составить схемы делителей на ИС К561ИЕ10 и К561ИЕ14 с заданным Кд. Осциллограммы (заготовки) к пунктам 1 и 2.