ПРАКТИЧЕСКАЯ РАБОТА

«Проектирование ФАПЧ на ПЛИС»

Выполнил:

Студент группы

Глумова Е.С.

Проверил:

Чернышев С.А.

г. Нижний Новгород

2017 г.

Назначение ФАПЧ (PLL)

ФАПЧ (PLL - Phase-Locked Loop) ̶ это специальный генератор со схемой подстройки частоты, управляемый напряжением ̶ ГУН (VCO - voltage-controlled oscillator). В генераторе реализовано сравнение фаз сигнала входной частоты и сигнала выходной частоты. Измеренная разность фаз этих частот через отрицательную обратную связь как раз и управляет частотой генератора, фиксируя её на заданном значении.

PLL широко используются при телекоммуникации, в компьютерах и других электронных устройствах.

Принцип действия ФАПЧ (PLL)

На вход PLL подаётся некоторая входная частота опорного генератора Fin. Далее на счётчике N-counter опорная частота делится и получается другая частота Fref, которая поступает на фазовый детектор PFD (phase-frequency detector).

Фазовый детектор сравнивает фазы частот Fref и той, что поступает с делителя M-counter. Разность фаз, фильтруется и управляет генератором VCO.

На выходе управляемого генератора получается новая частота Fvco. Фазовый детектор подаёт управляющее воздействие на генератор VCO до тех пор, пока не выполнится условие Fref = Fvco / M. При этом условии частоты, подаваемые на детектор фаз равны. Таким образом, например, если M=2, то частота генератора VCO должна получиться в 2 раза выше частоты Fref. Последний этап ̶ деление частоты Fvco на выходном счетчике K-counter. Подбирая коэффициенты N, M, K, можно синтезировать довольно большой диапазон частот. Более сложные компоненты PLL позволяют перезагружать коэффициенты в процессе работы системы.

Исходное задание: спроектировать ФАПЧ на ПЛИС со следующими параметрами

Входная частота: Fin=160 МГц

Выходные частоты: 1. Fout1=3/8Fin

2. Fout2=3/2Fin

Проектирование в среде Quartus II

Для проектирования ФАПЧ на ПЛИС используем среду программирования Quartus II.

Запускаем Quartus Prime Lite Edition:

Для запуска советника-генератора IP-ядер для создания проектного экземпляра ФАПЧ в среде Quartus в правом углу выбираем Device Family: Arria II GX. Далее выполняем следующую последовательность: Installed IP → Library → Basic Functions → Clocks; PLLs and Resets → PLL→ Altera PLL.

Запускается MegaWizard Plug-In Manager, где производится установка параметров системы ФАПЧ.

1) Выставляем входную частоту 160 МГц.

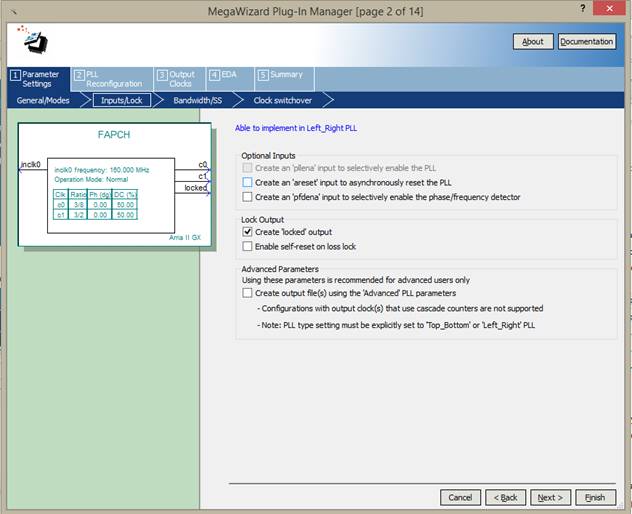

2) Убираем такие лишние настройки, как сброс PLL areset и разрешение работы PLL pfdena на входе ФАПЧ.

Устанавливаем сигнал, сообщающий о захвате частоты, ̶ locked на выходе ФАПЧ.

Принимаем решение об этих сигналах и нажимаем Next.

Пропускаем настройки Spread Spectrum ̶ о возможности девиации частоты на выходе PLL. Так же поступаем с ClockSwitchover ̶ возможностью подключить вторую входную частоту и пока пропускаем Dynamic Reconfiguration.

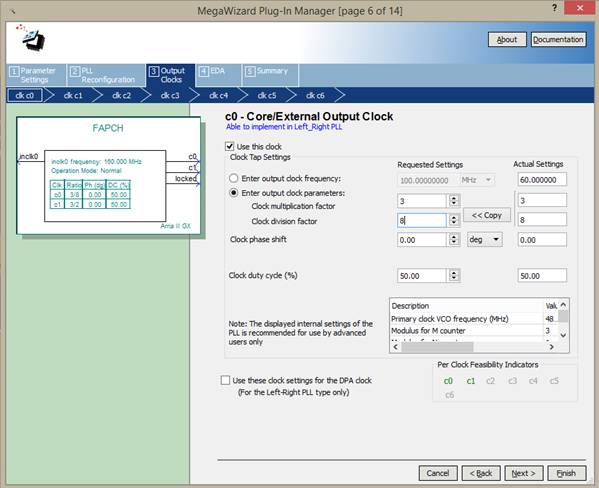

3) Переходим к настройкам коэффициентов умножения и деления исходной частоты для получения нужных частот на выходе. Это можно сделать вручную, а можно задать желаемую частоту, тогда Quartus II Wizard сам рассчитает коэффициенты, которые потом нужно скопировать.

Cyclone IV PLL может иметь 5 выходов: C0, C1, C2, C3, C4. Каждый из выходов может быть самостоятельно сконфигурирован на заданную частоту. Правда, частоты получатся более или менее связанными.

Для каждого выхода PLL будет соответствующая страница Wizard с настройками.

В нашем случае имеем 2 выхода с фиксированными частотами. Зададим коэффициенты умножения и деления входной частоты. Для C0 это будет 3/8, а для С1 ̶ 3/2. Quartus II Wizard сам рассчитает частоты на выходе, которые должны получиться.

4) Далее переходим к настройками Summary, где выбираем необходимые в процессе проектирования файлы нужного формата

Описанные действия отражают приведённые ниже скриншоты.

1)

1)

2)

2)

3.1)

3.1)

3.2)

4)

4)

Таким образом, мы получаем некоторые сгенерированные файлы.

Файл с расширениями *.bsf ̶ это компонент, который можно вставить в схему, если проект выполнятся в схематическом виде. Файл вида*.v ̶ это модуль Verilog, экземпляры которого можно вставлять в свои модули Verilog.

Далее создаём проект формата *.bdf (Block Diagram/Schematic File) ̶ «тело» схемы, где физически осуществляется подключение входов и выходов системы.

Далее создаём проект формата *.bdf (Block Diagram/Schematic File) ̶ «тело» схемы, где физически осуществляется подключение входов и выходов системы.

Создаём файл дизайна HDL для синтезированной блок-схемы (этот формат был выбран при настройке блока ФАПЧ), также этот формат был указан в выборе расширения файлов для программы симуляции (в нашем случае ModelSim) при создании проекта.

Присваиваем компоненту fapch.v Top-level.

Выполним синтез проекта, выбрав Processing→ Start → Start Analysis & Synthesis.

Чтобы избежать ошибок при моделировании, проверим проект и на другие процессы.

Запустим сборщик проекта Fitter в той же вкладке Processing→ Start→ StartFitter.

Затем выполним синхронизацию проекта по времени, запустив Processing → Start→ StartTimeQuest Timing Analyzer.

После чего переходим к проверке списков соединений. Открываем Processing → Start → Start EDA Netlist Writer.

Данные действия позволяют выявить ошибки до моделирования проекта. На этом этапе производится налаживание связи между Quartus и ModelSim, генерация TestBench и его привязка к проекту.

Если приведённые операции не выдали ошибок, то можно смело переходить к моделированию системы ФАПЧ в среде ModelSim.

ModelSim запускается через вкладку Tools →Run Simulation Tool→Gate Level Simulation…