Лабораторная работа 2

Тема: Исследование двоичных сумматоров

Цель работы

Исследование внутренней структуры и логики функционирования сумматоров и полусумматоров; проверка правильности их функционирования.

Краткая теория к заданию

По числу входов различают полусумматоры, одноразрядные сумматоры (ОС) и многоразрядные сумматоры.

Полусумматорами называются устройства с двумя входами и двумя выходами, на которых вырабатываются сигналы суммы и переноса. Полусумматор реализует лишь часть задачи суммирования, так как не учитывает входной величины – переноса из соседнего младшего разряда в данных. В таблице 1 приведена таблица истинности полусумматора.

Таблица 1 – Таблица истинности полусумматора

| Ai | Bi | Si | Pi |

Одноразрядный двоичный сумматор состоит из двух комбинационных схем: одна – для формирования Si, вторая – для определения Pi.

Многоразрядный сумматор строится на основе одноразрядных в соответствии с правилами сложения. В зависимости от характера ввода-вывода кодов и организации переносов многоразрядные сумматоры бывают последовательного и параллельного принципа действия.

Одноразрядные сумматоры имеют три входа и обеспечивают сложение разрядов слагаемых с переносом из предыдущего разряда. В таблице 2 приведена таблица истинности сумматора.

Таблица 2 – Таблица истинности сумматора

| Ai | Bi | Пi-1 | Сi | Пi |

Обозначения в таблице 2:

· Ai, Bi – слагаемые i-го разряда;

· Сi – сумма слагаемых i-го разряда;

· Пi-1, Пi – переносы из (i‑1)-го и i-го разрядов.

Арифметические сумматоры являются составной частью так называемых арифметико-логических устройств (АЛУ) микропроцессоров (МП). Они используются также для формирования физического адреса ячеек памяти в МП с сегментной организацией памяти.

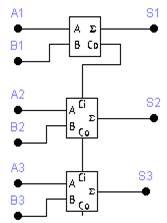

В программе ЕWВ арифметические сумматоры представлены в двумя базовыми устройствами, показанными на рис. 1: полусумматором (слева) и полным сумматором (справа).

Рисунок 1 – Устройства полусумматора и сумматора

Они имеют следующие назначения выводов:

А, В – входы слагаемых,

∑ – результат суммирования,

Со – выход переноса,

Сi – вход переноса.

Многоразрядный сумматор создается на базе одного полусумматора и n полных сумматоров.

|

В качестве примера на рис. 2 приведена структура трехразрядного сумматора. На входы А1, А2, АЗ и В1, В2, ВЗ подаются первое и второе слагаемые соответственно, а с выходов S1, S2, S3 снимается результат суммирования.

Рисунок 2 – Трёхразрядный сумматор

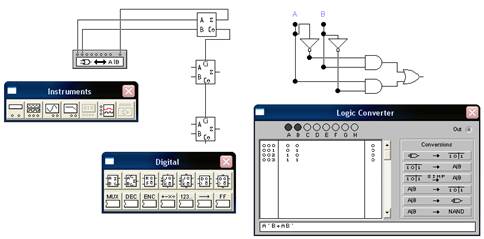

Для исследования внутренней структуры и логики функционирования сумматоров как нельзя лучше подходит логический преобразователь.

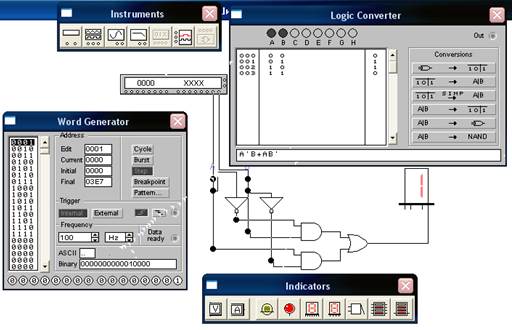

Схема подключения полусумматора к логическому преобразователю приведена на рис. 3.

Рисунок 3 – Подключение полусумматора к логическому конвертеру

|

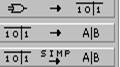

После подключения полусумматора к преобразователю последовательно нажимаем кнопки (рис. 4) и в результате получаем таблицу истинности и логическое выражение.

Рисунок 4 – Кнопки логического конвертера

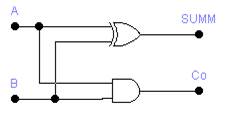

Из полученной таблицы истинности можно видеть, что при подключении вывода ∑ полусумматора к зажиму ОUТ преобразователя он выполняет функции элемента «Исключающее ИЛИ». Подключив клемму ОUT преобразователя к выходу Со полусумматора и проделав аналогичные действия, приходим к выводу, что в таком включении полусумматор выполняет функции элемента И. Следовательно, эквивалентная схема полусумматора имеет вид, показанный на рис. 5.

Рисунок 5 – Эквивалентная схема полусумматора

Практическая часть

1. Подключим полный сумматор к логическому преобразователю, как указано на рис. 6, и выясним его внутреннюю структуру, принимая во внимание методику решения аналогичной задачи для полусумматора.

Рисунок 6 – Исследование полного сумматора

2. Используя опыт работы со схемой на рис. 8, подключим ко входам трехразрядного сумматора на рис. 2 генератор слова, а к выходам алфавитно-цифровой индикатор с дешифратором и проверим правильность его функционирования.

Рисунок 7 – Подключение семисегментного индикатора с дешифратором

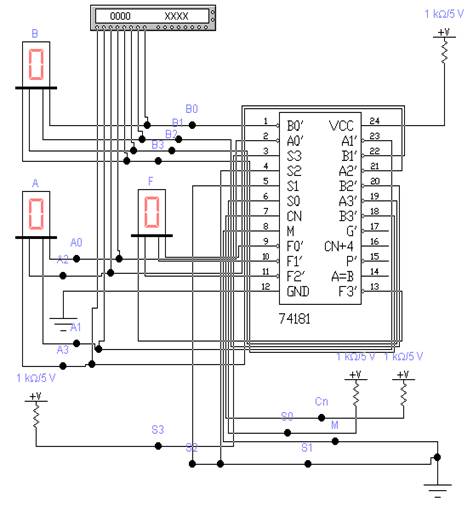

В каталоге программы ЕWВ имеется схема включения четырехразрядного АЛУ на базе серийной микросхемы 74181 (отечественный аналог К155ИПЗ.

Проверим работу ИМС 74181 (рис. 8) в режиме сумматора с переносом (на вход Сn подаём сигнал логического нуля).

ИМС74181 обеспечивает 32 режима работы АЛУ в зависимости от состояния управляющих сигналов на входах М, S0...S3, а также допускает наращивание разрядности (вход СN и выход СN<4 для переносов).

Показанная на рис. 8 схема включения ИМС соответствует режиму сумматора без переноса. Значения четырехразрядных операндов А и В на входе задаются с помощью генератора слова и в шестнадцатеричном коде отображаются одноимёнными алфавитно-цифровыми индикаторами. На выходах F0...F3 результат суммирования отображается индикатором F. Изменяя состояния сигналов на управляющих входах, можно промоделировать большинство функций АЛУ, используемых в микропроцессорах.

Рисунок 8 – Подключение микросхемы ИМС74181 в режиме сумматора без переноса

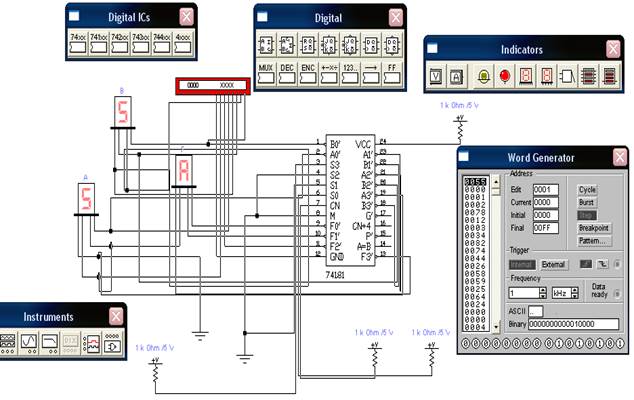

4.В соответствии с рис. 8 соберем ИМС 74181. В генераторе слов вводим любые комбинации десятичного системы счисления. (рис. 9).

Рисунок 9 – Ввод комбинаций

Вывод: При выполнении лабораторной работы мы изучили принцип работы, внутреннюю структуру и логику функционирования сумматоров и полусумматоров, удостоверились в правильности функционировании ИМС 74181 в режиме сумматора с переносом (на вход Сn подали сигнал логического нуля).

Контрольные вопросы и задания

1. Чем отличается полусумматор от одноразрядного сумматора?

2. Сколько входов имеет полный сумматор? Сколько выходов?

3. Запишите функцию алгебры логики, которая реализует арифметическое суммирование одноразрядных двоичных чисел.