Digital Integrated Circuits

Lab9: Изучение схем на динамической логике

Цель

Изучение свойств CMOS NAND и NOR логических ячеек, их характеристик и параметров с помощью программы – инструмента для моделирования схем HSPICE и оценка их значений через расчеты.

Laboratory tasks

2.1. Характеризация схемы двухвходовой ячейки NAND (DNAND02 gate)

- Постройте схему NAND основанную на информации в таблице table 1 (Fig. 8.1).

|

|

Подложки NMOS транзисторов подключены к VSS

Подложки PMOS транзисторов подключены к VDD

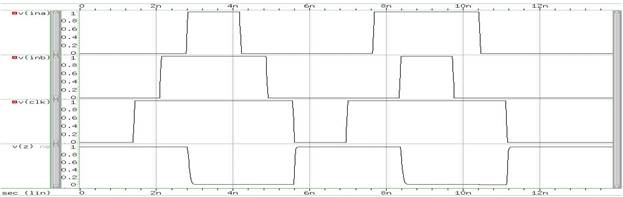

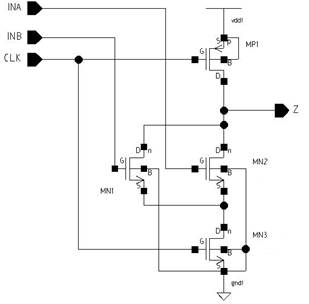

Рис. 8.1. Динамический И-НЕ: символ, схема, таблица истинности, формы входного и выходного сигналов

- Получите нетлист схемы (dnand02.netl file) и разместите его по следующей ссылке:

/student_lab/digital_ic/variant_val/...

- Входные файлы необходимые для симуляции.

Для входного файла примите:

- Входной slope: 50 ps

- Значение выходной нагрузки, Cload: 5 fF

2.1.1. Входной файл, находящий минимум выходного напряжения для двухвходовых динамических ячеек NAND и время переключения при помощи HSPICE представлен ниже:

*DNAND02 Gate

*Propagation Delay, Transition Time

| * HSPICE Netlist .options POST=1 parhier=local * Models section * Include models .include '/student_lab/digital_ic/all_models/model_val' * Design variables section * Define parameters .param vdd = VDD_val .param tr=TR_val .param freq=FREQ_val .param per=’1/freq’ .param tst=’0.5*per’ .temp Temp_val * Structural netlist section .include '/student_lab/digital_ic/variant_val/dnand02.netl' vvss vss gnd dc=0 vvdd vdd gnd dc='vdd' ***Input Signals (PWL) Vina ina 0 pwl 0 0 '2*tst' 0 '2*tst+tr' vdd '3*tst' vdd '3*tst+tr' 0 '5.5*tst ' 0 '5.5*tst+tr' vdd '7.5*tst' vdd + '7.5*tst+tr' 0 '10*tst' 0 Vinb inb 0 pwl 0 0 '1.5*tst' 0 '1.5*tst+tr' vdd '3.5*tst' vdd '3.5*tst+tr' 0 '6*tst' 0 '6*tst+tr' vdd '7*tst' vdd + 7*tst+tr' 0 '10*tst' 0 Vclk clk 0 pwl 0 0 tst 0 'tst+tr' vdd '4*tst' vdd '4*tst+tr' 0 '5*tst' 0 '5*tst+tr' vdd '8*tst' vdd '8*tst+tr' 0 '10*tst' 0 cload z gnd LOAD_val * Analysis section * Transient Analyses .tran ‘0.01*tr’ ‘5*per’ .probe v(*) *Options .option post probe .option autostop ***Measures ***Propagation Delay .meas tran tplh_clk_z trig v(clk) val='0.5*vdd' fall=1 targ v(z) val='0.5*vdd' rise=1 .meas tran tphl_ina_z trig v(ina) val='0.5*vdd' rise=1 targ v(z) val='0.5*vdd' fall=1 .meas tran tphl_inb_z trig v(inb) val='0.5*vdd' rise=2 targ v(z) val='0.5*vdd' fall=2 ***Transition Time .meas tran ttlh_clk_z trig v(z) val='0.4*vdd' rise=1 targ v(z) val='0.6*vdd' rise=1 .meas tran tthl_ina_z trig v(z) val='0.6*vdd' fall=1 targ v(z) val='0.4*vdd' fall=1 .meas tran tthl_inb_z trig v(z) val='0.6*vdd' fall=2 targ v(z) val='0.4*vdd' fall=2 .end |

2.1.2. Входной файл для измерения среднего значения потребления тока и динамической мощности для двух входных динамических NAND ячеек в режиме переключения при помощи HSPICE представлен ниже:

*DNAND02 Gate

*I average, dynamic power

* HSPICE Netlist

.options POST=1 parhier=local

* Models section

* Include models

.include '/student_lab/digital_ic/all_models/model_val'

* Design variables section

* Define parameters

.param vdd = VDD_val

.param tr=TR_val

.param freq=FREQ_val

.param per=’1/freq’

.param tst=’0.5*per’

.temp Temp_val

* Structural netlist section

.include '/student_lab/digital_ic/variant_val/dnand02.netl'

vvss vss gnd dc=0

vvdd vdd gnd dc='vdd'

***Input Signals (PWL)

Vina ina 0 pwl 0 0 '2*tst' 0 '2*tst+tr' vdd '3*tst' vdd '3*tst+tr' 0 '5.5*tst ' 0 '5.5*tst+tr' vdd '7.5*tst' vdd

+ '7.5*tst+tr' 0 '10*tst' 0

Vinb inb 0 pwl 0 0 '1.5*tst' 0 '1.5*tst+tr' vdd '3.5*tst' vdd '3.5*tst+tr' 0 '6*tst' 0 '6*tst+tr' vdd '7*tst' vdd

+ 7*tst+tr' 0 '10*tst' 0

Vclk clk 0 pwl 0 0 tst 0 'tst+tr' vdd '4*tst' vdd '4*tst+tr' 0 '5*tst' 0 '5*tst+tr' vdd '8*tst' vdd '8*tst+tr' 0 '10*tst' 0

cload z gnd LOAD_val

* Analysis section

* Transient Analyses

.tran ‘0.01*tr’ ‘5*per’

.probe v(*)

*Options

.option post probe

.option autostop

***Measures

***Average Current, Dynamic Power

.meas tran Iavg avg I(vvdd) from 0 to per

.meas pdyn param = ‘vdd*iavg’

.end

2.2. Характеризация схемы двухвходовой ячейки NOR (DNOR02 gate)

- Постройте схему динамической NOR ячейки с двумя входами, основанную на информации в таблице 1 (Fig. 8.2).

|

|

Подложки NMOS транзисторов подключены к VSS

Подложки PMOS транзисторов подключены к VDD

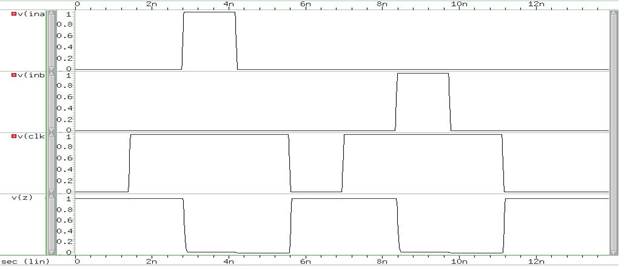

Рис. 8.2. Динамический ИЛИ-НЕ: символ, схема, таблица истинности, формы входного и выходного сигналов

- Получите нетлист схемы (dnor02.netl file) и разместите его по адресу:

/student_lab/digital_ic/variant_val/...

- Input files necessary for simulation.

For input files take:

- Input slope: 50 ps

- Output capacitive load value, Cload: 5 fF

2.2.1. Входной файл для нахождения задержек для двухвходовых динамических ячеек NOR и время переключения при помощи HSPICE представлен ниже::

*DNOR02 Gate

*Propagation Delay, Transition Time

* HSPICE Netlist

.options POST=1 parhier=local

* Models section

* Include models

.include '/student_lab/digital_ic/all_models/model_val'

* Design variables section

* Define parameters

.param vdd = VDD_val

.param tr=TR_val

.param freq=FREQ_val

.param per=’1/freq’

.param tst=’0.5*per’

.temp Temp_val

* Structural netlist section

.include '/student_lab/digital_ic/variant_val/dnor02.netl'

vvss vss gnd dc=0

vvdd vdd gnd dc='vdd'

***Input Signals (PWL)

Vina ina 0 pwl 0 0 '2*tst' 0 '2*tst+tr' vdd '3*tst' vdd '3*tst+tr' 0 '10*tst' 0

Vinb inb 0 pwl 0 0 '6*tst' 0 '6*tst+tr' vdd '7*tst' vdd '7*tst+tr' 0 '10*tst' 0

Vclk clk 0 pwl 0 0 tst 0 'tst+tr' vdd '4*tst' vdd '4*tst+tr' 0 '5*tst' 0 '5*tst+tr' vdd '8*tst' vdd '8*tst+tr' 0 '10*tst' 0

cload z gnd LOAD_val

* Analysis section

* Transient Analyses

.tran ‘0.01*tr’ ‘5*per’

.probe v(*)

*Options

.option post probe

.option autostop

***Measures

***Propagation Delay

.meas tran tplh_clk_z trig v(clk) val='0.5*vdd' fall=1 targ v(z) val='0.5*vdd' rise=1

.meas tran tphl_ina_z trig v(ina) val='vdd*0.5' rise=1 targ v(z) val='vdd*0.5' fall=1

.meas tran tphl_inb_z trig v(inb) val='vdd*0.5' rise=1 targ v(z) val='vdd*0.5' fall=2

***Transition Time

.meas tran ttlh_clk_z trig v(z) val='0.6*vdd' rise=1 targ v(z) val='0.4*vdd' rise=1

.meas tran tthl_ina_z trig v(z) val='vdd*0.6' fall=1 targ v(z) val='vdd*0.4' fall=1

.meas tran tthl_inb_z trig v(z) val='vdd*0.6' fall=2 targ v(z) val='vdd*0.4' fall=2

.end

2.2.2. Входной файл, для измерения среднего потребления по мощности и динамического потребления, для двух входных динамических ячеек NOR при помощи HSPICE представлен ниже:

*DNOR02 Gate

*I average, dynamic power

* HSPICE Netlist

.options POST=1 parhier=local

* Models section

* Include models

.include '/student_lab/digital_ic/all_models/model_val'

* Design variables section

* Define parameters

.param vdd = VDD_val

.param tr=TR_val

.param freq=FREQ_val

.param per=’1/freq’

.param tst=’0.5*per’

.temp Temp_val

* Structural netlist section

.include '/student_lab/digital_ic/variant_val/dnor02.netl'

vvss vss gnd dc=0

vvdd vdd gnd dc='vdd'

***Input Signals (PWL)

Vina ina 0 pwl 0 0 '2*tst' 0 '2*tst+tr' vdd '3*tst' vdd '3*tst+tr' 0 '10*tst' 0

Vinb inb 0 pwl 0 0 '6*tst' 0 '6*tst+tr' vdd '7*tst' vdd '7*tst+tr' 0 '10*tst' 0

Vclk clk 0 pwl 0 0 tst 0 'tst+tr' vdd '4*tst' vdd '4*tst+tr' 0 '5*tst' 0 '5*tst+tr' vdd '8*tst' vdd '8*tst+tr' 0 '10*tst' 0

cload z gnd LOAD_val

* Analysis section

* Transient Analyses

.tran ‘0.01*tr’ ‘5*per’

.probe v(*)

*Options

.option post probe

.option autostop

***Measures

***Average Current, Dynamic Power

.meas tran Iavg avg I(vvdd) from 0 to per

.meas pdyn param = ‘vdd*iavg’

.end

Steps to Perform the Lab Exercise

Симуляция двух входных NAND ячеек.

В режиме передачи:

- Получите диаграммы для входных и выходных сигналов при:

1) LOAD_val = 0

2) LOAD_val = Cload

- Померьте tPHL задержки для входов INA и INB (Table 9, point 4) когда

1) LOAD_val = 0

2) LOAD_val = Cload

- Симуляция двух входных ячеек NOR в режиме передачи:

Получите диаграммы для входных и выходных сигналов при

1) LOAD_val = 0

2) LOAD_val = Cload

- Померьте tPHL задержки для входов INA и INB (Table 9, point 4) когда

1) LOAD_val = 0

2) LOAD_val = Cload

- Померьте среднее значение потребления по мощности и динамическое потребление мощности при

1) LOAD_val = 0

2) LOAD_val = Cload