Микропроцессорный модуль является по сути основным узлом микропроцессорной системы. В его состав входит сам микропроцессор, тактовый генератор, буферные регистры, шинный формирователь, дешифратор адреса контроллера прерываний и контроллер прерываний.

Микропроцессорный модуль является по сути основным узлом микропроцессорной системы. В его состав входит сам микропроцессор, тактовый генератор, буферные регистры, шинный формирователь, дешифратор адреса контроллера прерываний и контроллер прерываний.

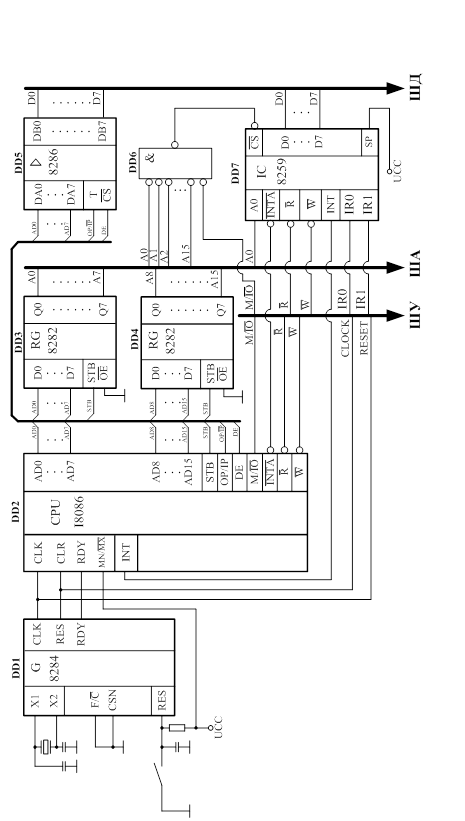

Функциональная схема микропроцессорного модуля представлена на рисунке 2.

|

Рис. 2. Функциональная схема микропроцессорного модуля.

Генератор тактовых импульсов выполнен на микросхеме 8284. Генератор имеет в своем составе кварцевый резонатор для обеспечения повышенной стабильности частоты генерируемого сигнала, кнопку сброса обеспечивающую выдачу генератором на вход процессора сигнала reset,

RC цепь исключающую эффект “дребезга” контактов при нажатии кнопки сброса. Генератор имеет пять входов и три выхода. Ко входам X1 и X2 подключается кварцевый резонатор, вход F/C служит для выбора внутреннего или внешнего задающего генератора, при подаче на него логического “0” генерация тактовых импульсов производится внутренним генератором, при подаче “1” – внешним задающим генератором, вход CSN позволяет обеспечить синхронизацию тактовых сигналов путем сброса делителей частоты при работе от внешнего задающего генератора. Входы F/C и CSN в данной схеме заземлены. Ко входу RES подключается кнопка сброса. На выходе CLK подключенному ко входу CLK процессора, формируется тактовый сигнал генерируемый генератором. Выход RES служит для выдачи сигнала сброса, и подключен ко входу CLR процессора. Выход RDY генератора подключен ко входу RDY процессора, и выдает сигнал готовности генератора.

RC цепь исключающую эффект “дребезга” контактов при нажатии кнопки сброса. Генератор имеет пять входов и три выхода. Ко входам X1 и X2 подключается кварцевый резонатор, вход F/C служит для выбора внутреннего или внешнего задающего генератора, при подаче на него логического “0” генерация тактовых импульсов производится внутренним генератором, при подаче “1” – внешним задающим генератором, вход CSN позволяет обеспечить синхронизацию тактовых сигналов путем сброса делителей частоты при работе от внешнего задающего генератора. Входы F/C и CSN в данной схеме заземлены. Ко входу RES подключается кнопка сброса. На выходе CLK подключенному ко входу CLK процессора, формируется тактовый сигнал генерируемый генератором. Выход RES служит для выдачи сигнала сброса, и подключен ко входу CLR процессора. Выход RDY генератора подключен ко входу RDY процессора, и выдает сигнал готовности генератора.

В качестве центрального процессора используется микросхема микропроцессора I8086. Эта микросхема имеет шестнадцать тристабильных входов/выходов AD0-AD15, обеспечивающих выдачу адреса на шину адреса, и выдачу (прием) данных на (с) шину данных. Эти выходы подключены к двум микросхемам 8282 и к одной микросхеме 8286 таким образом, что младшие восемь разрядов подключены к одной микросхеме 8282 и одной 8286, старшие к оставшейся микросхеме 8282. Сигнал STB формируемый микропроцессором является стробирующим сигналом для буферных регистров RG. Выход OP/IP формирует сигнал направления передачи данных для шинного формирователя выполненного на микросхеме 8286. Сигнал DE определяет тип информации передаваемой в текущий момент на шину AD0-AD15 (адрес/данные), и является сигналом выбора микросхемы для шинного формирователя. Сигнал M/IO служит для указания типа устройства (память или устройства В/В) при адресации. Сигналы R и W являются стробирующими сигналами чтения и записи соответственно. На вход INT поступают сигналы запроса прерывания от контроллера прерываний, с выхода INTA обратно в контроллер прерываний поступают сигналы подтверждения прерывания. Вход процессора MN/MX служит для выбора типа конфигурации системы (максимальная/минимальная). Для выбора минимальной конфигурации к этому входу подведена логическая “1”.

В качестве центрального процессора используется микросхема микропроцессора I8086. Эта микросхема имеет шестнадцать тристабильных входов/выходов AD0-AD15, обеспечивающих выдачу адреса на шину адреса, и выдачу (прием) данных на (с) шину данных. Эти выходы подключены к двум микросхемам 8282 и к одной микросхеме 8286 таким образом, что младшие восемь разрядов подключены к одной микросхеме 8282 и одной 8286, старшие к оставшейся микросхеме 8282. Сигнал STB формируемый микропроцессором является стробирующим сигналом для буферных регистров RG. Выход OP/IP формирует сигнал направления передачи данных для шинного формирователя выполненного на микросхеме 8286. Сигнал DE определяет тип информации передаваемой в текущий момент на шину AD0-AD15 (адрес/данные), и является сигналом выбора микросхемы для шинного формирователя. Сигнал M/IO служит для указания типа устройства (память или устройства В/В) при адресации. Сигналы R и W являются стробирующими сигналами чтения и записи соответственно. На вход INT поступают сигналы запроса прерывания от контроллера прерываний, с выхода INTA обратно в контроллер прерываний поступают сигналы подтверждения прерывания. Вход процессора MN/MX служит для выбора типа конфигурации системы (максимальная/минимальная). Для выбора минимальной конфигурации к этому входу подведена логическая “1”.

Буферные регистры выполнены на восьми разрядных микросхемах 8282. Входы данных этих микросхем подключены к выходам AD0-AD15 микропроцессора, выходы подключены к шине адреса. На вход стробирования STB поступает сигнал сторбирования адреса STB с процессора, ко входу выбора микросхемы OE подведен логический “0”.

Буферные регистры выполнены на восьми разрядных микросхемах 8282. Входы данных этих микросхем подключены к выходам AD0-AD15 микропроцессора, выходы подключены к шине адреса. На вход стробирования STB поступает сигнал сторбирования адреса STB с процессора, ко входу выбора микросхемы OE подведен логический “0”.

Шинный формирователь выполнен на восьми разрядной микросхеме 8286. Входы данных этой микросхемы подключены к входам/выходам AD0-AD7 микропроцессора, выходы подключены к шине данных. На вход направления передачи данных поступает сигнал OP/IP с процессора, ко входу выбора микросхемы CS подведен сигнал DE формируемый процессором.

На микросхеме DD6 выполнен дешифратор адреса для контроллера прерываний (8259). Ко входу дешифратора подключены все разряды шины адреса и сигнал M/IO. На выходе дешифратора формируется логический “0” если все разряды шины адреса находятся в состоянии логического “0” и сигнал M/IO сигнализирует о выборе устройства ввода/вывода. Выход дешифратора подключен ко входу CS (выбор микросхемы) контроллера прерываний.

На микросхеме DD6 выполнен дешифратор адреса для контроллера прерываний (8259). Ко входу дешифратора подключены все разряды шины адреса и сигнал M/IO. На выходе дешифратора формируется логический “0” если все разряды шины адреса находятся в состоянии логического “0” и сигнал M/IO сигнализирует о выборе устройства ввода/вывода. Выход дешифратора подключен ко входу CS (выбор микросхемы) контроллера прерываний.

Контроллер прерываний выполнен на микросхеме 8259. Микросхема подключается к шине данных через входы/выходы D0-D7. Вход A0, подключенный к младшему разряду шины адреса используется для выбора регистров контроллера при обмене данными между контроллером и процессором. Выход INT подключенный к одноименному входу процессора используется для формирования запроса прерывания контроллером, в свою очередь вход контроллера INTA обеспечивает получение подтверждения прерывания. Сигналы R и W являются стробирующими сигналами чтения и записи информации соответственно. Вход SP подтянутый к логической “1”, служит для выбора роли микросхемы (ведущий “1”, ведомый “0”) если используется несколько микросхем одновременно. На входы IR0, IR1 поступают запросы прерывания от модуля ввода/вывода.

Контроллер прерываний выполнен на микросхеме 8259. Микросхема подключается к шине данных через входы/выходы D0-D7. Вход A0, подключенный к младшему разряду шины адреса используется для выбора регистров контроллера при обмене данными между контроллером и процессором. Выход INT подключенный к одноименному входу процессора используется для формирования запроса прерывания контроллером, в свою очередь вход контроллера INTA обеспечивает получение подтверждения прерывания. Сигналы R и W являются стробирующими сигналами чтения и записи информации соответственно. Вход SP подтянутый к логической “1”, служит для выбора роли микросхемы (ведущий “1”, ведомый “0”) если используется несколько микросхем одновременно. На входы IR0, IR1 поступают запросы прерывания от модуля ввода/вывода.