Оглавление

1 Введение. 3

1.1 Терминология. 3

1.1.1 Кристалл. 3

1.1.2 Микросхема. 3

1.1.3 Корпуса: DIP, Chip, BGA. 3

1.1.4 Печатная плата. 3

1.2 Цифровая электроника. 3

1.2.1 Логические уровни и напряжение. 3

1.2.2 Положительная и отрицательная логика. 3

1.2.3 Виды цифровых кодов. 3

2 Технологические виды цифровой логики. 3

2.1 По типу технологии: КМОП, ТТЛ, ДТЛ, ЭСЛ. 3

2.2 По напряжению питания: 5В, 3.3В, 2.5В, 1.8В, 1.5В, 1.2В, 1В. 3

3 Виды цифровых логических схем.. 3

3.1 Комбинаторные логические схемы.. 3

3.1.1 Стандартные вентили, их обозначение и таблица истинности. 3

3.1.2 Основные законы алгебры логики. 4

3.1.3 Базисный элемент ИЛИ-НЕ для построения любой комбинаторной логики. 4

3.1.4 Полусумматоры и сумматоры. 4

3.1.5 Дешифраторы.. 4

3.1.6 Цифровые компараторы.. 4

3.1.7 Мультиплексоры.. 4

3.2 Последовательностные логические схемы.. 4

3.2.1 Триггеры.. 4

3.2.2 Регистры.. 4

4 Проектирование цифровых схем.. 4

4.1 RTL представление. 4

4.2 Задержки на элементах. 4

4.3 Статический тайминг анализ. 4

4.3.1 Гонки сигналов. 4

4.3.2 Максимальная задержка. 4

4.3.3 Минимальная задержка. 4

5 Память. 4

5.1 ОЗУ.. 5

5.1.1 Статическое. 5

5.1.2 Динамическое. 5

5.2 ПЗУ.. 5

5.2.1 Однократно программируемое. 5

5.2.2 Многократно программируемое. 5

6 Типы цифровых микросхем.. 5

6.1 Стандартная логика. 6

6.2 Application-specific integrated circuit (ASIC) 6

6.3 Программируемые логические интегральные схемы (ПЛИС) 7

6.3.1 Типы ПЛИС.. 7

6.4 Контрольные вопросы.. 15

7 Интерфейсы.. 16

7.1 UART. 16

7.2 SPI. 16

7.3 Rs232. 16

7.4 Rs422. 16

7.5 Rs485. 16

7.6 Mil 1553b. 16

7.7 Spacewire. 16

8 Надёжность радиоэлектронной аппаратуры.. 16

8.1 Расчеты надёжности. 16

8.2 Схемы отказоустойчивости. 16

8.3 Расчёт радиационной стойкости. 16

9 Проверки и испытания РЭА.. 16

9.1 Этапы проверок РЭА.. 16

9.2 Испытания РЭА.. 16

9.2.1 ЛОИ.. 16

|

|

9.2.2 КДИ.. 16

9.2.3 ПСИ.. 16

1 Введение

1.1 Терминология

1.1.1 Кристалл

1.1.2 Микросхема

1.1.3 Корпуса: DIP, Chip, BGA.

1.1.4 Печатная плата

1.2 Цифровая электроника

1.2.1 Логические уровни и напряжение

1.2.2 Положительная и отрицательная логика

1.2.3 Виды цифровых кодов

1.2.3.1 Бинарный код

1.2.3.2 Дополнительный код

1.2.3.3 Код Грэя

2 Технологические виды цифровой логики

2.1 По типу технологии: КМОП, ТТЛ, ДТЛ, ЭСЛ.

2.2 По напряжению питания: 5В, 3.3В, 2.5В, 1.8В, 1.5В, 1.2В, 1В.

3 Виды цифровых логических схем

3.1 Комбинаторные логические схемы

3.1.1 Стандартные вентили, их обозначение и таблица истинности

3.1.1.1 Не

3.1.1.2 И

3.1.1.3 Или

3.1.1.4 Исключающее ИЛИ

3.1.1.5 Буферы

3.1.1.5.1 Выход с открытым коллектором

3.1.1.5.2 Выход с тремя состояниями

3.1.1.5.3 Схемы объединения. Проводное И.

3.1.2 Основные законы алгебры логики

3.1.3 Базисный элемент ИЛИ-НЕ для построения любой комбинаторной логики

3.1.4 Полусумматоры и сумматоры.

3.1.5 Дешифраторы

3.1.6 Цифровые компараторы

3.1.7 Мультиплексоры

3.2 Последовательностные логические схемы

3.2.1 Триггеры

3.2.1.1 RS-триггер и как он реализуется с помощью вентилей

3.2.1.2 FD

3.2.1.3 FT

3.2.1.4 JK

3.2.1.5 LD

3.2.1.6 Триггер Шмитта.

3.2.2 Регистры

3.2.2.1 Параллельный

3.2.2.2 Последовательный (сдвиговый)

3.2.2.3 Счетчики

4 Проектирование цифровых схем

4.1 RTL представление

4.2 Задержки на элементах

4.3 Статический тайминг анализ

4.3.1 Гонки сигналов

4.3.2 Максимальная задержка

4.3.3 Минимальная задержка

5 Память

5.1 ОЗУ

5.1.1 Статическое

5.1.1.1 По количеству портов

5.1.1.1.1 Однопортовое

5.1.1.1.2 Двухпортовое

5.1.1.2 По тактированию

5.1.1.2.1 Асинхронное

5.1.1.2.2 Синхронное

5.1.1.3 Специальные типы ОЗУ

|

|

5.1.1.3.1 FIFO

5.1.1.3.2 STACK

5.1.2 Динамическое

5.2 ПЗУ

5.2.1 Однократно программируемое

5.2.1.1 Масочное

5.2.1.2 Antifuse

5.2.2 Многократно программируемое

5.2.2.1 Flash

5.2.2.1.1 NAND

5.2.2.1.1.1 SLC

5.2.2.1.1.2 MLC

5.2.2.1.1.3 TLC

5.2.2.1.2 NOR

5.2.2.2 EEPROM

5.2.2.3 MRAM

5.2.2.4 FRAM

5.2.2.5 CRAM

6 Типы цифровых микросхем

Современные цифровые микросхемы разделяются на следующие типы:

6.1 Стандартная логика.

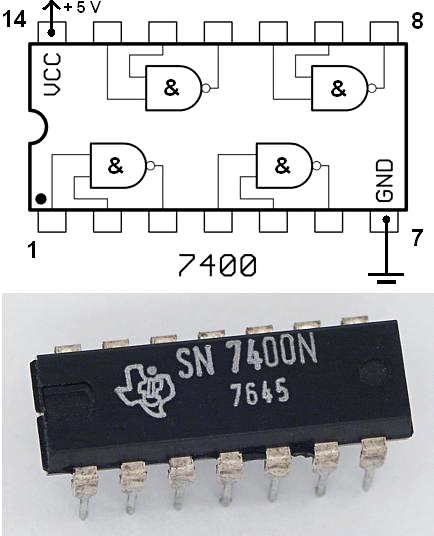

Это микросхемы, реализующие общие логические функции: комбинаторные и регистровые: логические вентили, триггеры, счетчики, сумматоры, компараторы, мультиплексоры, которые мы рассматривали ранее. Пример: серии 7400 ТТЛ и 4000 КМОП. Пример микросхемы из серии 7400 приведен на рисунке. Это микросхема SN7400N, содержащая 4 вентиля «ИЛИ-НЕ» в одном корпусе.

Из стандартной логики можно собрать схему, реализующую любые логические функции, однако это схема будет слишком громоздкой, особенно для сложных устройств. Процессор, собранный из стандартной логики, будет занимать целую комнату.

6.2 Application-specific integrated circuit (ASIC)

ASIC – интегральная схема, специализированная для решения конкретной задачи. В отличие от обычных интегральных схем стандартной логики, специализированные интегральные схемы применяются в конкретном устройстве и выполняют строго ограниченные функции, характерные только для данного устройства. По сути ASIC интегрирует внутри себя на одном полупроводниковом кристалле схему, которая может быть реализована путем соединения микросхем стандартной логики. Вследствие этого выполнение функций происходит быстрее, устройство становится компактнее и, в конечном счёте, дешевле. Примером ASIC может являться микросхема, разработанная исключительно для управления мобильным телефоном, микросхемы аппаратного кодирования/декодирования аудио- и видеосигналов (сигнальные процессоры).

|

|

Современные ASIC часто содержат 32-битный или даже 64-битный процессор, иногда в количестве нескольких ядер, блоки памяти (как ПЗУ, так и ОЗУ) и другие крупные блоки. Такие ASIC часто называют однокристальной системой или системой на кристалле System-on-Chip (SoC).

При разработке цифровых ASIC для описания их функциональности используют языки описания аппаратных устройств (HDL), такие как Verilog и VHDL.

6.3 Программируемые логические интегральные схемы (ПЛИС)

В отличие от обычных цифровых микросхем, рассмотренных ранее (стандартная логика и ASIC), логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования. Для программирования используются программатор и IDE (среда разработки), позволяющие задать желаемую структуру цифрового устройства в виде принципиальной электрической схемы или описания на специальных языках описания аппаратуры – Hardware Description Language (HDL). HDL – не язык программирования, хотя внешние сходства имеются. HDL – это язык, который описывает схему цифрового устройства в текстовом виде.

6.3.1 Типы ПЛИС

Основными типами ПЛИС, которые используются в современной электронике являются CPLD и FPGA. На текущий момент отличия между ними стали очень несущественными, но основные отличия – это то, что CPLD более маленькие по логической емкости, более простые по функциям, чем FPGA. Также CPLD всегда уже сконфигурированы (в них запрограммирована заданная пользователем цифровая схема) при включении питания. Большинство же типов ПЛИС при включении питания не сконфигурированы и требуют записи в них конфигурации.

6.3.1.1 Complex programmable logic device (CPLD)

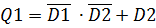

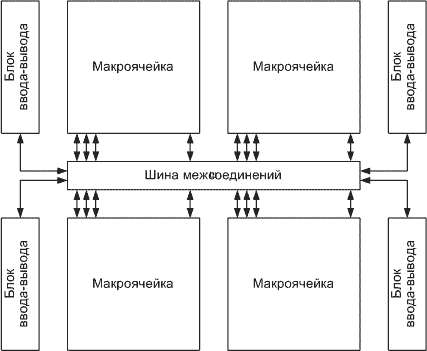

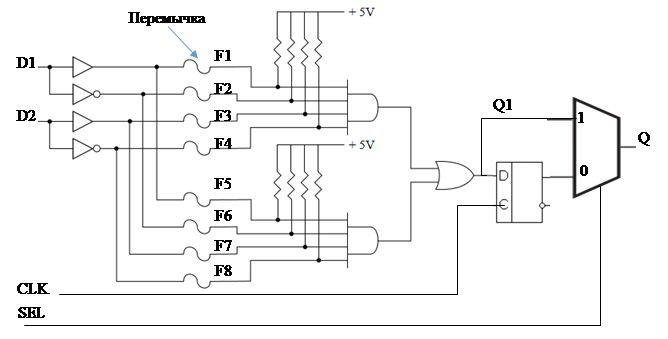

Программируемая логическая интегральная схема CPLD (еще ее называют в русскоязычной литературе программируемая логическая матрица или ПЛМ) состоит из нескольких макроячеек, расположенных на одном кристалле (см. Рисунок 1). Каждая макроячейка соединена с блоками ввода-вывода, осуществляющими формирование необходимого вида входов или выходов для работы с внешними схемами. Кроме того, все макроячейки и блоки ввода-вывода связаны между собой внутренними параллельными шинами. Приведенная на рисунке 3 микросхема CPLD состоит из четырех макроячеек, которые связаны между собой внутренними шинами и соединяются с блоками ввода-вывода. Макроячейка представляет универсальную схему (см Рисунок 2), с помощью которой можно реализовать любую логическую схему путем создания соединений или разрывов цепи на месте условных перемычек. Этот процесс называют конфигурированием или программированием CPLD. В качестве этих условных перемычек могут быть собственно плавкие перемычки или ячейки EEPROM или FLASH. Входы D1 и D2 проходят через инверторы, которые создают прямую и инверсную сигнал-«копию» этих входов внутри макроячейки, которые могут быть соединены (если перемычка соединена) или разорваны (перемычка оборвана) с многовходовыми вентилями «И», которые идут на вход вентилей «ИЛИ». На выход Q с помощью мультиплексора можно подать либо выход вентиля «ИЛИ» непосредственно, либо через D-триггер. С помощью данной схемы макроячейки, можно реализовать любую комбинаторную функцию от двух входов (как мы говорили ранее, любую цифровую комбинаторную схему можно реализовать, имея базисный набор вентилей И-ИЛИ-НЕ). А с помощью нескольких макроячеек в CPLD, можно реализовать комбинаторную функцию и на большее число входов. Входящий в макроячейку триггер позволяет создавать регистровые схемы. Например, если замкнуть перемычки F2, F4, F7, а остальные разомкнуть, то  . При этом, если SEL = 1, то Q = Q1, а если SEL = 0, то Q – это выход триггера, вход которого Q1.

. При этом, если SEL = 1, то Q = Q1, а если SEL = 0, то Q – это выход триггера, вход которого Q1.

К недостаткам мож но отнести то, что трудно обеспечить эффективное применение всех макроячеек. Всегда часть макроячеек остается неиспользуемыми. Часто из макроячейки используется только триггер или логический элемент "И" (“ИЛИ"). Остальная часть схемы зря занимает площадь кристалла и потребляет ток от источника питания.

Рисунок 1. Функциональная схема CPLD

Рисунок 2. Макроячейка CPLD

6.3.1.2 Field-Programmable Gate Array (FPGA)

FPGA – это программируемый пользователем массив вентилей. В целом похож на CPLD, но имеет более сложную структуру и большее количество ячеек.

Программируемы пользователем матрицы логических элементов (ППМЛЭ, FPGA) представляют собой матрицу реконфигурируемых элементов. С использованием специального программного обеспечения пользователь может описать свой проект на языке описания аппаратуры или в виде схемы, а затем реализовать его в FPGA. В ряде отношений матрицы FPGA мощнее и гибче, чем ПЛМ. В FPGA возможно реализовать как комбинационные, так и последовательностные схемы. В них можно реализовывать многоуровневые логические схемы, тогда как в ПЛМ могут быть реализованы только двухуровневые схемы. В современные FPGA интегрированы другие полезные узлы, такие как умножители, высокоскоростные устройства ввода/вывода, ЦАП, АЦП, большие ОЗУ и процессоры.

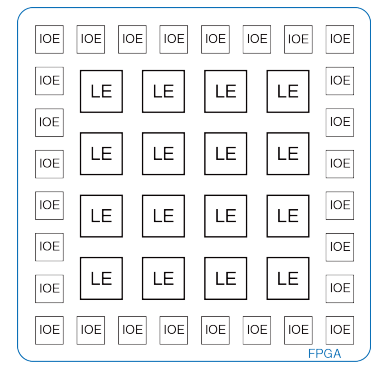

FPGA используются во многих потребительских продуктах, таких как автомобили, медицинское оборудование, устройства обработки медиаинформации. Например, в системах навигации, круиз-контроля, звуковоспроизведения автомобилей Mercedes Benz S-класса используется более десяти FPGA и PLD фирмы Xilinx. FPGA позволяют быстрее выводить изделия на рынок и упрощают отладку и добавление новых возможностей на поздних этапах жизненного цикла продукта. FPGA представляет собой матрицу конфигурируемых логических элементов (logic elements, ЛЭ, LE), которые также называются конфигурируемыми логическими блоками (configurable logic blocks, КЛБ,CLB). Каждый ЛЭ можно сконфигурировать для выполнения функций некоторой комбинационной или последовательностной схемы.

Рисунок 3 Обобщенная структура FPGA

На Рисунок 3 приведена обобщенная структура FPGA. ЛЭ окружены элементами ввода/вывода (input/output elements, IOE, ЭВВ), которые предназначены для организации обмена информацией между FPGA и прочими компонентами системы.

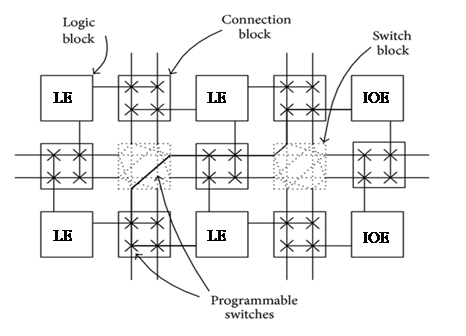

Рисунок 4. Программируемые каналы трассировки

Элементы ввода/вывода соединяют входы и выходы логических элементов с контактами корпуса микросхемы. Логические элементы могут быть соединены между собой и с элементами ввода/вывода с помощью программируемых каналов трассировки, которые являются обычными проводниками, плюс программируемые ключи (programmable switches) для формирования произвольных соединений. Любой connection block может создавать соединение или разрыв на месте символа X, а любой programmable switch может создавать соединение (сплошная линия) по любому пути, обозначенному пунктиром (см. Рисунок 4)

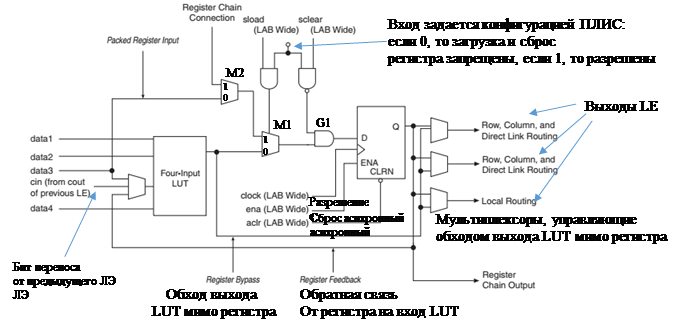

Рисунок 5 Логический элемент (LE) FPGA Cyclone IV фирмы Intel (бывшая Altera).

Лидерами на рынке коммерческих и промышленных FPGA являются фирмы Intel (бывшая Altera Corp.) и Xilinx, Inc. На рынке FPGA для военного и космического применения лидерами являются Xilinx и Microsemi (бывший Actel). На Рисунок 5 упрощенно показан один логический элемент FPGA фирмы Altera Cyclone IV, производство которой началось в 2009 году.

Основными компонентами логического элемента является четырехвходовая таблица истинности (LUT) и однобитовый регистр. Таблица истинности – это по сути однобитовая память с адресом, подающимся на входы. При этом каждой комбинации входов соответствует выбранное из памяти значение, которое подается на выход. Таким образом, LUT задает таблицу истинности для произвольной комбинаторной функции своих N входов и одного выхода. Логический элемент также содержит конфигурируемые мультиплексоры, предназначенные для коммутации сигналов в логическом элементе.

При программировании FPGA устанавливается содержимое таблиц истинности (LUT) и определяются входные сигналы мультиплексоров, которые проходят на их выход (т.е. фактически задаются управляющие сигналы для мультиплекосоров, изображенных без управляющих входов)

Логический элемент FPGA Cyclone IV содержит одну четырехвходовую таблицу истинности (LUT) и один триггер. Путем загрузки соответствующих значений в LUT, она может быть сконфигурирована для реализации произвольной логической функции четырех (или менее) аргументов. Также при конфигурировании FPGA сигналам выбора, которые определяют, как мультиплексоры будут коммутировать каналы передачи данных в пределах логического элемента (LE) и между ним и соседними логическими элементами (LE) или элементами ввода/вывода (IOE), присваиваются необходимые значения. Например, в зависимости от конфигурации мультиплексора на один из входов LUT некоторого LE может поступать сигнал или с его входа data 3 или с выхода регистра этого же LE (register feedback), или бит переноса carry out (например, из сумматора) от предыдущего ЛЭ (см. Рисунок 5). На остальные три входа LUT сигналы всегда поступают со входов LE data 1, data 2 и data 4. В зависимости от трассировки внешних соединений сигнал на входы data 1-4 поступает с IOE или выходов других LE. Выход LUT может поступать либо непосредственно на выход LE при реализации комбинационной логической схемы (по цепи register bypass через мультиплексоры, управляющие обходом выхода LUT мимо регистра), либо через триггер при создании последовательностной схемы. Сигнал на вход триггера может поступать с выхода LUT этого же LE (через вход 0 мультиплексора M1 и через вентиль «И» G1), входа data 3 (через вход 0 мультиплексора M2, вход 1 мультиплексора M1 и через вентиль «И» G1) или с выхода регистра предыдущего LE (через вход 1 мультиплексора M2, вход 1 мультиплексора M1 и через вентиль «И» G1). Мультиплексором M1 управляет сигнал синхронной загрузки sload. Если он равен 1, то разрешена синхронная загрузка триггера либо входным сигналом data3, либо выходом регистра другого LE (register chain connection) в зависимости от управляющего сигнала мультиплексора M2. Если sload = 0, то на вход триггера может подаваться только выход LUT. Сигнал sclear управляет синхронным сбросом триггера. Если он равен 1, то триггера сбрасывается по фронту clock, иначе триггер не сбрасывается. Кроме того, в LE входит ряд вспомогательных схем: дополнительные мультиплексоры для трассировки, схемы управления сигналами разрешения и сброса триггера (выдающие асинхронный сброс aclr, который сбрасывает триггер сразу, в независимости от сигнала clock, а также сигнал разрешение ena), схемы, позволяющие реализовать сумматор с последовательным переносом. В FPGA фирмы Altera группы из 16 LE объедены в блок логических матриц (logic array block, LAB), для передачи данных между LE одного блока существуют специальные локальные соединения (local routing на рисунке). Таким образом, в LE FPGA Cyclone IV можно реализовать одну функцию четырех (или менее) входов, причем она может быть комбинационной или последовательностной, то есть иметь на выходе триггер. FPGA других производителей организованы немного по-другому, но принцип построения остается общим. Например, в FPGA фирмы Xilinx седьмой серии вместо четырехвходовой LUT используется шестивходовая.

При разработке конфигурации FPGA проектировщик вначале создает схемное описание проекта или описание на HDL. Затем происходит имплементация проекта. Программное обеспечение имплементации определяет, как следует сконфигурировать LUT, мультиплексоры и каналы трассировки для реализации заданных функций. Эта конфигурационная информация загружается в FPGA. Так как FPGA Cyclone IV (а также FPGA XILINX) сохраняют конфигурационную информацию в статическом ОЗУ, они могут быть легко перепрограммированы. Такие FPGA еще называют SRAM-based. Содержимое статического ОЗУ FPGA может быть загружено с компьютера (в лабораторных условиях) или при включении питания из специальной микросхемы ЭСППЗУ (EEPROM). Некоторые производители встраивают ЭСППЗУ непосредственно в микросхему FPGA. Фирма Microsemi использует для конфигурирования своих FPGA однократно программируемые перемычки (технология Antifuse), или флеш-ключи (технология Flash).

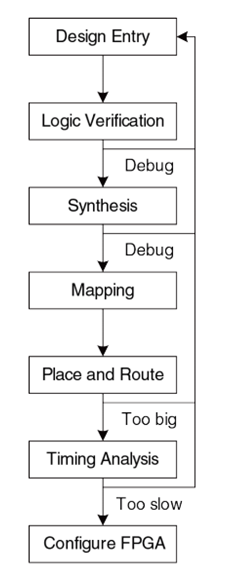

6.3.1.2.1 Процесс разработки цифровых схем на FPGA.

На Рисунок 6 показан процесс разработки цифровой системы на FPGA. Разработка обычно ведется на языке описания аппаратуры (HDL), хотя некоторые среды разработки FPGA поддерживают графический ввод схем (Design Entry). После разработки проводится временное моделирование. На входы схемы подаются тестовые воздействия и выходные сигналы во временной области (волновые диаграммы, они же переходные процессы) сравниваются с ожидаемыми, чтобы проверить работу устройства (Logic Verification). На данном этапе происходит чисто функциональная проверка логики схемы, без учета временных задержек на элементах схемы и проводниках. Обычно требуется некоторая отладка. Далее в процессе логического синтеза HDL описание преобразуется в булевы функции (Synthesis). Современные средства синтеза строят принципиальные схемы реализаций этих функций, и скрупулезный разработчик анализирует эти схемы, а также все предупреждения, появившиеся в процессе синтеза, чтобы убедиться, что реализована именно желаемая логика. Иногда небрежное описание приводит к генерации схем, больших по размерам, чем требуется, и схем с асинхронной логикой работы.

Когда результаты синтеза удовлетворительны, среда разработки отображает функции на логические элементы конкретной микросхемы (Mapping). Это отображение фактически реализует заданную пользователем логику с использованием элементов конкретной микросхемы FPGA. В результате отображения исходная схема, заданная пользователем в виде описания логики как бы «перерисовывается» с применением логических элементов конкретной микросхемы FPGA. Например, если пользователь нарисовал исходную схему, которая состоит из единственного вентиля «И», то после синтеза, из вентиля «И» будет получена булева функция «И», а после отображения на Cyclone IV, схема будет «перерисована» в виде логического элемента, в котором LUT будет сконфигурирован так, чтобы хранить таблицу истинности булевой функции «И», и будет задействован register bypass для обхода триггера и разводки выхода LUT на выход логического элемента.

После синтеза и отображения (Mapping) также проводится временное моделирование аналогично этапу Logic Verification, но при этом в модели схемы учитываются задержки на логических элементах конкретной микросхемы (т.к. на этом этапе уже известны конкретные задействованные в схеме логические элементы конкретной микросхемы, а у них, в свою очередь, известны задержки).

Инструмент размещения и трассировки (Place and Route) определяет, к какой таблице истинности относится каждая функция, и как эти таблицы соединены между собой. Задержка распространения сигнала возрастает с увеличением длины проводника, поэтому наиболее ответственные цепи следует размещать как можно ближе друг к другу. Если проект слишком велик, чтобы уместиться на одной  микросхеме FPGA, его придется пересматривать.

микросхеме FPGA, его придется пересматривать.

Временной анализ (Timing Analysis, его еще называют статическим временным анализом) сравнивает ограничения во временной области (например, заданный требуемый период тактовой частоты 100 МГц) с реальными задержками, получаемыми в схеме, и выдает отчет об ошибках. Данный временной анализ называют статическим, т.к. он не подразумевает анализ переходных процессов. Если схема работает слишком медленно, её, возможно, следует модернизировать или изменить конвейерную структуру.

После размещения и трассировки (Place and Route) также проводится временное моделирование аналогично этапу Logic Verification, но при этом в модели схемы учитываются задержки на логических элементах конкретной микросхемы, а также задержки распространения сигналов по проводникам (т.к. на этом этапе уже известны не только конкретные задействованные в схеме логические элементы конкретной микросхемы, но и длины проводников, их соединяющих).

После размещения и трассировки (Place and Route) также проводится временное моделирование аналогично этапу Logic Verification, но при этом в модели схемы учитываются задержки на логических элементах конкретной микросхемы, а также задержки распространения сигналов по проводникам (т.к. на этом этапе уже известны не только конкретные задействованные в схеме логические элементы конкретной микросхемы, но и длины проводников, их соединяющих).

После того, как проект исправлен, генерируется файл, определяющий содержание каждого логического элемента и конфигурацию всех трассировочных ресурсов или межсоединений в FPGA (Configure). Процесс синтеза, отображения, размещения и трассировки и генерации файла конфигурации ПЛИС называют имплементацией.

6.4 Контрольные вопросы

1) В чем отличия и в чем сходство между стандартной логикой и ASIC?

2) В чем отличия и в чем сходство между FPGA и CPLD?

3) В чем отличия и в чем сходство между стандартной логикой и ASIC с одной стороны, и FPGA и CPLD с другой стороны?

4) Для чего в составе макроячейки CPLD и логического элемента FPGA нужен триггер?

5) Для чего в FPGA нужны элементы ввода-вывода?

6) В чем отличие синхронного сброса триггера от асинхронного?

7) Что такое конфигурирование FPGA? Что происходит при конфигурировании?

8) Какими путями входной сигнал data3 может попасть на выход логического элемента LE (см Рисунок 5)?

9) В чем отличие логического синтеза и отображения?

10) Чем отличается исходная логическая схема, и схема, полученная в результате синтеза? В результате синтеза и отображения?

11) Сопоставьте понятие Timing analysis из данной главы с темами «Статический тайминг-анализ» и «RTL-представление» из предыдущих лекций. Фактически это то же самое, только Timing Analasys делается автоматически программным обеспечением разработки FPGA. В чем отличие статического тайминг-анализа от временного моделирования?

7 Интерфейсы

7.1 UART

7.2 SPI

7.3 Rs232

7.4 Rs422

7.5 Rs485

7.6 Mil 1553b

7.7 Spacewire

8 Надёжность радиоэлектронной аппаратуры

8.1 Расчеты надёжности

8.2 Схемы отказоустойчивости

8.3 Расчёт радиационной стойкости

9 Проверки и испытания РЭА

9.1 Этапы проверок РЭА

9.2 Испытания РЭА

9.2.1 ЛОИ

9.2.2 КДИ

9.2.3 ПСИ