Теоретическая часть.

Микропроцессоры.

Структура микропроцессорной системы.

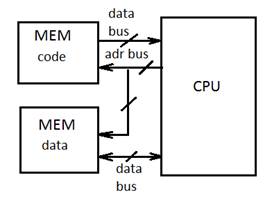

Любая микропроцессорная система состоит из трех основных компонентов: микропроцессора, производящего операции над данными, области памяти, где хранятся коды программ работы процессора и обрабатываемые массивы данных, и области устройств ввода-вывода, состоящую из схем, адаптирующих процессорную систему к внешним устройствам. Соединение блоков микропроцессорной системы производится по системной шине (СШ).

Системная шина состоит из трёх групп шин:

-шины адреса, на которую процессор выставляет адрес устройства в пространстве памяти или пространстве ввода-вывода, с которым будет производиться обмен информацией;

-шины данных, по которой производится обмен информацией;

-шины управления, по которой процессор посылает управляющие сигналы и получает запросы от устройств ввода-вывода.

Шина адреса однонаправленна, информация, следующая по ней, многоразрядна. Шина данных двунаправленна и информация, следующая по ней, также многоразрядна. Шина управления состоит из отдельных проводников, каждый из которых передает определенный сигнал управления. Формировать управляющие сигналы может процессорный блок и блок устройств ввода-вывода (запросы на процессорный блок).

Для полноценного обмена процессора по шине данных важны три момента: направление обмена (чтение/запись), объект обмена (память/устройства ввода-вывода) и, наконец, структура информации (данные/код).

Производительность процессора. Архитектура процессоров.

Если процессор работает с тактовой частотой F, то время T=1/F называется тактом. Время выполнения тестовой задачи можно рассчитать через такт

T x C x I,

где C – количество тактов на инструкцию, а I – количество инструкций на задачу.

Соответственно, чем меньше времени затрачивается на решение тестовой задачи, тем производительность процессора выше. В указанном выше выражении уменьшение T ограничено свойствами структуры, поэтому изменение производительности можно достичь изменением I или C.

Рассмотрим две основные архитектуры процессорного ядра. RISC-процессоры (Reduced Instruction Set Computer) и CISC-процессоры (Complete Instruction Set Computer).

Любой тип процессора выполняет инструкции, непрерывным потоком поступающие из памяти по шине данных. Выполнение инструкции можно разбить на 5 этапов:

1 – выборка кода из памяти по выставленному на адресной шине адресу,

2 – дешифрация кода,

3 – исполнение,

4 – получение результата,

5 – обратная загрузка результата.

Для ускорения процесса работа производится конвейерным способом, т.е. в каждый момент времени одновременно выполняются разные этапы следующих подряд команд. Рассмотренный выше случай – пятиступенчатый конвейер, но для разных процессоров возможно объединение 4 и 5 или 3, 4 и 5 этапов, в этих случаях мы имеем четырех- или трехступенчатый конвейер.

Для CISC – процессоров характерны сложные многотактовые инструкции, производители этих процессоров старались увеличить производительность за счёт уменьшения I. Но это приводило к приостановке конвейера, а, следовательно, снова снижало производительность процессора.

RISC – процессоры выполняют простые однотактовые операции. Они, в отличие от CISC не могут выполнять сложные задачи, зато для них C = 1, а так как операции обмена с пространством памяти в RISC выделены в отдельную группу, конвейер работает практически безостановочно и производительность высока.

Типы архитектуры микропроцессорных систем.

В настоящее время существуют два типа архитектуры микропроцессорных систем – Принстонская, или архитектура фон-Неймана, и Гарвардская.

В 1945 г. американский математик Джон фон Нейман сформулировал основные принципы работы современных компьютеров. Им была предложена архитектура, получившая его имя (von Neumann architecture) и предполагающая хранение программ и данных в общей памяти (1946 г.).

Сегодня такая архитектура наиболее характерна для микропроцессоров, ориентированных на использование в компьютерах. Примером могут служить микропроцессоры семейства х86. Эти микропроцессоры относятся к CISC-процессорам.

Архитектура, предполагающая раздельное использование памяти программ и данных, носит название гарвардской (Harvard architecture). Гарвардская архитектура позволяет центральному процессору работать одновременно как с памятью программ, так и с памятью данных, что существенно увеличивает производительность.

Структура ядра RISC-процессора предполагает наличие большой внутренней памяти, состоящей из регистров общего назначения, не имеющих дополнительных специальных функций. Исключение составляет так называемый «регистр нуля», присутствующий во многих модификациях таких процессоров. Этот регистр не предназначен для записи информации, в нем хранится «0». Кроме того, в общее число регистров общего назначения входят указатель стека и указатель связей. В этих регистрах всегда записываются адреса: в указатель стека – адрес вершины стека в исполняемой программе, а в указатель связей – адрес выхода из основной программы в вызванную область для возможности возврата. С помощью команд прямой и обратной загрузки происходит обмен между регистрами общего назначения и памятью данных. При работе команд, использующих АЛУ (арифметико-логическое устройство), операнды поступают только из внутренней памяти ядра, что экономит время обработки. Команды RISC-процессора, в основном, выполняются за один такт, все КЦУ, участвующие в процессе обработки, как коммутирующие, так и кодопреобразующие образуют цепочки и имеют общую задержку, не превышающую время такта. Команды пересылок между регистрами выполняются как арифметическая операция сложения с 0.

Структура ядра CISC-процессора, напротив, предполагает наличие малого количества регистров общего назначения, к тому же имеющих строго определенные функции. Эти функции обусловлены наличием большого количества указателей и счетчиков, входящих в состав ядра и позволяющих выполнять циклические операции, записанные в одной инструкции. При выполнении операций в АЛУ процессор может пользоваться операндами как хранящимися в регистрах общего назначения, так и в пространстве памяти, выделенном под данные. Таким образом, для написания программ под CISC-процессор используется большее количество адресаций данных, чем при программировании под RISC-процессор. Команды CISC-процессора выполняются за несколько тактов, что позволяет не выстраивать коммутационные КЦУ в цепочку, а использовать один коммутатор и служебный регистр (например, в командах пересылок).

Устройства памяти.

Внутренняя память микропроцессорной системы по способу доступа к ячейкам накопителя делится на 3 типа: адресная память, память с последовательным доступом и ассоциативная память.

В адресной памяти доступ к любой ячейке накопителя возможен по любому выставленному на шине адресу, независимо от предыдущего обращения.

В памяти с последовательным доступом порядок обращения к ячейкам задается счетчиком адресов, который невозможно переустановить в процессе работы с памятью. Таким образом, адрес обращения к каждой последующей ячейке отличается от предыдущего всегда на определенную величину.

В ассоциативной памяти ячейка накопителя содержит информацию, скопированную из основной адресной памяти. При этом некоторая часть адреса этой основной памяти, так называемый тег, или признак, также сохраняется в ассоциативной памяти. И, если вызываемый процессором адрес содержит такой тег, информация извлекается из накопителя ассоциативной памяти.

Пример ассоциативной памяти CACH-память. Данная структура в настоящем курсе не рассматривается.

Примеры памяти с последовательным доступом: память FIFO (first input, first output) и память LIFO (last input, first output), или stack.

Структура n-разрядного стека глубиной k. Вершина стека – RG0.

Примеры адресной памяти: постоянные запоминающие устройства ROM и оперативные запоминающие устройства RAM.

Постоянные запоминающие устройства, имеющие диодные накопители, могут программироваться однократно (ROM, PROM). Постоянные запоминающие устройства, матрицы накопителей которых построены на полевых транзисторах, возможно многократно перепрограммировать. Это могут быть схемы с ультрафиолетовым стиранием информации (EPROM), или с электрическим стиранием (EEPROM). В матрице накопителя постоянного запоминающего устройства строки подключены к выходам дешифратора адреса, а столбцы – к шине данных.

Оперативные запоминающие устройства делятся на 2 класса по структуре матриц накопителя. Это динамические ОЗУ (DRAM), имеющие ячейки накопителя емкостного типа, и статические ОЗУ (SRAM), в которых накопители строятся на основе триггерных ячеек. Обращение к ячейкам накопителя DRAM не может совершаться одновременно по строкам и столбцам из-за инерционности емкости. При считывании с DRAM информация стирается (емкость разряжается) и необходимо время на восстановление информации в ячейке. Такая память обладает низким быстродействием.

Память SRAM, имеющая триггерную матрицу накопителя, наоборот, обладает сверхвысоким быстродействием. Если рассматривать матрицу накопителя, имеющую 2n ячеек, то в SRAM имеется n адресных входов, распределенных на дешифраторы строки и столбца, вход CS (chip select), позволяющий подключить именно данный кристалл к шине и входы управления буферами записи и считывания.

На рисунке изображена внутренняя структура схемы SRAM на 4 адресных входа, на которые подаем адрес «0» (0000). Пересечение строки и столбца матрицы накопителя, на которых при этом будут уровни «1» выделено желтым. Видно, что будет активна ячейка синхронного RS-триггера, на вход C которой поступит «1». В ячейку будет записана информация, поступившая на входы S и R всей матрицы. На рисунке видно, как работают входы CS (активный уровень «0») и W/R(для записи активный уровень «0», а для чтения «1»). Получаемые на выходах элементов 2И уровни «1» открывают буфер записи или буфер чтения. Считывание с ячейки накопителя также управляется с элемента 2И на линиях выходов дешифраторов строк и столбцов.

В DRAM адресные входы подключаются к шине через мультиплексоры, выделяющие адреса строки и столбца. K=n/2. Вход RAS активен, когда подается адрес строки (строб строки), вход CAS активен после подачи адреса столбца (строб столбца).