Триггеры

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время.

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации.

RS-триггеры [править | править вики-текст]

RS-триггер асинхронный [править | править вики-текст]

| S | R | Q(t) | Q(t) |

Асинхронный RS-триггер с инверсными входами

RS-триггер [10][11], или SR-триггер (от англ. Set/Reset — установить/сбросить) — асинхронный триггер, который сохраняет своё предыдущее состояние при неактивном состоянии обоих входов и изменяет своё состояние при подаче на один из его входов активного уровня. При подаче на оба входа активного уровня состояние триггера вообще говоря неопределённо, но в конкретных реализациях на логических элементах оба выхода принимают состояния либо логического нуля, либо логической 1. В зависимости от конкретной реализации активным входным уровнем может быть как логическая 1, так и логический 0. Так, в RS-триггере выполненном на 2 элементах 2И-НЕ активным входным уровнем является логический 0.

При подаче активного уровня на вход S (от англ. Set — установить) выходное состояние становится равным логической единице. А при подаче активного уровня на вход R (от англ. Reset — сбросить) выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы активные уровни не определено и зависит от реализации, например в триггере на элементах «или-не» оба выхода переходят в состояние логической 1, которое сохраняется пока на входах удерживаются логические 0. Перевод одного из входов в неактивное состояние, в данном примере в логическую 1, переводит триггер в одно из разрешённых устойчивых состояний. Одновременный перевод обоих входов из активного в неактивное состояние вызывает непредсказуемое переключение триггера в одно из устойчивых состояний. RS-триггер используется для формирования сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством подачи импульсов на входы, которые разнесены во времени.

RS-триггер синхронный[править | править вики-текст]

| C | S | R | Q(t) | Q(t+1) |

| x | x | |||

| не определено | ||||

| не определено |

Схема синхронного RS-триггера совпадает со схемой одноступенчатого парафазного (двухфазного) D-триггера, но не наоборот, так как в парафазном (двухфазном) D-триггере не используются комбинации S=0, R=0 и S=1, R=1.

Алгоритм функционирования синхронного RS-триггера можно представить формулой

{\displaystyle Q(t+1)={\overline {R}}\cdot \left(~Q(t)+S~\right)+x\cdot S\cdot R,}

где x — неопределённое состояние.

Аналогично, триггер с доопределённым состоянием (Rs или rS) допускает наличие двух активных сигналов на момент тактирования, и переключается согласно тому сигналу, который для него является приоритетным.

·

Условное графическое обозначение синхронного RS-триггера.

·

Схема синхронного RS-триггера на элементах 2И-НЕ.

D-триггер синхронный [править | править вики-текст]

Пример условного графического обозначения (УГО) D-триггера с динамическим синхронным входом С и с дополнительными асинхронными инверсными входами S и R

| D | Q(t) | Q(t+1) |

D-триггер (D от англ. delay — задержка [13][14][15], либо от data [16] — данные) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Вход синхронизации С может быть статическим (потенциальным) и динамическим. У триггеров со статическим входом С информация записывается в течение времени, при котором уровень сигнала C=1. В триггерах с динамическим входом С информация записывается только в течение перепада напряжения на входе С. Динамический вход изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы (прямой динамический вход), то триггер срабатывает по фронту входного импульса, если от неё (инверсный динамический вход) — по срезу импульса. В таком триггере информация на выходе может быть задержана на один такт по отношению к входной информации.Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры.

·

·

Условное графическое обозначение D-триггера со статическим входом синхронизации С

D-триггер двухступенчатый [править | править вики-текст]

В одноступенчатом триггере имеется одна ступень запоминания информации, при этом, в состоянии записи триггер "прозрачен", т.е. все изменения на входе триггера повторяются на выходе триггера, что может привести к ложным срабатываниям устройств стоящих после триггера. В двухступенчатом триггере две ступени. Вначале информация записывается в первую ступень, все изменения на входе триггера во вторую ступень до сигнала перезаписи не попадают, затем, после перехода D-триггера первой ступени в режим хранения, информация переписывается во вторую ступень и появляется на выходе, что позволяет избежать состояния "прозрачности". Двухступенчатый триггер обозначают ТТ. Если первая ступень двухступенчатого D-триггера выполнена на статическом D-триггере, то двухступенчатый D-триггер называют двухступенчатым D-триггером со статическим управлением, а если на динамическом D-триггере, то двухступенчатый D-триггер называют двухступенчатым D-триггером с динамическим управлением.

T-триггеры [править | править вики-тексст]

Т-триггер (от англ. Toggle — переключатель) часто называют счётным триггером, так как он является простейшим счётчиком до 2.

Т-триггер асинхронный [править | править вики-текст]

Асинхронный Т-триггер не имеет входа разрешения счёта - Т и переключается по каждому тактовому импульсу на входе С.

T-триггер синхронный [править | править вики-текст]

| T | Q(t) | Q(t+1) |

Условное графическое обозначение (УГО) синхронного T-триггера с динамическим входом синхронизации С на схемах.

Синхронный Т-триггер [17], при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер можно построить на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе.

Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К.

В двухступенчатом (Master-Slave, MS) D-триггере инверсный выход Q соединяется со входом D, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение Q, то есть будет переключаться в противоположное состояние.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2.

JK-триггер[править | править вики-текст]

JK-триггер с дополнительными асинхронными инверсными входами S и R

| J | K | Q(t) | Q(t+1) |

JK-триггер [18][19] работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное, т.е. выполняется операция инверсии (чем он отличается от RS-триггеров с доопределённым состоянием, которые строго переходят в логический ноль или единицу, независимо от предыдущего состояния). Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — отключение) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние ютриггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации, поскольку понятие «одновременности» для асинхронных сигналов уже само по себе, в самом определении, содержит неопределённость поведения по типу гонки состояний (опять же, у Rs- и rS-триггеров этой проблемы нет, потому что они не осуществляют инверсию, а просто подчиняются тому сигналу, который для них приоритетен).

Теоретически, построение асинхронного JK-триггера по сути означало бы построение RS-триггера с динамическими входами, когда фронт сигнала J(S) переключает триггер в логическую единицу, а фронт сигнала K(R) — в ноль, даже если при этом уровень сигнала J продолжает сохраняться, и наоборот.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К [20].

Алгоритм функционирования JK-триггера можно представить формулой

Синхронные триггеры с динамическим тактированием изменяют своё состояние только в момент определённого перехода тактового сигнала (либо 0→1, либо 1→0, т.е. по переднему или заднему фронту тактового импульса). При неизменном уровне сигнала на тактовом входе никакие изменения на информационных входах не отражаются на состоянии триггера.

{\displaystyle Q(t+1)={\overline {Q}}(t)\cdot J+Q(t)\cdot {\overline {K}}.}222222

оророльол

2.Сдвигающие регистры

Последовательный регистр (регистр сдвига или сдвиговый регистр) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем).

Принципиальная схема последовательного (сдвигового) регистра, собранного на основе D триггеров и позволяющего осуществить преобразование последовательного кода в параллельный, приведена на рисунке 1. Обратите внимание, что если для параллельных регистров подходили как триггеры работающие по потенциалу (триггеры-защелки), так и триггеры, работающие по фронту, то для реализации последовательного (сдвигового) регистра подходят только D триггеры, работающие по фронту!

Рисунок 1. Схема последовательного (сдвигового) регистра

Внутри сдвигового регистра триггеры соединены последовательно, то есть выход первого соединён с входом второго и т.д. Условно-графическое изображение рассмотренного последовательного регистра приведено на рисунке 2.

Рисунок 2. Условно-графическое обозначение последовательного (сдвигового) регистра

Входы синхронизации в последовательных (сдвиговых) регистрах, как и в параллельных регистрах, объединяются. Это обеспечивает одновременность смены состояния всех триггеров, входящих в состав последовательного (сдвигового) регистра.

Преобразование последовательного кода в параллельный в последовательном (сдвиговом) регистре производится следующим образом. Отдельные биты двоичной информации последовательно подаются на вход сдвигового регистра D0. Каждый бит сопровождается отдельным тактовым импульсом синхронизации, который поступает на вход синхронизации последовательного регистра C.

Компараторы

Компара́тор аналоговых сигналов (от лат. comparare — сравнивать) — сравнивающее устройство[1]) — электронная схема, принимающая на свои входы два аналоговых сигнала и выдающая сигнал высокого уровня, если сигнал на неинвертирующем входе («+») больше, чем на инвертирующем (инверсном) входе («−»), и сигнал низкого уровня, если сигнал на неинвертирующем входе меньше, чем на инверсном входе. Значение выходного сигнала компаратора при равенстве входных напряжений, в общем случае не определено. Обычно в логических схемах сигналу высокого уровня приписывается значение логической 1, а низкому — логического 0.

Через компараторы осуществляется связь между непрерывными сигналами, например, напряжения и логическими переменными цифровых устройств.

Применяются в различных электронных устройствах, АЦП и ЦАП, устройствах сигнализации, допускового контроля и др.

Одно из напряжений (сигналов), подаваемое на один из входов компаратора обычно называют опорным или пороговым напряжением.

В аналитическом виде идеальный однопороговый неинвертирующий компаратор задаётся следующей системой неравенств:

{\displaystyle U_{out}={\begin{cases}U_{0},&{\mbox{if }}U_{in}<U_{ref}\\{\text{не определено}},&{\mbox{if }}U_{in}=U_{ref}\\U_{1},&{\mbox{if }}U_{in}>U_{ref}\end{cases}}}

В случае использования многозначной логики, например, троичной для учёта третьего состояния (равенство) применить соответствующую троичную функцию из чёткой троичной логики с чётким третьим значением.

Компаратор

Компаратор

3.Счетчики

Счётчик числа импульсов — устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики могут строиться на двухступенчатых D-триггерах, T-триггерах и JK-триггерах.

Основной параметр счётчика — модуль счёта — максимальное число единичных сигналов, которое может быть сосчитано счётчиком. Счётчики обозначают через СТ (от англ. counter).

Функция счетчика состоит в подсчете количества импульсных сигналов, поступающих на его вход. Элементом структуры счетчика является Т -триггер. Состояние счетчика характеризуется его содержимым

S (t) = snsn –1… s 0.

Здесь si – состояние i -го триггера счетчика. Код S (t) так или иначе соответствует количеству счетных импульсов, поступивших на счетчик к данному моменту времени t. Одно из состояний счетчика принимают за начальное s (0). Подсчет количества импульсов производится в счетчике по модулю K, где K – общее число различных состояний счетчика. Число K называют или модулем, или основанием, или коэффициентом пересчета, а также емкостью счетчика.

Классифицируют счетчики по следующим признакам: по коэффициенту пересчета K, по направлению счета, по способу управления счетом.

По коэффициенту пересчета K различают:

– бинарные счетчики, у которых K = 2 n +1;

– счетчики с произвольным коэффициентом пересчета(K ¹ 2 n +1, K = сonst);

– счетчики с произвольным K ¹ 2 n +1, K = var.

По направлению счета счетчики разделяют как:

– суммирующие, у которых S (0) < S (t), t > 0 (суммирующий счетчик – счетчик, который под действием счетного импульса переходит из состояния s (t) в (s (t) + 1)mod K состояние);

– вычитающие, у которых S (0) > S (t), t > 0 (вычитающий счетчик – счетчик, который под действием счетного импульса переходит из состояния s (t) в (s (t) – 1)mod K состояние);

– реверсивные счетчики (цифровые устройства, способные работать как в режиме суммирующего, так и в режиме вычитающего счетчика).

По способу управления счетом счетчики бывают:

– асинхронными, когда смена состояния счетчика происходит только под воздействием счетных импульсов;

– синхронными, для работы которых необходимы еще и хронирующие сигналы.

Признаки классификации независимы и могут встречаться в различных сочетаниях, скажем, асинхронный двоично-десятичный суммирующий счетчик или бинарный синхронный реверсивный счетчик.

Бинарные суммирующие счетчики

Функцию суммирующего счетчика можно задать такими соотношениями:

где x (t) – элемент потока счетных импульсов; S (t), S (t + 1) Î [0,2 n +1–1] – состояния счетчика.

Как видим, с каждым очередным счетным импульсом счетчик переходит из состояния s (t) в состояние s (t)+1.

Рис. 1.32. Суммирующий бинарный 4-разрядный счетчик с основанием K = 2 n +1, временные диаграммы и таблицы состояний 4-разрядного счетчика; УГО ИС 1533ИЕ19

Счетчики с исключением младших состояний – счетчики, начальное состояние которых отлично от нулевого (задается специальной схемой сброса в начальное состояние).

Счетчики с исключением младших состояний строят на основе счетчиков с параллельной записью. На рис. 1.35 показано УГО такого счетчика. Перед началом счета сигналом beg = 1 в счетчик по входам D записывается число S (0) = 2n+1 – K.

Рис. 1.35. УГО счетчика с исключением младших состояний

Счетчики с исключением старших состояний – счетчики с произвольным коэффициентом пересчета, начальное состояние которых равно 0.

Такие счетчики имеют естественную последовательность состояний. На рис. 1.36, а показана функциональная схема двоично-десятичного счетчика (т.е. у него K = 10), а на рис. 1.36, б – временные диаграммы, поясняющие его работу. В каждом из состояний S = (0,1,...,9) счетчик находится в течение периода следования счетных импульсов. При S = 10 на выходе схемы DD формируется значение у = 0, которым счетчик сбрасывается в нулевое состояние. Длительность пребывания счетчика в состоянии S = 10 составляет

t сбр = t DD + t R,

где t DD – задержка в схеме DD; t R – время срабатывания счетчика по сигналу на асинхронном установочном входе. Считается, что t сбр много меньше периода следования счетных импульсов, и потребитель результатов счета не успевает среагировать на показание S = 10. Ясно, что такое предположение далеко не всегда оправдывается.

Рис. 1.36. Функциональная схема и временные диаграммы двоично-десятичного счетчика

4.Счетчики

Счетчики - это устройства предназначенные для подсчета числа сигналов, поступающих на его вход и фиксация этого числа в виде кода хранящегося в триггерах. Количество разрядов счетчика определяется наибольшим числом, которое должно быть получено в каждом конкретном случае. Для подсчета и выдачи результата счетчики имеют один вход и n выходов, где n -количество разрядов. В общем случае счетчик имеет 2? устойчивых состояния, включая и 0 -е. Количество устойчивых состояний называется коэффициентом пересчета счетчика (М= 2?).

По назначению счетчики подразделяются на: простые и реверсивные.

Простые счетчики- счетчики, работающие только на сложение или вычитание.

Реверсивный счетчик может работать и на сложение и на вычитание.

Суммирующий счетчик предназначен для выполнения счета в прямом направление, т.е. с приходом очередного сигнала показатель счетчика увеличивается на 1.

Вычитающий счетчик предназначен для счета в обратном направлении, т.е. с приходом новогосигнала счетчик уменьшается на 1.

По способу организации счета счетчики бывают: асинхронные или синхронные.

По способу организации цепей переноса между разрядами счетчика счетчики бывают: последовательные, параллельные и частичнопараллельные.

Видно, что триггер младшего разряда переключается каждым счетным импульсом, т.е. входом счетчика служит вход этого триггера. Состояния второго и третьего триггеров меняются соответственно каждым вторым и четвертым импульсом. Это обеспечивается последовательным соединением триггеров.

Из правила прибавления к двоичному числу единицы также известно, что изменение значения i-го разряда происходит тогда, когда до прибавления очередной единицы все предыдущие разряды были единицами. Отсюда следует правило: если триггеры имеют прямой счетный вход, то он подключается к инверсному выходу предыдущего триггера; если имеет инверсный вход, то он подключается к прямому выходу.

Иллюстрирующий пример трехразрядного суммирующего счетчика с временными диаграммами работы и условным изображением приведен на рис. 13.27. Счетчик может принимать 8 различных состояний, которые повторяются через каждые 8 входных импульсов (Kn=8). С наибольшей частотой переключается триггер младшего разряда, следовательно, разрешающая способность счетчика определяется временем задержки переключение триггера (Тст=Ттг). Это положение распространяется на все типы двоичных счетчиков.

При подаче на вход вычитающего счетчика одного счетного импульса ранее записанное в нем число уменьшается на единицу.

Принципы построения вычитающих счетчиков основаны на правилах вычитания двоичных чисел и отличаются от принципов построения суммирующих счетчиков лишь тем, что если триггеры имеют прямой вход +1, то его подключают к прямому выходу предыдущего триггера, если вход инверсный, то подключают к инверсному выходу.

5.Шифраторы, дешифраторы

Шифратор — это комбинационное устройств о, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду. Шифратор иногда называют «кодером» (от англ. coder) и используют, например, для перевода десятичных чисел, набранных на клавиатуре кнопочного пульта управления, в двоичные числа. Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением n = 2m, где n — число входов, m — число выходов. Так, для преобразования кода кнопочного пульта в четырехразрядное двоичное число достаточно использовать лишь 10 входов, в то время как полное число возможных входов будет равно 16 (n = 24 = 16), поэтому шифратор 10x4 (из 10 в 4) будет неполным.

Основное назначение шифратора — преобразование номера источника сигнала в код (например, номера нажатой кнопки некоторой клавиатуры).

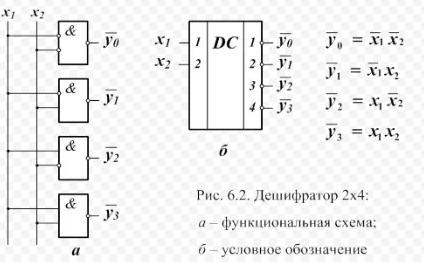

Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. Число входов и выходов в так называемом полном дешифраторе связано соотношением m = 2n, где n — число входов, а m — число выходов. Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет полным, а если бы выходов было только 10, то он являлся бы неполным.

Дешифратор — одно из широко используемых логических устройств. Его применяют для построения различных комбинационных устройств.

Рассмотренные шифраторы и дешифраторы являются примерами простейших преобразователей кодов.

Преобразователями кодов, в общем случае, называют устройства, предназначенные для преобразования одного кода в другой, при этом часто они выполняют нестандартные преобразования кодов. Преобразователи кодов обозначают через X/Y.

Сумматор представляет собой комбинационное цифровое устройство (КЦУ), предназначенное в основном для суммирования двоичных чисел. Кроме того, с помощью сумматора могут выполняться вычитание, умножение, деление, преобразование чисел в дополнительный код и некоторые другие операции. Обычно сумматор состоит только из логических элементов, а результат операции направляется затем для записи в регистр. Классификация сумматоров может быть проведена по трем основным признакам:числу входов (полусумматоры, одноразрядные и многоразрядные сумматоры). Многоразрядные сумматоры, в свою очередь, подразделяются на последовательные и параллельные; последние по способу организации межразрядных переносов подразделяются на сумматоры с последовательным и параллельным переносом и с групповой структурой; пособу тактирования (синхронные и асинхронные сумматоры);системе счисления (двоичные, двоично-десятичные и др.). П олусумматорами (рис. 4.8, 4.9) называют КЦУ с двумя входами (а, b)и двумя выходами, на одном из которых вырабатывается сигнал суммы (выход S),а на другом – сигнал переноса (выход Р).

| Рис. 4.8. Условное обозначение полусумматора | Рис. 4.9. Схема полусумматора на логических элемента |

Одноразрядным сумматором (рис. 4.10, 4.11) называют КЦУ с тремя входами и двумя выходами. Кроме двух входов для чисел он имеет третий вход, на который подается сигнал переноса из предыдущего разряда. Одноразрядный сумматор является основным элементом многоразрядных сумматоров. Он выполняет арифметическое сложение одноразрядных двоичных чисел ai и bi и перенос Pi- 1 из предыдущего разряда с образованием на выходе суммы Si и переноса Pi в старший разряд (табл. 4.6). Аналогичным способом могут быть построены логические схемы вычитателей. Как сумматоры, так и вычитатели предназначены для выполнения основных арифметических операций – сложения и вычитания. Имея на входе дополнительные средства для изменения знака второго аргумента, сумматор может прибавлять к первому слагаемому второе с измененным знаком,

т.е. вычитать, а вычитатель – вычитать из уменьшаемого вычитаемое с измененным знаком, т.е. прибавлять. Таким образом, в арифметико-логических устройствах (АЛУ) в большинстве случаев используется только один из двух рассматриваемых узлов, традиционно – именно сумматор, хотя по всем показателям вычитатель подобен сумматору.

| Рис. 4.10. Условное обозначение одноразрядного сумматора | Рис. 4.11. Схема одноразрядного сумматора на логических элементах |

Операции сложения и вычитания бывают последовательными и параллельными. В данном случае под последовательностью понимается поочередное, разряд за разрядом, сложение (или вычитание) на одноразрядной схеме с задержкой переносов (или займов) для использования их как третьих аргументов в следующем такте, т. е. в разряде.

При параллельных сложениях (или вычитаниях) используются столько одноразрядных сумматоров (или вычитателей), сколько разрядов в исходных числах (точнее – сколько разрядов в самом большом из них числе). Эти одноразрядные сумматоры взаимодействуют между собой по цепям переносов (или займов). Очевидно, что полный параллелизм при этом не достигается, так как переносы и займы распространяются с некоторой, хотя и небольшой, задержкой от младших разрядов к старшим. Имеется в виду схемное распространение займа в отличие от логического, направленного в противоположную сторону. Проблема сокращения времени распространения переносов (или займов) по разрядам – одна из главных при проектировании АЛУ. Отметим некоторые особенности логики работы сумматоров и вычитателей: сумма равна 1, если единичные значения принимает нечетное число аргументов; выходной перенос равен 1, если единичные значения принимают больше двух аргументов; разность равна 1, если при отсутствии входного займа из 1 вычитается 0 или из 0 вычитается 1; она также равна 1, если аргументы равны при наличии входного займа. Выходной заем равен 1, если из 0 вычитается 1, а также если аргументы равны при наличии входного займа.

структуре АЛУ часто присутствует накопительный блок, состоящий из комбинационного сумматора (или вычитателя) и регистра результата. Подобный блок необходим при реализации последовательного алгоритма вычислений, когда вновь поступающий аргумент прибавляется к ранее накопленному результату или из него вычитается, а новый результат вычислений заменяет исходный. Функцию накопительного блока, сочетающего функции сумматора (или вычитателя) и регистра, может выполнять набор Т -триггеров, работающих в режиме инверсии состояния, т.е. сложения по модулю 2. Такой сумматор на основе T -триггеров называют накопительным. Он уже является не комбинационным устройством, а конечным автоматом, поскольку обладает памятью. перации сложения (или вычитания) с учетом переноса (или займа) выполняются всегда над тремя аргументами, поэтому накопительный сумматор (или вычитатель) должен содержать управляющие коммутационные схемы, чтобы разнести сложение (или вычитание) на два такта. В этом состоит главный его недостаток. В остальном накопительный сумматор (или вычита-

тель) – самый простой и экономичный. Помимо несложных коммутационных схем он содержит дополнительно только цепи переноса (или займа).

Булевы функции, описывающие работу одноразрядного двоичного сумматора (по табл. 4.6), можно записать в следующем виде:

Для обработки многоразрядных чисел объединяется соответствующее число одноразрядных сумматоров. При этом отдельные разряды обрабатываемых чисел А и В подаются на входы ai и bi. На вход Pi подается перенос из предыдущего, более младшего разряда. Формируемый в данном разряде перенос Pi+ 1 передается в следующий, более старший разряд. Такая организация процесса формирования переноса, называемая последовательным переносом, снижает быстродействие многоразрядного сумматора, так как получение результата в старшем разряде сумматора обеспечивается только после завершения распространения переноса по всем разрядам. Поэтому иногда организуется параллельный перенос.

Что такое триггеры?

Триггер (от английского “тrigger”) – цифровое устройство, которое может иметь всего два (0 или 1) устойчивых состояния. При этом переход из одного состояния в другое осуществляется максимально быстро, временем переходным процессов на практике принято пренебрегать. Триггеры – это основной элемент для построения различных запоминающих устройств. Их можно использоваться для хранения информации, но объем их память чрезвычайно мал – триггер может хранить биты, отдельные коды или сигналы.

Рис. 1. JK-триггер

Триггеры способны сохранять свою память только при наличии питающего напряжения. Именно по этому их принято относить к оперативной памяти. Если выключить питающее напряжение и затем его снова включить, триггер переходит в случайное состояние – он может иметь на выходе как логический ноль, так и логическую единицу. Именно поэтому, проводя проектирование схем, надо обязательно предусмотреть вопрос приведения триггера в начальное («стартовое») состояние, исход из которого и проводится дальнейший расчет.

В основу построения любого триггера положена схема, которая состоит из двух логических (И-НЕ или ИЛИ-НЕ), которые охватываются обратной положительной связью. В результате такого подключения схема может пребывать исключительно в одном (из двух возможных) устойчивых состояний. При этом в этом состоянии, если не приходят другие управляющие сигналы, схема может находиться по времени практически без ограничений – пока есть питающее напряжение.

На рисунке ниже приводится пример подобной схемы – триггерной ячейки, созданной на основе 2 элементов И-НЕ

Рис.2. Пример схемы триггерной ячейки

Как видно, схема имеет 2 инверсных входа: сброс – обозначен на схеме R (сокращение от англ. Reset) и установка – обозначен S (сокращенно от Set), а так же два выхода: прямой, обозначенный Q и инверсный, обозначенный как – Q. Для правильной и стабильной работы триггерной ячейки должно соблюдаться одно правило – на ее входы не могут поступать одновременно отрицательные импульсы. Когда на вход –R поступает импульс при единичном сигнале на входе -S, выход переходит в состояние единиц