Организация блоков АЦП, ОЗУИ, ПЗУ трудности не представляет. Они выполняются по стандартным решениям. Остановимся на проектировании ВУ. Оно должно на каждом кадре осуществлять формирование координат точек области U, вычисление функций корреляции R в каждой из этих точек, для чего необходимо вычислять адреса точек исходного и эталонного изображений, находить минимальные значения функции корреляции и координат точки.

Внешний интерфейс ВУ:

D1 ¾ информационная шина с ОЗУИ;

D2 ¾ информационная шина с ПЗУ;

"Пуск", "Ост" ¾ линии для передачи сигналов "Пуск" и "Останов" с ПУ; EW ¾ линия передачи сигнала EW с блока AЦП; Хцн, Yцн ¾ шины ввода начальных координат; A1 ¾ шина адреса на ОЗУИ; A2 ¾ шина адреса на ПЗУ; X,Y ¾ шины координат X и Y.

Определим внутренние запоминающие элементы: регистры Xц, Yц и Xт, Yт ¾ для хранения координат соответственно центра и точек области U; X’т Y’т ¾ для хранения текущих координат точек "окна" вычисления функции R; AC ¾ для формирования текущего значения функции R; Rmin ¾ регистр минимального значения функции корреляции; m, n ¾ для хранения размеров "окна"; r, p ¾ для хранения размеров области U; Q ¾ рабочий регистр; счётчики k, l ¾ для организации циклов сканирования области U; i, j ¾ для организации циклов сканирования "окна" вычисления функции R.

Так как m = n и r = p, то необходимо иметь только по одному регистру (m и r).

Определим разрядность регистров.

Все регистры координат имеют одну разрядность, определяемую как  . В данном случае разрядность должна быть равна 7. Так как организация микросхем такова, что разрядность кратна 2, выбираем разрядность регистров Xц, Yц, Xт, Yт, X’т, Y’т равной 8.

. В данном случае разрядность должна быть равна 7. Так как организация микросхем такова, что разрядность кратна 2, выбираем разрядность регистров Xц, Yц, Xт, Yт, X’т, Y’т равной 8.

Разрядность АС, Rmin определяется максимально возможным значением функции корреляции. Максимальное значение получается, если яркости всех точек в "окне" исходного изображения максимальны ( - 1), а яркости всех точек эталонов - минимальны (0).

- 1), а яркости всех точек эталонов - минимальны (0).

В этом случае максимальное значение равно  .

.

Следовательно, необходимо иметь 14 разрядов. Принимаем разрядность регистров АС и Rmin равной 1 Разрядность регистра Q может быть равна 8.

Количество разрядов регистров m, r и счётчиков k, l и i, j равно соответственно  и

и  , т. е. четырём и трём.

, т. е. четырём и трём.

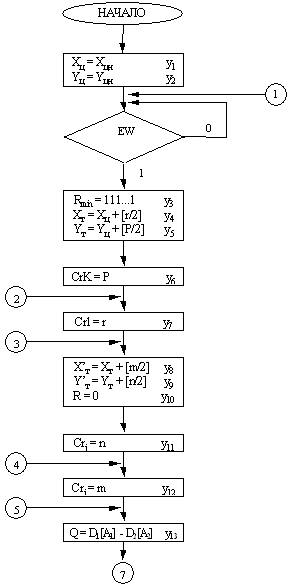

Шина A1 формируется из выходов регистров X’т и Y’т, а шина A2 ¾ из i и j. Алгоритм функционирования ВУ показан на рис. 2.

В зависимости от требований к аппаратурным затратам и быстродействию данный алгоритм может быть реализован различными способами. По аппаратурным затратам самой экономичной является реализация, при которой все операции над регистрами выполняются на одном блоке обработки.

Однако при этом все операции выполняются последовательно и значит, быстродействие самое низкое.

Самой быстродействующей является реализация, при которой все возможные для совмещения операции выполняются на своих блоках обработки.

Исходя из алгоритма, можно выделить следующие параллельно работающие блоки:

n арифметический (АР);

n формирование координаты Х адреса (АХ);

n формирование координаты Y адреса (AY);

n счётчиков (СК);

n управления (БУ).

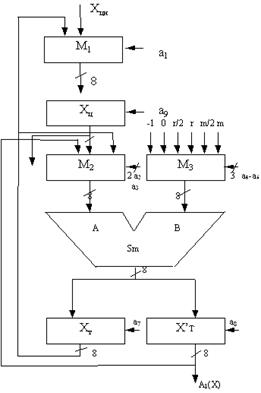

Блоки АР, АХ, AY, СК образуют операционный блок. Структурная схема для такого разделения изображена на рис. 3.

Арифметический блок выполняет микрокоманды Y3, Y10, Y14, Y15, Y29, Y21.

Блок формирования координаты АХ выполняют микрокоманды Y1, Y4, Y8, Y16, Y19, Y30,Y23, Y25.

Блок формирования координаты AY аналогичен блоку АХ и служит для выполнения микрокоманд Y2, Y5, Y9, Y18, Y22, Y2

Блок счётчиков служит для организации циклов и выполняет микрокоманды Y6, Y7, Y11, Y12, Y17, Y20, Y24, Y27.

Блок управления предназначен для формирования управляющих сигналов аi, подаваемых на все блоки, для организации условных и безусловных переходов. Условные переходы производятся по сигналам: внешних условий (Х1), арифметического блока (Х2), с блока счётчиков (Х3 - Х6).

Рисунок 2 ¾ Алгоритм функционирования ВУ

Рисунок 2 ¾ Окончание рисунка

Рисунок 3 ¾ Структурная схема оптимальной реализации

На рис. 4. показан пример организации арифметического блока (М1 и М2 ¾ мультиплексоры; АЛУ ¾ арифметико-логическое устройство; ai ¾ управляющие сигналы).

Рисунок 4 ¾ Организация арифметического блока

Блок управления может выдавать на каждый из блоков код микрокоманды, который с помощью дешифратора переводится в набор управляющих сигналов ai. Организация блока AX(AY) показана на рис. 5, а схема блока счётчиков на рис. Определим теперь для такой реализации время выполнения алгоритма, показанного на рис.2.

Т = [(((4m+3)n+6)r+3)p+4] tц,

где tц - время одного цикла.

Время цикла определяется временем прохождения сигналов по самому длинному пути среди всех блоков. В рассматриваемом устройстве таким путём является: чтение данных из ОЗУИ и ПЗУ, прохождение через мультиплексоры М1 и М2 арифметического блока, выполнение операции на АЛУ и запись в регистр Q.

Рисунок 5 ¾ Организация блока формирования координаты

В этом случае время цикла:

tц = tчт + tм + tАЛУ + tQ.

При построении устройства на элементах ТТЛШ логики может быть порядка 200 нс.

Если ввести конвейерные регистры на выходах ОЗУИ и ПЗУ, то время цикла можно уменьшить в два раза.

Для tц = 200 нс; Т = 5,4 мс.

Рисунок 6 ¾ Организация блока счётчиков