Последовательные порты предназначены для обмена информацией между

микропроцессорами, а также между микропроцессорами и внешними уст-

ройствами, если критично количество соединительных проводов. В на-

стоящее время широко используются два вида последовательных портов:

· синхронные последовательные порты;

· асинхронные последовательные порты.

Синхронные последовательные порты

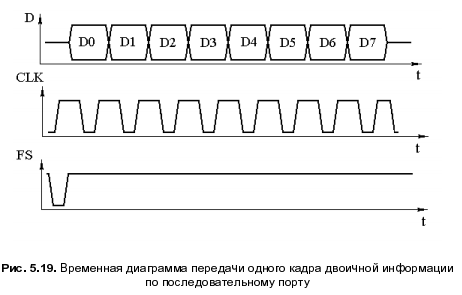

При рассмотрении работы параллельного порта в режиме обмена данными с другим компьютером или принтером уже рассматривался режим

последовательной передачи байтов. В последовательном порте режим

последовательной передачи применяется не только к байтам, но и к от-

дельным битам внутри байта. В этом случае для передачи данных достаточно только одного провода. Передаваемая и принимаемая информация обычно представляется в виде однобайтовых или многобайтовых

слов. Вес каждого бита в слове различен, поэтому кроме битовой синхронизации, аналогичной байтовой синхронизации для параллельного

порта, требуется кадровая синхронизация. Она позволяет однозначно

определять номер каждого бита в передаваемом слове. Временная диаграмма передачи кадра по синхронному последовательному порту при-

ведена на рис. 5.19.

Временная диаграмма передачи одного кадра двоичной информации

по последовательному порту

Такая временная диаграмма характерна для синхронных последовательных портов, которые используются чаще всего в сигнальных процессо-

рах для обмена информацией с кодеками речи, аналого-цифровыми и

цифроаналоговыми преобразователями. На временной диаграмме показаны два синхросигнала: тактовой синхронизации CLK и кадровой синхронизации FS. Кадровый синхросигнал формируется аппаратно из сигнала WR# при записи очередного байта в параллельный порт вывода.

Полярность сигналов синхронизации зависит от конкретного типа при-

меняемых микросхем, поэтому в большинстве последовательных портов

возможна настройка полярности сигналов синхронизации.

Упрощенная схема синхронного последовательного порта приведена на

рис. 5.20. В состав последовательного порта входит универсальный по-

следовательно-параллельный регистр, подключенный к системной шине.

Он обеспечивает преобразования параллельного кода, поступающего с

системной шины в последовательный. При обращении центрального

процессора к последовательному порту вырабатывается сигнал записи в

последовательный порт WR#, который через дешифратор подается на

вход параллельной записи V универсального регистра. Этот же сигнал

используется в качестве кадрового синхросигнала FS. Тактовый синдром-

сигнал CLK, вырабатываемый отдельным генератором, подается на вход

последовательного сдвига С универсального регистра, входящего в со-

став порта.

Рис. 5.20. Упрощенная схема синхронного последовательного порта

В синхронном последовательном порте информация передается непрерывно, что, конечно, удобно для устройств с непрерывным потоком ин-

формации, как, например, в кодеках речи. Но существуют устройства, к

которым необходимо обращаться только периодически, как, например,

синтезаторы частоты, микросхемы приемников, блоков цветности телевизоров, микросхем памяти данных и многие другие устройства. В этих

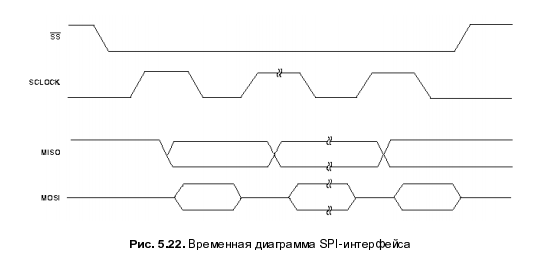

случаях используются другие виды синхронных последовательных портов, такие как SPI и I2С. Временная диаграмма сигналов SPI-интерфейса

приведена на рис. 5.22.

Рис. 5.22. Временная диаграмма SPI-интерфейса

Основное отличие этого интерфейса от приведенного выше заключается

в том, что сигнал тактовой синхронизации передается только в момент

действия импульса кадровой синхронизации. Активный уровень сигнала

кадровой синхронизации длится до окончания передачи последнего бита

в передаваемом кадре. По одним и тем же линиям передачи данных:

MISO (вход для главного, выход для ведомого); и MOSI (выход для

главного, вход для ведомого), может передаваться информация к совершенно различным микросхемам. Выбор среди микросхем, подключенных

к одному и тому же порту, той, для которой предназначена информация,

производится сигналом SS (выбор ведомого). В SPI-интерфейсе в приемнике не требуется счетчик тактовых импульсов. Запись принятой информации в параллельный регистр данных производится по окончанию кадрового импульса.

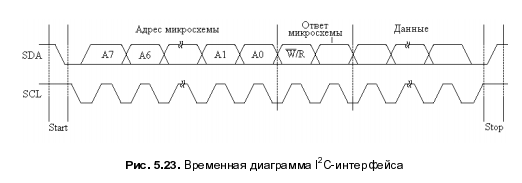

Если в устройстве используется много микросхем, то в SPI-интерфейсе

количество линий выбора ведомого становится значительным, поэтому в

таких случаях используется еще один вид синхронного последовательно-

го интерфейса: 12С. Временная диаграмма этого интерфейса приведена на

рис. 5.23. В PC-интерфейсе прием и передача данных, а также передача

адреса микросхемы и адреса регистра внутри микросхемы, к которому

осуществляется обращение, производятся по одной и той же линии данных SDA. Для подключения к этой линии используются микросхемы с

открытым коллектором. Нагрузкой для всех микросхем, подключенных

к линии SDA, служит внешний резистор. Естественно, что скорость передачи данных по такому интерфейсу будет ниже, чем в случае SPI.

Адрес микросхемы

Рис. 5.23. Временная диаграмма I2С-интерфейса

Сигнал тактовой синхронизации в I2С-шине передается по линии SCL.

Начало работы с микросхемой обозначается особой комбинацией сигналов SDA и SCL (переход 0-1 SDA при высоком уровне SCL), которая называется условием старта. Эта же комбинация одновременно осуществляет кадровую синхронизацию. Завершение работы с микросхемой

обозначается еще одной комбинацией сигналов SDA и SCL — переходом

0-1 SDA при высоком уровне SCL. В качестве примера микросхем, использующих интерфейс 12С, можно назвать микросхемы EEPROM серии

24сХХ.

Асинхронные

Последовательные порты

Рассмотренные синхронные последовательные порты позволяют достиг-

нуть больших скоростей передачи данных, но линия, по которой ведется

передача синхросигнала, практически не несет информации. Такой сиг-

нал можно было бы сформировать и на приемном конце линии передачи,

если заранее договориться о скорости передачи.

В настоящее время используются стандартные скорости передачи, крат-

ные скорости 1200 бит/с. При этом масштабирование может проводиться

как в сторону увеличения скорости обмена, так и в сторону уменьшения

скорости обмена двоичной информацией. Например, стандартной скоро-

стью передачи последовательного порта будет скорость 2400 и 4800 бит/с.

Стандартными же будут скорости обмена 600 и 300 бит/с.

Проблема, возникающая при таком способе обмена данными, — это не-

возможность добиться от двух внутренних генераторов, осуществляющих

синхронизацию передачи данных на приемном и передающем концах

линии, одинаковой частоты и фазы генерируемых сигналов. Проблема

решается принудительной синхронизацией тактового генератора на при-

емном конце при помощи особого условия начала асинхронной переда-

чи — стартового бита.

Все время, пока не ведется передача информации, на линии присутствует

стоп-сигнал единичного уровня. Перед началом передачи каждого байта

передается старт-бит, сигнализирующий приемнику о начале посылки

данных, за которым следуют информационные биты. Стартовый бит

всегда передается нулевым уровнем с длительностью, как у информационных битов.

Внутренний генератор синхронизации приемника использует счетчик-

делитель опорной частоты, обнуляемый в момент приема начала старт-

бита. Этот счетчик генерирует внутренние стробы, по которым приемник

фиксирует последующие принимаемые биты. В идеале стробы располагаются в середине битовых интервалов, что позволяет принимать данные

и при незначительном рассогласовании скоростей приемника и передатчика. Очевидно, что при передаче 8 битов данных, одного контрольного

и одного стоп-бита предельно допустимое рассогласование скоростей,

при котором данные будут распознаны верно, не может превышать 5%.

В некоторых случаях после передачи битов данных может передаваться

бит паритета (четности). Завершается передача данных стоп-сигналом.

Минимальная длительность стопового сигнала должна быть 1,5 длительности информационных битов, но обычно используют паузу между

соседними пакетами данных, равную двум длительностям информационного бита.

Временная диаграмма сигналов при асинхронной передаче данных при-

ведена на рис. 5.24.

Рис. 5.24. Временная диаграмма сигналов при асинхронной передаче

Формат асинхронной посылки позволяет выявлять следующие возможные ошибки передачи:

если принят перепад, сигнализирующий о начале посылки, а по стробу старт-бита зафиксирован уровень логической единицы, то старт- бит считается ложным и приемник снова переходит в состояние ожидания. Об этой ошибке приемник может и не сообщать;

если во время, отведенное под стоп-бит, обнаружен уровень логического нуля, то фиксируется ошибка стоп-бита;

если применяется контроль четности, то после посылки битов данных

передается контрольный бит. Он дополняет количество единичных

битов данных до четного или нечетного в зависимости от принятого

соглашения. Прием байта с неверным значением контрольного бита

приводит к фиксации ошибки.

Наиболее распространенным в настоящее время является последовательный асинхронный порт, работающий по стандарту RS-232. Временная

диаграмма этого порта приведена на рис. 5.25. Используются уровни

сигналов НОВ, что позволяет контролировать обрыв линии.

Рис. 5.25. Временная диаграмма сигналов интерфейса RS-232

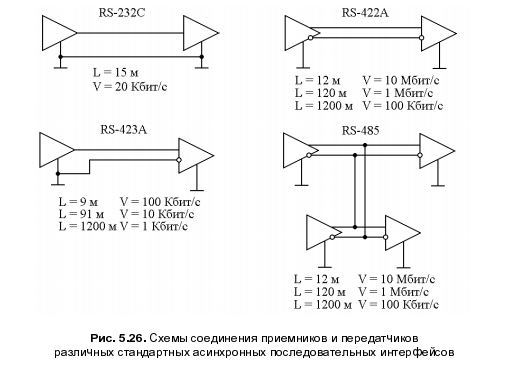

Существует ряд международных стандартов на асинхронные последовательные интерфейсы: RS-232C, RS-423A, RS-422A и RS-485. На рис. 5.26

приведены схемы соединения приемников и передатчиков, а также показаны ограничения на длину линии (L) и максимальную скорость передачи данных (V) по этим интерфейсам.

Несимметричные линии интерфейсов RS-232C и RS-423A имеют самую

низкую защищенность от синфазной помехи, хотя дифференциальный

вход приемника RS-423A несколько смягчает ситуацию. Лучшие пара-

метры имеет двухточечный интерфейс RS-422A и его магистральный

(шинный) аналог RS-485, работающие на симметричных линиях связи.

В них для передачи каждого сигнала используются дифференциальные

сигналы с отдельной (витой) парой проводов.

Рис. 5.26. Схемы соединения приемников и передатчиков

различных стандартных асинхронных последовательных интерфейсов

Последовательный асинхронный порт, работающий по стандартам RS-

232, RS-423A и RS-422A, позволяет соединять между собой только два

устройства. Это связано с тем, что при параллельном соединении двух

передатчиков их выходные каскады могут выйти из строя. В ряде случаев

требуется объединить несколько устройств. Для того чтобы выходные

каскады передатчиков последовательных портов не выходили из строя,

необходимо применять специальные меры, которые обсуждались в предыдущих главах. Эти меры реализованы в интерфейсе RS-485.