Генераторы с кварцевой стабилизацией частоты

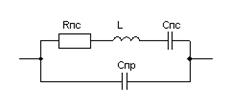

Существенное уменьшение нестабильности генераторов может быть достигнуто за счет использования кварцевого резонатора, который представляют собой особым образом вырезанную и отшлифованную пластину натурального или искусственного кварца. Кварц - пьезоэлектрик, поэтому упругие колебания кристалла могут быть вызваны приложением электрического поля, а эти колебания, в свою очередь, генерируют напряжение на гранях кристалла. В этом случае кристалл ведет себя как RLC-элемент, эквивалентная схема которого приведена на рис.1.4.

Рисунок 1.4 - Эквивалентная схема замещения кварцевого резонатора

RC – генераторы

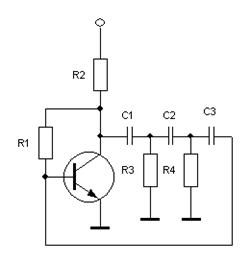

В генераторах этого типа баланс фаз достигается за счет специальной фазосдвигающей RC – цепи, устанавливаемой в цепи обратной связи. Схема простейшего RС-генератора на транзисторе приведена на рис.1.7.Трехзвенная RC-цепь на частоте квазирезонанса обеспечивает сдвиг фазы, равный 1800. Схема с общим эмиттером, на которой собран генератор, изменяет фазу сигнала на выходе по отношению ко входному также на 1800, т.е. суммарный фазовый сдвиг равен  , за счет чего выполняется условие баланса фаз. При условии С1=С2=С3=С и R3=R4=RвхVT = R коэффициент передачи трехзвенной RC-цепи равен примерно 1/29, поэтому, если коэффициент усиления транзисторного каскада КU< 29, в схеме возникают колебания с частотой

, за счет чего выполняется условие баланса фаз. При условии С1=С2=С3=С и R3=R4=RвхVT = R коэффициент передачи трехзвенной RC-цепи равен примерно 1/29, поэтому, если коэффициент усиления транзисторного каскада КU< 29, в схеме возникают колебания с частотой

Рисунок 1.7 – RC-генератор на транзисторе

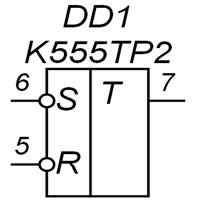

18) RS-триггер, или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы.

При подаче единицы на вход S выходное состояние становится равным логической единице. А при подаче единицы на вход R выходное состояние становится равным логическому нулю.

Схема синхронного RS-триггера совпадает со схемой одноступенчатого парафазного (двухфазного) D-триггера, но не наоборот, так как в парафазном (двухфазном) D-триггере не используются комбинации S=0, R=0 и S=1, R=1.

Алгоритм функционирования синхронного RS-триггера можно представить формулой.

D-триггер (D от 0%90%D0%BD%D0%B3%D0%BB%D0%B8%D0%B9%D1%81%D0%BA%D0%B8%D0%B9_%D1%8F%D0%B7%D1%8B%D0%BA"англ. delay — задержка0%A2%D1%80%D0%B8%D0%B3%D0%B3%D0%B5%D1%80"[13]HYPERLINK "https://ru.wikipedia.org/wiki/%D0%A2%D1%80%D0%B8%D0%B3%D0%B3%D0%B5%D1%80"[14]HYPERLINK "https://ru.wikipedia.org/wiki/%D0%A2%D1%80%D0%B8%D0%B3%D0%B3%D0%B5%D1%80"[15] либо от data0 %A 2 %D 1 %80%D 0 %B 8 %D 0 %B 3 %D 0 %B 3 %D 0 %B 5 %D 1 %80"[16] - данные) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Вход синхронизации С может быть статическим (потенциальным) и динамическим. У триггеров со статическим входом С информация записывается в течение времени, при котором уровень сигнала C=1.

Синхронный Т-триггер0 %A 2 %D 1 %80%D 0 %B 8 %D 0 %B 3 %D 0 %B 3 %D 0 %B 5 %D 1 %80"[17], при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер можно построить на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе.

JK-триггер0 %A 2 %D 1 %80%D 0 %B 8 %D 0 %B 3 %D 0 %B 3 %D 0 %B 5 %D 1 %80"[18]HYPERLINK "https://ru.wikipedia.org/wiki/%D0%A2%D1%80%D0%B8%D0%B3%D0%B3%D0%B5%D1%80"[19] работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное, то есть выполняется операция инверсии. Вход J (от 0%90%D0%BD%D0%B3%D0%BB%D0%B8%D0%B9%D1%81%D0%BA%D0%B8%D0%B9_%D1%8F%D0%B7%D1%8B%D0%BA"англ. Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (от 0%90%D0%BD%D0%B3%D0%BB%D0%B8%D0%B9%D1%81%D0%BA%D0%B8%D0%B9_%D1%8F%D0%B7%D1%8B%D0%BA"англ. Kill — отключение) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю.

19) Классификация вычислительных машин по принципу действия:

Цифровые вычислительные машины (ЦВМ) - вычислительные машины дискретного действия, работают с информацией, представленной в дискретной, а точнее, в цифровой форме.

Аналоговые вычислительные машины (АВМ) - вычислительные машины непрерывного действия, работают с информацией, представленной в непрерывной (аналоговой) форме, т.е. в виде непрерывного ряда значений какой-либо физической величины (чаще всего электрического напряжения)

Гибридные вычислительные машины (ГВМ) - вычислительные машины комбинированного действия, работают с информацией, представленной и в цифровой, и в аналоговой форме; они совмещают в себе достоинства АВМ и ЦВМ. ГВМ целесообразно использовать для решения задач управления сложными быстродействующими техническими комплексами.

Классификация ЭВМ по назначению.

Универсальные ЭВМ предназначены для решения самых различных инженерно-технических задач: экономических, математических, информационных и других задач, отличающихся сложностью алгоритмов и большим объемом обрабатываемых данных. Они широко используются в вычислительных центрах коллективного пользования и в других мощных вычислительных комплексах.

Проблемно-ориентированные ЭВМ служат для решения более узкого круга задач, связанных, как правило, с управлением технологическими объектами; регистрацией, накоплением и обработкой относительно небольших объемов данных; выполнением расчетов по относительно несложным алгоритмам; они обладают ограниченными по сравнению с универсальными ЭВМ аппаратными и программными ресурсами.

Специализированные ЭВМ используются для решения узкого круга задач или реализации строго определенной группы функций. Такая узкая ориентация ЭВМ позволяет четко специализировать их структуру, существенно снизить их сложность и стоимость при сохранении высокой производительности и надежности их работы.

20) Применение МП позволило создать новый класс вычислительной техники - микропроцессорные системы.

Центральное место в этой структуре занимает микропроцессор, который выполняет арифметические и логические операции над данными, осуществляет программное управление процессом обработки информации, организует взаимодействие всех устройств, входящих в систему. Работа МП происходит под воздействием сигналов схемы синхронизации и начальной установки, часто выполняемой в виде отдельного кристалла.

В состав МПС, как правило, входят:

- шинный контролер для сопряжения устройств с системной шиной по параллельному интерфейсу;

- адаптер последовательного интерфейса для построения многопроцессорных систем или сопряжения источников и приемников сигналов, не увеличивающих нагрузку на системный интерфейс;

- специализированный процессор арифметической обработки сигналов (сопроцессор);

- ПЗУ команд и констант;

- ОЗУ операндов.

В рассматриваемых структурах МПС реализуются три способа организации (обслуживания) передачи информации:

1) программно-управляемая передача, инициируемая процессором;

2) программно-управляющая передача, инициируемая запросом прерывания от периферийного устройства;

3) прямой доступ к памяти (ПДП).

21) Микропроцессор — это центральный блок персонального компьютера, предназначенный для управления работой всех остальных блоков и выполнения арифметических и логических операций над информацией.

Микропроцессор выполняет следующие основные функции:

чтение и дешифрацию команд из основной памяти;

чтение данных из основной памяти и регистров адаптеров внешних устройств;

прием и обработку запросов и команд от адаптеров на обслуживание внешних устройств;

обработку данных и их запись в основную память и регистры адаптеров внешних устройств;

выработку управляющих сигналов для всех прочих узлов и блоков компьютера.

В состав микропроцессора входят следующие устройства.

1. Арифметико-логическое устройство предназначено для выполнения всех арифметических и логических операций над числовой и символьной информацией.

2. Устройство управления координирует взаимодействие различных частей компьютера. Выполняет следующие основные функции:

3. Микропроцессорная память предназначена для кратковременного хранения, записи и выдачи информации, используемой в вычислениях непосредственно в ближайшие такты работы машины. Микропроцессорная память строится на регистрах и используется для обеспечения высокого быстродействия компьютера, так как основная память не всегда обеспечивает скорость записи, поиска и считывания информации, необходимую для эффективной работы быстродействующего микропроцессора.

4. Интерфейсная система микропроцессора предназначена для связи с другими устройствами компьютера.

Важнейшими характеристиками микропроцессора являются:

тактовая частота. Характеризует быстродействие компьютера. Режим работы процессора задается микросхемой, называемой генератором тактовых импульсов.

• разрядность процессора — это максимальное количество разрядов двоичного числа, над которым одновременно может выполняться машинная операция.