Регистром называется устройство, предназначенное для хранения многоразрядных двоичных слов.

Основу регистров составляют триггеры, количество которых равно числу разрядов в двоичном слове.

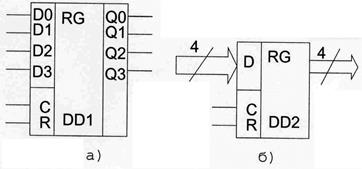

Рис. 20.1

Обозначения регистров представлены на рис. 20.1. Типовыми внешними связями регистров являются:

- информационные входы (входы данных) Di;

- вход синхронизации С;

- вход сброса (обнуления) R;

- выходы Qi.

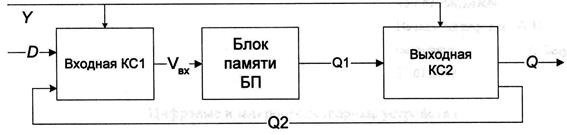

Рис 8.321 Структурная схема регистров

D - входы n-разрядного слова;

Y - совокупность управляющих сигналов, в каждом устройстве заменяются на R, S, D, T, J, K, C – обозначения соответствующих сигналов;

– функции возбуждения триггеров;

– функции возбуждения триггеров;

Q, Q1, Q2, - выходные сигналы регистра.

Характерные операции (микрооперации), реализуемые регистрами:

-прием информации (в регистре запоминается информационное слово);

-установка (запись в регистр константы);

-выдача информации (управление прохождения информации с выходов регистра);

-сдвиг (смещение информации на заданное количество разрядов).

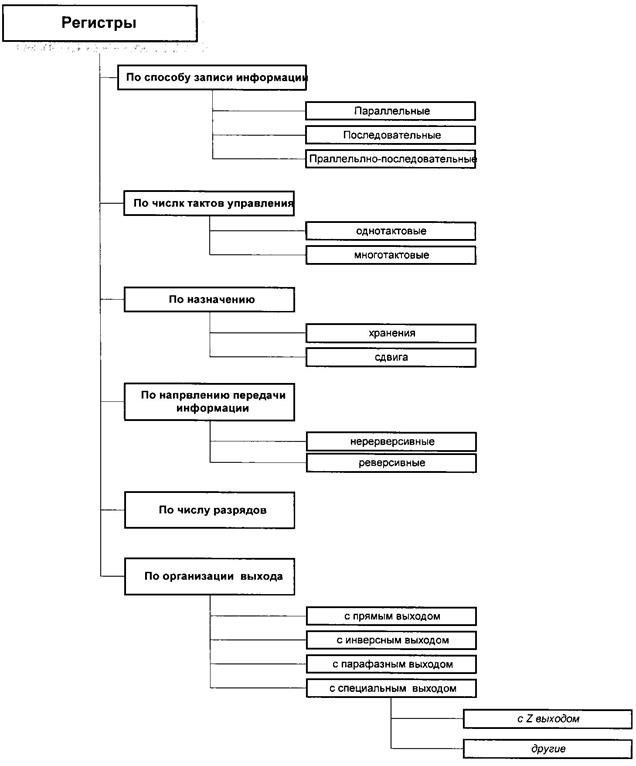

Классификация регистров

Рис 22

Параллельные регистры

В параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения выхода или приема, то есть цепи управления. Пример схемы статического регистра, построенного на триггерах типа D с прямыми динамическими входами, имеющего входы сброса и выходы с третьим состоянием, управляемые сигналом EZ.

Сдвигающие (последовательные) регистры

Последовательные регистры, или регистры сдвига, предназначены для выполнения операций сдвига двоичной информации под действием внешних синхроимпульсов.

По направлению сдвига регистры различаются по трём признакам:

– регистры, выполняющие сдвиг числа от младших разрядов к старшим, называются регистрами сдвига вправо;

– регистры, выполняющие сдвиг числа от старших разрядов к младшим, называются регистрами сдвига влево;

– регистры, выполняющие сдвиг числа как вправо, так и влево, – реверсивные регистры сдвига.

Основное назначение регистров последовательного действия – это сдвиг информации, поступающей на вход.

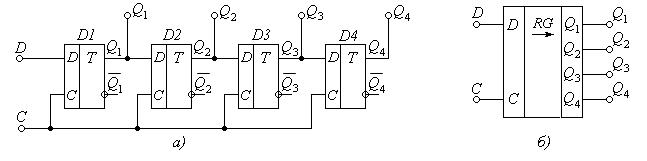

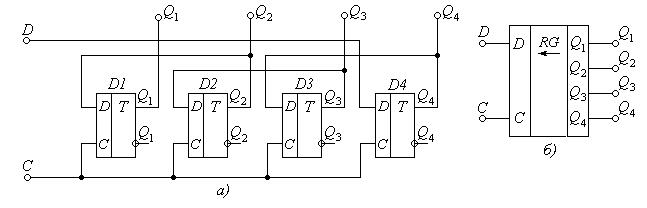

На рис. 23 дана схема и условное обозначение четырёхразрядного регистра сдвига вправо на D -триггерах.

Регистр имеет один информационный вход D, на который поступает информация в виде последовательности нулей и единиц, и тактовый вход С, на который подаются синхронизирующие импульсы.

Регистр сдвига вправо работает следующим образом.

Рисунок 23 – Регистр сдвига вправо: а) схема; б) условное обозначение

На параллельных выходах регистра Q 1 – Q 4 информация появляется одновременно, а на последовательном входе D только поочерёдно по одному биту.

Первый триггер D1 отвечает за младший разряд каждого слова информации, а D4 – за старший. Информация поступает, начиная с младшего разряда.

С поступлением синхронизирующих импульсов одновременно на тактовые входы С всех D -триггеров с каждым фронтом С выход последующего триггера копирует состояние предшествующего.

Регистр из четырёх триггеров или четырёх разрядов может принять информацию, которая состоит из четырёх бит.

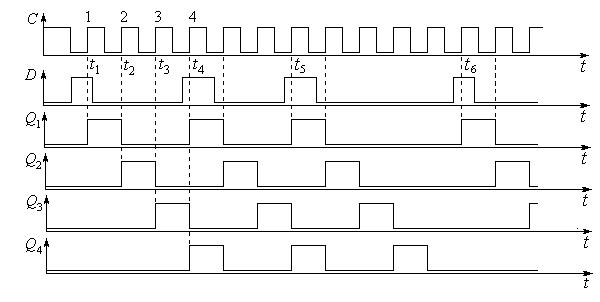

Принцип действия регистра сдвига вправо иллюстрирует временная диаграмма его работы (рис. 24).

Рисунок 24– Временная диаграмма работы регистра сдвига вправо

Для записи информации в данном регистре необходимы четыре такта синхроимпульсов С (1…4).

Считывание информации выходов Q 1, Q 2, Q 3, и Q 4 можно выполнить в параллельном коде одновременно с четырёх названных выходов или в последовательном коде с выхода последнего триггера D4. Пусть к моменту t 1 на информационный D -вход регистра поступила единица. Она подготовит к взводу только триггер 1-го младшего разряда D1. Входы D остальных триггеров D2, D3 и D4 остаются под нулевыми потенциалами. Фронт 1-го синхроимпульса С в момент t 1 взводит триггер D1 и на его выходе будет Q 1 = 1. Эта информация передаётся к входу D триггера D2 и подготавливает триггер D2 к взводу. 2-й синхроимпульс в момент t 2 взводит триггер D2 и тем самым изменяет потенциал на его выходе Q 2 с нуля на единицу. С приходом 3-го синхроимпульса в момент t 3 на выходе Q 3 устанавливается логическая единица. 4-й синхроимпульс в момент t 4 взводит триггер D4 и на его выходе Q 4 потенциал будет равен 1.

25

25

Аналогичным образом записываются и сдвигаются логические единицы, поступившие на D -вход регистра в моменты t 4, t 5, t 6.

Таким образом, в рассмотренной схеме (рис. 23) осуществляется сдвиг логических единиц и нулей, поступивших на D- вход регистра, от младшего разряда к старшему разряду, т.е. вправо.

Для увеличения ёмкости регистров используют их каскадное соединение, как показано на рис. 14.3, при котором выход последнего разрядапредшествующего регистра D1 соединяют с D -входом последующего регистра D2, а входы С объединяют в шину. При этом те же самые выходы последующего регистра D2: Q 1; Q 2; Q 3; Q 4 имеют в соединении другую разрядность: Q 5; Q 6; Q 7; Q 8, т.е. после разряда Q 4 будет разряд Q 5, затем Q 6 и т.д.

Рисунок 26– Регистр сдвига влево: а) схема; б) условное обозначение

Рисунок 26– Регистр сдвига влево: а) схема; б) условное обозначение

Рассматривая типы регистров, следует отметить, что сдвиг информации может быть как вправо, так и влево. Это зависит от того, как поступает информация на D -вход регистра: начиная с младшего разряда регистра или старшего.

На рис. 26 дана схема четырёхразрядного регистра сдвига влево.

Для осуществления сдвига влево D- входом регистра является вход D последнего триггера D4, а выход каждого последующего триггера соединён с D -входом предыдущего.

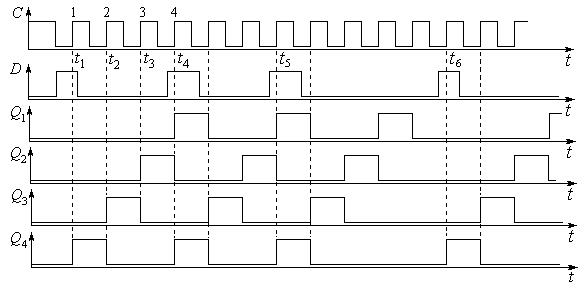

Принцип действия регистра сдвига влево иллюстрирует временная диаграмма его работы (рис. 27).

Рисунок 27 – временная диаграмма регистра сдвига работы влево

Буферные регистры используются для реализации схем фиксации, буферизации и мультиплексирования в микропроцессорных системах на базе различных микропроцессорных наборов.

К этим регистрам, как и ко всем БИС, применяемым в микропроцессорных информационно-управляющих системах, предъявляются следующие обязательные требования:

- наличие Z -состояния на выходах данных;

- наличие входа "выбора микросхемы" (CS) – разрешение реакции

МС на входные управляющие сигналы;

- наличие управляющего входа перевода выходов данных микросхемы в Z -состояние.

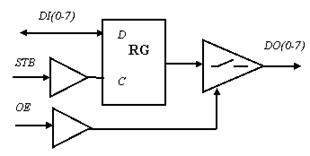

Структурная схема буферного регистра приведена на рис. 9.3.

Рисунок 27 – структурная схема буферного регистра

Запись входных данных в буферные регистры производится при переходе сигнала STB с H -уровня в L -уровень. При H -уровне сигнала OE выходы буферных регистров находятся в высокоимпедансном состоянии.

Вопрос №2