Курсовой проект

По МДК 02.01 Микропроцессорные системы

ПМ.02. Применение микропроцессорных систем, установка и настройка периферийного оборудования

Тема «______________________________»

Выполнил: студент группы КСиК-16

______________________________

Проверилпреподаватель кафедрыЭОИС

______________________________

Якутск 2018

Микропроцессор К1821ВМ85А (18085)

Микропроцессор К1821ВМ85А (ВМ85А) - однокристальный микропроцессор общего применения, являющийся усовершенствованным вариантом первого 8-разрядного микропроцессора фирмы Intel -i8080. Обладая, при относительной простоте, многими чертами и характеристиками, свойственными более производительным современным процессорам, i8085 удобен для изучения в качестве базового, учебного МП. Рассмотренные далее режимы работы процессора: чтения, записи, подтверждения прерываний, прямого доступа к памяти, а также способы его адресации и принципы программирования с некоторыми изменениями могут быть отнесены и ко многим другим микропроцессорам. Таким образом, знание принципов аппаратно-программной организации ВМ85А значительно облегчает освоение и других микропроцессорных БИС.

В настоящее время ВМ85А находит применение в недорогих системах управления различной аппаратурой, при отсутствии высоких требований к ее быстродействию.

Основные характеристики ВМ85А:

разрядность - 8 бит;

тактовая частота - 3 МГц (5 МГц у I8085A-2);

адресуемая память - 64 Кбайт;

подсистема ввода/вывода - 256 байт;

напряжение питания - 5 В;

технология изготовления - n-МОП (5000 тыс. транзисторов);

исполнение - DIP-корпус, 40 выводов;

аналог -i8085А.

Архитектура и интерфейс МП ВМ85А

Большинство МП сами по себе функционально ограничены, поэтому возникает необходимость в применении дополнительных БИС: микросхем ПЗУ, ОЗУ, контроллеров прерываний, прямого доступа в память, адаптеров последовательного и параллельного ВВ и т.д. Сам МП функционирует как элемент микропроцессорной системы. Соединения между элементами внутри системы составляют интерфейс.

Под интерфейсом понимается совокупность унифицированных технических и программных средств, необходимых для подключения данных устройств к системе или одной системы к другой.

Структурная схема МП приведена на рис. 1. Особенностью микропроцессора является наличие совмещенной шины адреса/данных, по которой передается младшая часть адресной информации и 8-разрядные данные.

В состав интерфейса МП ВМ85А входят:

AD7-AD0 Двунаправленная трехстабильная мультиплексированная шина младшей части адреса/данных;

А15-А8 Трехстабильная шина старшей части адреса;

XI, Х2 Входы для подключения внешнего кварцевого резонатора, LC или RC-цепей. Вход X1 может быть использован для приема тактовых импульсов от внешнего задающего генератора.

CLK Выход тактовых импульсов;

RESIN Вход для приема сигнала сброса МП в начальное состояние (RESET IN);

RESET Выходной сигнал системного сброса, синхронизированный с CLK, может использоваться для начальной установки других устройств МС;

SO, SI Состояние МП:

SI S2 Назначение О 0 Halt (останов) О 1 WRITE (запись)

0 READ (чтение)

1 FETCH (выборка команды)

Для фиксации сигналов во внешнем регистре может использоваться спад ALE;

ALE Трехстабильный строб разрешения фиксации адреса (по срезу);

RD/WR Трехстабильные линии вывода стробов чтения и записи;

IO/M Трехстабильная линия выбора памяти или устройств ВВ;

READY Вход для приема сигналов подтверждения обмена при чтении/записи информации;

INTR Вход для приема запроса прерывания, может быть запрещен программно;

INTA Выход подтверждения прерывания; генерируется в ответ на запрос по входу INTR и используется аналогично сигналу RD для чтения вектора прерывания, выставленного внешним устройством на ШД;

RST 5.5

RST 6.5

RST 7.5 Входы (в порядке увеличения приоритета) для принятия запросов типа RST n; приоритет входов выше, чем у INTA, прерывания могут быть запрещены независимо друг от друга;

TRAP Вход немаскируемого запроса прерывания (не может быть запрещен программно), имеет наивысший приоритет;

SID, SOD Вход и выход последовательной передачи данных;

HOLD Вход для приема запроса на захват шины;

HLDA Линия подтверждения захвата шины, активизируется в ответ на сигнал HOLD.

Рис. 1. Структурная схема микропроцессора ВМ85А

Схема МП (рис. 1) содержит следующие функциональные блоки: 8-разрядное арифметико-логическое устройство (ALU); аккумулятор (АC); регистр признаков (флагов) (RF); регистр временного хранения (TR); регистр команд (IR); блок регистров (шесть регистров общего назначения B-L; два буферных регистра W,Z; указатель стека SP, счетчик команд и регистр адреса со схемой инкремента/декремента INC/DEC); блоки синхронизации и управления шиной, прерываниями и последовательным вводом/выводом.

Восьмиразрядное АЛУ выполняет предусмотренные системой команд МП арифметические и логические операции, результат которых помещает в аккумулятор, а также в зависимости от результатов операций (нуль, переполнение и т.д.) устанавливает регистр признаков RF.

Устройство управления и синхронизации на основе сигналов дешифратора команд формирует сигналы управления, передаваемые во все устройства системы для координации выполнения команд, а также формирует сигналы управления внешними устройствами (памятью, устройствами ввода/вывода и т.д.).

Блок управления прерываниями осуществляет переключение выполняемых программ (задач) МП по внешним сигналам управления, что необходимо для быстрой реакции МП на внешние события (нажатие клавиши на клавиатуре, переполнение буфера принтера и т.п.).

Блок управления последовательным вводом/выводом осуществляет программный ввод или вывод последовательных данных через внешние выводы SID, SOD соответственно.

Часть внутренних регистров используется процессором для собственных целей и является программно недоступным. К ним относится регистр IR, используемый для хранения, выбранной из памяти команды и регистры временного хранения данных - ТR, W, Z. Другие регистры программно доступны и могут использоваться программистом для собственных целей промежуточного хранения данных.

Программная модель ВМ85А

Блок программно-доступных регистров МП ВМ85А (рис. 2) отличается большой функциональной неоднородностью, что проявляется в выполнении большинством регистров МП присущих только им функций. В результате часто отсутствует необходимость в явном задании операндов и команды кодируются более коротко. В то же время усложнилось программирование из-за возникшей необходимости учитывать функциональные особенности регистров.

Подробнее рассмотрим программно-доступные регистры МП.

Аккумулятор А - 8-разрядный регистр, являющийся ядром большинства операций МП - при выполнении арифметических и логических операций он обычно является источником одного из операндов, в него же помещается результат. Другой операнд может находиться в одном из регистров МП или ячейке памяти и явно задается в команде МП. Аккумулятор также используется при обмене данными между МП и УВВ.

Регистры общего назначения B,C,D,E,H,L - в зависимости от выполняемой команды могут быть использованы как шесть 8-разрядных регистров или три 16-разрядные регистровые пары. Кроме того, регистровая пара HL используется МП для хранения адреса памяти при косвенной адресации данных. Несколько команд позволяют использовать и пары ВС и DE для адресации данных, но обычно они являются общецелевыми регистровыми парами временного хранения данных.

Счетчик команд PC используется для указания на адрес следующей выполняемой команды. Содержимое PC может быть изменено командами переходов, вызова подпрограмм и возврата из них.

Указатель стека SP предназначен для адресации особым образом организованной области памяти, называемой стеком. Он всегда указывает на вершину стека, содержащую последний введенный в него элемент. Стек заполняется в сторону младших адресов, что считается стандартным для МС.

Регистр состояния (флагов или индикаторов) RF использует 5 битов (флажков) хранения информации о состоянии МП. Флажки имеют следующее назначение:- признак переноса из старшего разряда АЛУ;

Р - признак четного числа единиц в результате операции;

АС - признак дополнительного переноса из младших четырех разрядов АЛУ;- признак нулевого результата;

М - знак результата.

Автоматическая установка битов в единицу происходит в результате выполнения арифметических и логических операций при условии наступления соответствующего назначению бита события, в противном случае содержимое битов сбрасывается в нуль. Эти биты используются командами условных переходов, вызова подпрограмм и возврата из них.

Кодирование команд и адресация данных

Команды ВМ85А требуют для кодирования от 1 до 3 байт. Первый байт всегда содержит код операции. Второй и при необходимости третий байты отводятся под непосредственные данные, адрес порта или ячейки памяти (рис. 3).

Рис. 3. Формат команд МП ВМ85А: а- однобайтовый, б- двухбайтовый, в- трехбайтовый

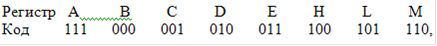

Поля dst и src предназначены для кодирования операндов в одно- и двухбайтовых командах МП согласно правилу

где фиктивный регистр М задает в качестве операнда ячейку памяти, косвенно адресуемую через регистровую пару HL.

Команды МП содержат именную часть команды или код операции, а также адресную часть, содержащую сведения об адресах операндов. Источниками и приемниками операндов могут служить: регистры МП, ячейки памяти, а также порты ВВ. Сведения о месторасположении операндов могут задаваться в двух формах: явной и неявной. Неявная форма обеспечивает передачу адресной информации через код операции, для чего используются поля dst и src на рис. 3. Достоинства такого подхода - в малой длине машинных команд, требующих меньшего времени для своего выполнения.

Большей гибкостью обладают команды, использующие явную форму задания адресной информации, что позволяет связывать с одной командой множество адресов, повышая ее эффективность. Однако при этом возрастает длина машинной команды и соответственно снижается эффективность объектного кода. На практике часто встречаются и комбинированные формы адресации, содержащие явную и неявную части.

Примеры команд, использующих явную адресацию: LXIrp,datal6; LHLD addr ADI data8

Примеры команд с неявной адресацией: MOV R1,R2; LDAX D ADDR

Метод задания адресов операндов в памяти называется способом адресации. Для повышения эффективности программного кода (т. е. минимизации длины программы или времени ее выполнения) разработан ряд способов адресации, каждый из которых наиболее эффективен для своей конкретной ситуации. Правильное использование всего набора позволяет обеспечить эффективный доступ к структурированным данным (массивы, стеки), сократить длину программного кода и число обращений к магистрали.

МП ВМ85А имеет следующие способы адресации: прямую, регистровую, непосредственную, косвенную регистровую. В случае регистровой адресации операнд находится в одном из внутренних регистров МП. Примеры команд с регистровой адресацией: MOV R1,R2. ADDR.

Поскольку для ссылки на регистр требуется всего лишь несколько бит, включаемых в код операции, команды данного типа имеют наименьшую длину и не требуют циклов обращения к магистрали. Все это обеспечивает командам регистровой адресации наибольшую эффективность.

Команды с прямым способом адресации используют для задания места расположения данных в памяти второй и третий байты команды. Прямая адресация позволяет явно выбрать любую ячейку памяти или порт ВВ во всем адресном пространстве МП. Примеры команд данного типа: IN, port; LHLD addr

В случае непосредственной адресации источником данных служит сама команда, второй и, если необходимо, третий байт которой служат для задания констант. Например: LXI В,1234; MVI D, 5.

Основной недостаток непосредственной адресации заключается в невозможности манипуляции данными без изменения программного кода, что привело к созданию способов с вычисляемым адресом, к простейшим из которых относится косвенная регистровая адресация. В командах с косвенной адресацией указывается не прямой адрес ячейки памяти, а регистровая пара МП, содержащая адрес операнда. К командам, использующим косвенный способ адресации, в частности, относятся: MOV A, M;LDAX B.

Временные диаграммы режимов работы ВМ85А

В каждом машинном цикле МП выполняет операцию ввода или вывода одного байта информации согласно временным диаграммам на рис. 4. Для синхронизации обмена используются стробы ALE, RD, WR соответственно типовому протоколу обмена по двухшинной магистрали. Непосредственно для ВВ информации отводятся 3 машинных такта: в такте 71 производится установка адресного кода на ША, а в тактах 72 и 73 - обмен данными. При необходимости к этим тактам может быть добавлено произвольное число тактов ожидания готовности канала Тw, включаемых между тактами Т2 и 73. Для реализации подобного асинхронного режима работы используется сигнал READY, проверка которого выполняется в середине 72 и всех следующих за ним тактов Tw. Для обеспечения надежного считывания этот сигнал должен быть установлен в 0 за 110 не до момента его первой проверки. Манипуляция сигналом READY позволяет удлинить строб RD или WR до значения (1,5+N)T-80 не (N - число периодов ожидания Tw) необходимого для надежного обмена данными с медленной памятью и У ВВ. В синхронном режиме работы сигнал READY=] на протяжении всего машинного цикла, дополнительные периоды ожидания отсутствуют (N=0) и длительность стробов RD, WR минимальна, составляя 1,5Г-80 не. Отметим, что действительность данных обеспечивается только в момент формирования задних фронтов этих стробов.

При обращении к устройствам ВВ 8-разрядный адрес порта присутствует как на младшей, так и старшей половинах ША, что позволяет ориентировать модули ВВ на использование сигналов А15 - A8, для приема которых отсутствует необходимость во внешнем адресном регистре.

На рис. 5 приведен пример командного цикла IN port без тактов ожидания. Команда содержит три машинных цикла: Ml -выборка кода операции, М2 - чтение из памяти второго байта команды и МЗ - выдача содержимого аккумулятора в порт ВВ. Циклы М2 и МЗ требуют трех машинных тактов, цикл Ml - четырех. Дополнительный такт здесь требуется для реализации внутренних операций в МП, связанных с декодированием команды.

Рис. 4. Временные диаграммы: а - циклов чтения, б - записи МП ВМ85 А

Рис. 5. Временные диаграммы командного цикла IN port

МП ВМ85А имеет пять входов приема запросов на прерывание: TRAP, RST 5.5, RST 6.5, RST 7.5, INTR и один выход управления им - INTA. Первым четырем входам запроса сопоставлены фиксированные вектора прерываний, расположенные по адресам: 24Н, 2СН, 34Н, ЗСН. Уточним, что под вектором прерываний подразумевается информация, необходимая для перехода к соответствующей подпрограмме обслуживания. В простейшем случае - это просто адрес этой подпрограммы в памяти.

Линия LNTR предназначена для приема запроса на прерывание, при котором адрес обслуживающей подпрограммы определяет внешнее устройство, передавая по шине данных команду CALL или, что более удобно, команду RSTn. При этом для обеспечения приема команды, сформированной внешней аппаратурой, в ответ на запрос INTR генерируется один или три машинных цикла подтверждения прерывания, аналогичных циклам чтения памяти (без тактов ожидания), однако с активным сигналом INTA вместо сигнала RD (рис. 6).

микропроцессор память программный мощность

Рис. 6. Временные диаграммы цикла подтверждения прерывания и захвата шины

Вход TRAP имеет наивысший приоритет и является немаскируемым, т.е. прерывания по нему не могут быть запрещены программно. На этот вход подаются сигналы, оповещающие о наиболее важных событиях в МС, требующих немедленной реакции МП (например, связанных с аварийным изменением напряжения питания). Запросы по входам RST и INTR являются маскируемыми и управляются программно командами EI (разрешить прерывания) и DI (запретить прерывания), управляющими общим флагом разрешения прерываний. Существует также возможность раздельного маскирования запросов по входам RST, обеспечиваемая с помощью команды SIM.

Сопряжение ВМ85А с шинами микропроцессорной системы

В ряде применений однокристальные МП не могут быть непосредственно соединены с шинами МС по причине недостаточной нагрузочной способности их выходов. Для организации сопряжения МП с системными шинами в этом случае находят применение буферные регистры и шинные формирователи. Ниже рассмотрены некоторые типичные представители данных классов микросхем.

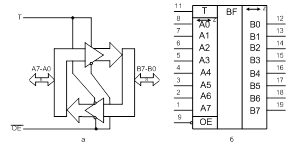

Буферный регистр КР580ИР82/ИР83 представляет собой 8-разрядный регистр-защелку, обеспечивающий выходной ток до 32 мА,и емкость нагрузки до 300 пФ и используемый в качестве фиксатора или буфера. На рис. 7 приведены схема и условное графическое обозначение регистра КР580ИР82, в отличие от которого КР580ИР83 имеет инверсные выходные сигналы.

Рис. 7. Буферный регистр КР580ИР82: а- структурная схема; б- условное графическое обозначение

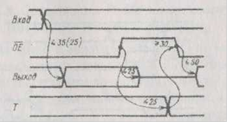

Основой схемы является 8-разрядный регистр со статическим управляющим входом STB, разрешающим запись при высоком уровне сигнала и хранение при низком уровне. Регистр содержит трехстабильный выходной буфер, управляемый сигналом ОЕ. При активном уровне этого сигнала (ОЕ=0) данные передаются на выход микросхемы, в ином случае буфер закрыт и находится в высокоомном состоянии. Временные диаграммы работы регистра представлены на рис. 8.

Рис. 8. Временные диаграммы работы регистров КР580ИР82/ИР83

Шинный формирователь КР580ВА86/ВА87 предназначен для реализации 8-разрядных одно- и двунаправленных буферных схем с тремя состояниями на выходе. На рис. 9 приведены схема и условное графическое обозначение БИС КР580ВА86, в отличие от которого КР580ИР83 имеет инверсные выходные сигналы.

Рис. 9. Шинный формирователь КР580ВА86: а- структурная схема; б- условное графическое обозначение

Основой схемы являются трехстабильные 8-разрядные буферные схемы, обеспечивающие со стороны канала А ток нагрузки до 16 мА при емкости нагрузки до 100пФ и со стороны канала В ток нагрузки до 32 мА при емкости нагрузки до 300 пФ. Таким образом, нагрузочная способность буфера является различной. Буферы выбираются только при низком уровне сигнала ОЕ, обеспечивая передачу данных из А в В при высоком уровне сигнала на входе Г и в обратном направлении в ином случае. Временные диаграммы работы буфера представлены на рис. 10.

Рис. 10. Временные диаграммы работы формирователей КР580ВА86/ВА87

Схема центрального процессора на базе ВМ85А приведена на рис. 11. Схема не требует внешнего тактового генератора, для запуска процессора необходим лишь кварцевый резонатор ZQ1, подключенный к входам XTAL1, XTAL2. В качестве схемы сброса используется RС-цепочка на элементах R1, R2, С5, постоянная времени которой рассчитывается из требований, накладываемых на длительность сигнала Reset.

Возможности выходов ВМ85А по току составляют 1<х = 2 мА, 1он = 400 мкА. Зная требования по постоянному току подключаемых элементов, можно оценить нагрузочную способность МП. Кроме токовой составляющей необходимо учитывать и емкостную составляющую нагрузки. Временные соотношения для ВМ85А гарантируются при CL < 150 пФ. При превышении этого значения временные соотношения ухудшаются, изменяясь приблизительно на 0,2 нс/пФ.

Шина данных МС через резисторы R4, R3 подключена к источнику питания. В результате чтение команды из несуществующей области памяти приведет к выполнению команды RST 7, что может быть использовано в отладочных целях.

Три сигнала МС - запрос на захват шины, подтверждение захвата HLDA и разрешение шины BUSEN- служат для организации доступа к системной магистрали со стороны других активных моделей системы. При отсутствии таких модулей требуется установка перемычек 1-2 и 3-4.

Системный контроллер представляет собой комбинационную схему, предназначенную для преобразования выходных сигналов МП в стробы синхронизации и управления доступом к памяти и УВВ. Возможна его реализация на микросхемах малой степени интеграции, а также ПЛМ.

Рис. 11. Схема центрального процессора на базе микропроцессора ВМ85А

Микропроцессор представляет собой практически законченный однокристальный ЦП. Для его запуска необходим только кварцевый резонатор, подключенный к входам Х1,Х2, и схема сброса на входе RESIN. Схема подключения кварцевого резонатора приведен в на рисунке 4.7, а. Конденсаторы емкостью 20 пФ на входах Х1 и Х2 могут потребоваться при запуске кварцевого резонатора с частотой 4 МГц и выше. Возможны другие варианты синхронизации МП. Схема на рисунке 4.7, б обеспечивает частоту колебаний

(4.1)

(4.1)

Где СIN- входная емкость между Х1 и Х2.

Рисунок 4.7 - Схемы тактирования микропроцессора ВМ85А

На рисунке 4.7 а) внутренний генератор с кварцевым резонатором; б) внутренний генератор с настроенным LC-контуром; в) внутренний генератор с RC-цепочкой; г-внешний генератор 1-6 МГц; д-внешний генератор 6-10 МГц.

Если установка точной тактовой частоты не обязательна, то применяется схема, показанная на рис. 3.7, в, которая обеспечивает частоту колебаний около 3 МГц. В схеме на рис.3.7, г, д синхронизация МП осуществляется от внешнего генератора. Схема центрального процессора на базе микропроцессора ВМ85Апредставлена на рис.3.8. Вход READY может быть использован для организации асинхронного доступа к системной магистрали. В ЦП на базе ВМ85А возможны два варианта построения системной линии подтверждения обмена, отличающиеся друг от друга уровнем активности. Выходы CLK и RESET применяются в качестве системных линий CCLK и INIT передачи тактовых импульсов и сигнала начальной установки соответственно. Возможности выходов схемы ВМ85А по току составляют IOL = 2мА IOH=400мкА. Зная требования по постоянному току, предъявляемые к обычным логическим элементам по входу, можно оценить нагрузочную способность МП ВМ85А.

Рисунок 4.8 - Схема центрального процессора на базе микропроцессора ВМ85А

Системный контроллер представляет собой комбинационную схему рисунок 4.9. На выходах схемы предусмотрены трехстабильные буферы, управляемые сигналом ОЕ. Этот вход предназначен для перевода командных линий в высокоомное состояние при захвате магистрали внешним модулем, когда BUSEN=0. Логика данного типа может быть реализована как на микросхемах малой степени интеграции, так и на программируемых логических матрицах (ПЛМ).

Рисунок 4.9 - Схема системного контроллера для МП ВМ85А

Применение МП ВМ85А выгодно за счет увеличения числа входных линий для приема запросов на прерывание, использования канала последовательного ВВ и перехода к единственному источнику питания +5 В. Не следует также забывать об улучшении скоростных свойств системного канала ЦП на базе МП ВМ85А.

Эффективность использования МП может быть повышена, если от трехшинной структуры вернуться к совмещенной магистрали AD. Однако в этом случае потребуется ряд специальных БИС памяти и ВВ, которые должны быть ориентированы на магистраль данного типа.