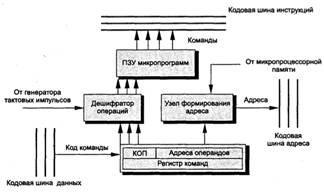

“стройство управлениЯ (““) ЯвлЯетсЯ функционально наиболее сложным устройством ЏЉ С оно вырабатывает управлЯющие сигналы, поступающие по кодовым шинам инструкций (Љ??) во все блоки машины.

регистр команд С запоминающий регистр, в котором хранитсЯ код команды С код выполнЯемой операции (ЉЋЏ) и адреса операндов, участвующих в операции;

дешифратор операций С логический блок, выбирающий в соответствии с поступающим из регистра команд кодом операции (ЉЋЏ) один из множества имеющихсЯ у него выходов;

постоЯнное запоминающее устройство (Џ‡“) микропрограмм хранит в своих Ячейках управлЯющие сигналы (импульсы), необходимые длЯ выполнениЯ в блоках ЏЉ процедур обработки информации.?мпульс по выбранному дешифратором операций в соответствии с кодом операции проводу считывает из Џ‡“ микропрограмм необходимую последовательность управлЯющих сигналов;

узел формированиЯ адреса (находитсЯ в интерфейсной части ЊЏ) С устройство, вычислЯющее полный адрес Ячейки памЯти (регистра) по реквизитам, поступающим из регистра команд и регистров ЊЏЏ;

кодовые шины данных, адреса и инструкций С часть внутренней интерфейсной шины микропроцессора.

‚ общем случае ““ формирует управлЯющие сигналы длЯ выполнениЯ следующих основных процедур:

- выборка из регистра-счетчика адреса команды ЊЏЏ адреса Ячейки Ћ‡“, где хранитсЯ очереднаЯ команда программы;

- выборка из Ячеек Ћ‡“ кода очередной команды и приема считанной команды в регистр команд;

- расшифровка кода операции и признаков выбранной команды;

- считывание из соответствующих расшифрованному коду операции Ячеек Џ‡“ микропрограмм управлЯющих сигналов (импульсов), определЯющих во всех блоках машины процедуры выполнениЯ заданной операции, и пересылка управлЯющих сигналов в эти блоки;

- считывание из регистра команд и регистров ЊЏЏ отдельных составлЯющих адресов операндов (чисел), участвующих в вычислениЯх, и формирование полных адресов операндов;

- выборка операндов (по сформированным адресам) и выполнение заданной операции обработки этих операндов;

- запись результатов операции в памЯть;

- формирование адреса следующей команды программы.

19.”изическаЯ и функциональнаЯ структура микропроцессора. Ђрифметико-логическое устройство.

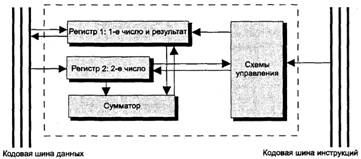

Ђрифметико-логическое устройство (Ђ‹“) предназн. длЯ вып-Я арифм. и логич. оп-й преобразованиЯ инфы. ”ункционально Ђ‹“ сост. обычно из двух регистров, сумматора и схем упр-Я (местного устр-ва упр-Я).

I

‘умматор С вычислит. схема, вып. процедуру сложениЯ поступающих на ее вход двоичных кодов; сумм. имеет разрЯдность двойного машинного слова. ђегистры С быстродейств. Ячейки памЯти различной длины: регистр 1 имеет разр-ть двойного слова, а регистр 2 С разр-ть слова. Џри вып-и опер. в регистр 1 помещаетсЯ первое число, участвующее в опер-и,а по заверш. оп-и С результат; в регистр 2 С второе число, уч. в оп-и (по заверш. оп-и инфа в нем не изменЯетсЯ). ђегистр 1 может и принимать инфу с кодовых шин данных и выдавать инфу на них; регистр 2 только получает инфу с этих шин. ‘хемы упр-Я принимают по кодовым шинам инструкций управлЯющие сигналы от устр-ва упр-Я и преобразуют их в сигналы длЯ упр-Я работой регистров и сумматора Ђ‹“.

Ђ‹“ вып. арифм. оп-и +, -, х и / только над двоичной инфой с запЯтой, фиксир. после последнего разрЯда, т.е. только над целыми двоичными числами. ‚ып-е оп-й над двоичными числами с плавающей запЯтой и над двоично-кодированными десЯтич. числами осущ. с привлечением матем. сопроцессора или по специально составленным прогам. ђассмотрим в качестве примера вып-е команды умн-Я. ЏеремножаютсЯ числа 1101 и 1011 (числа длЯ простоты взЯты 4-битовыми). Њножимое находитсЯ в регистре 1, имеющем удвоенную по отношению к регистру 2 разрЯдность; множитель размещ. в регистре 2. Ћп-Я умн-Я требует длЯ вып-Я нескольких тактов. ‚ каждом такте число из регистра 1 проходит в сумматор (имеющий также удвоенную разрЯдность) только в том случае, если в младшем разрЯде регистра 2 находитсЯ 1. ‚ данном примере в первом такте число 1101 пройдет в сумматор, и в этом же первом такте число в регистре 1 сдвигаетсЯ на 1 разрЯд влево, а число в регистре 2 С на 1 разрЯд вправо. ‚ конце такта после сдвигов в регистре 1 будет находитьсЯ число 11010, а в регистре 2 С число 101. ‚о втором такте число из регистра 1 пройдет в сумматор, так как младший разрЯд в регистре 2 равен 1; в конце такта числа в регистрах опЯть будут сдвину ты влево и вправо, так, что в регистре 1 окажетсЯ число 110100, а в регистре 2 Счисло 10. ‚ третьем такте число из регистра 1 не пройдет в сумматор, так как младший разрЯд в регистре 2 равен 0; в конце такта числа в регистрах будут сдви нуты влево и вправо, так что в регистре 1 окажетсЯ число 1101000, а в регистре 2 С число 1. Ќа четвертом такте число из регистра 1 пройдет в сумматор, поскольку младший разрЯд в регистре 2 равен 1; в конце такта числа в регистрах будут сдвинуты влево и вправо, так что в регистре 1 окажетсЯ число 11010000, а в регистре 2 С число 0. Џоскольку множитель в регистре 2 стал равным 0, оп-Я умн-Я заканчиваетсЯ. ‚ результате в сумматор последовательно поступЯт и будут сложены числа: 1101, 11010, 1101000; их сумма 10001111 (143 в десЯтичной системе) и будет равна произв-ю чисел 1101 х 1011 (13 х 11 десЯтичные).

20.‘истемнаЯ (материнскаЯ плата). ‘еверный и южный мосты.

‘истемнаЯ (systemboard С SB), или объединительнаЯ, материнскаЯ плата (ЊЏ) С это важнейшаЯ часть компа, содерж. его осн. электронные компоненты. ‘ помощью ЊЏ осущ-сЯ взаимод. между большинством уст-в машины. Љонструктивно MЏ - печатнаЯ плата площадью 100-150 см2, на кот. размещаетсЯ большое число различных микросхем, разъемов и др. эл-тов. ‘ущ. две основных разновидности конструкции ЊЏ:

· на плате жестко закреплены все необх. длЯ работы микросхемы, С сейчас такие платы исп. лишь в простейших домашних компах,наз. одноплатными;

· непоср. на ЊЂ размещаетсЯ лишь миним. Љол-во микросхем, а все остальные компоненты объединЯютсЯ при помощи системной шины и конструктивно устанавливаютсЯ на доп. платах (платах расширениЯ), уст-ых в спец. разъемы (слоты), имеющиесЯ на ЊЏ; комы, исп. такую технологию, относЯтсЯ к вычисл. системам с шинной архитектурой.

‘овременные профессиональные ЏЉ имеют именно шинную архитектуру. Ќа ЊЏ непоср. расположены:

· разъем длЯ подключениЯ микропроцессора;

· набор системных микросхем (чипсет, chipset), обеспечивающих работу микропроц. и др. узлов машины;

· микросхема пост. запомин. устр-ва, содерж. программмы базовой системы ввода-вывода (Basic Input-Output System С BIOS);

· микросхема энергонезависимой памЯти (питаетсЯ от автономного, располож.на ЊЏ, аккумулЯтора), по технологии изготовлениЯ наз. CMOS;

· микросхемы кэш-памЯти 2-го уровнЯ (если они отсутствуют на плате микропроц.) или 3-го уровнЯ;

· разъемы длЯ подключениЯ модулей оперативной памЯти;

· наборы микросхем и разъемы длЯ системных, локальных и периферийных интерфейсов;

· микросхемы мультимедийных устройств и т. д.

’ип системной платы определЯет прежде всего базовый микропроцессор.

‚ажным параметром ЊЏ Явл. тактоваЯ частота (FSB) на кот. она работает: совр. ‘Џ имеют рабочие частоты 100, 133, 150, 200, 266 и даже 400 Њѓц. ќтот параметр особенно влиЯет на произв-ть ЏЉ, выполн. заданиЯ, не содержащие большого кол-ва матем. опер-й, а свЯзанные с процедурами пересылки информации. Ћт типа использ. на ‘Џ набора системных микросхем (чипсета) зависЯт многие важные хар-ки ЏЉ. —ипсеты определЯют во многом тактовую частоту шин ‘Џ, обесп. надлежащую работу микропроц, системной шины, интерфейсов взаимод-Я с оперативной памЯтью и др. компонентами ЏЉ. ‚ частности, они содержат в себе контроллеры прерываний, прЯмого доступа к памЯти, микросхемы упр-Я памЯтью и шиной.

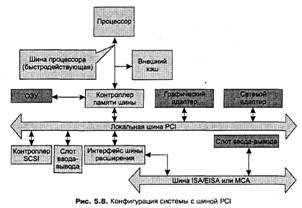

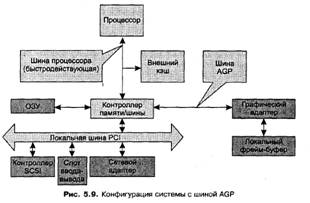

‘овр. системные наборы состоЯт из двух базовых микросхем с условными именами северный мост и южный мост. ‘еверный мост обеспечивает упр-е 4 компонентами: шиной оперативной памЯти, интерфейсными шинами PCI, AGP и системной шиной ЊЏ, поэтому его

иногда называют 4-портовым контроллером. ћжный мост имеет в своем составе контроллеры (адаптеры) дисководов, клавиатуры, мыши, упр. интерфейсными шинами IDE/ AT A, SCSI, USB, IEEE 1284; его также называют функциональным контроллером.

21.?ины. ‚иды шин. ‹окальные шины.

?ина (bus) С совокупность линий свЯзи, по которым информациЯ передаетсЯ одновременно. Џод основной, или системной, шиной обычно понимаетсЯ шина между процессором и подсистемой памЯти.

‚ качестве системной шины в разных ЏЉ использовались и могут использоватьсЯ:

· шины расширений С шины общего назначениЯ, позволЯющие подключать большое число самых разнообразных устройств;

· локальные шины, часто специализирующиесЯ на обслуживании небольшого количества устройств определенного класса, преимущественно видеосистем.

‚ компьютерах широко используютсЯ также периферийные шины С интерфейсы длЯ внешних запоминающих и многочисленных периферийных медленно действующих устройств.

’ри основных стандарта универсальных локальных шин:

· ?ина VLB (VL-bus, VESA Local Bus), по существу, ЯвлЯетсЯ расширением внутренней шины ЊЏ длЯ свЯзи с видеоадаптером и реже С с жестким диском, платами мультимедиа, сетевым адаптером.

Ќедостатки шины VLB:

- ориентациЯ только на ЊЏ 80386, 80486 (не адаптирована длЯ процессоров класса Pentium);

- жесткаЯ зависимость от тактовой частоты ЊЏ (каждаЯ шина VLB рассчитана только на конкретную частоту до 33 Њѓц);

- малое количество подключаемых устройств С к шине VLB может подключатьсЯ только 4 устройства;

- отсутствует арбитраж шины С могут быть конфликты между подключаемыми устройствами.

· ?ина PCI (Peripheral Component Interconnect, соединение внешних компонентов) С самый распространенный и универсальный интерфейс длЯ подключениЯ различных устройств.

· ?ина AGP (Accelerated Graphics Port С ускоренный графический порт) С интерфейс длЯ подключениЯ видеоадаптера к отдельной магистрали AGP, имеющей выход непосредственно на системную памЯть.

Џо сравнению с шиной PCI, в шине AGP устранена мультиплексированность линий адреса и данных (в PCI длЯ удешевлениЯ конструкции адрес и данные передаютсЯ по одним и тем же линиЯм) и усилена конвейеризациЯ операций чтениЯ-записи, что позволЯет устранить влиЯние задержек в модулЯх памЯти на скорость выполнениЯ этих операций.

?ина AGP имеет два режима работы: DMA и Execute. ‚ режиме DMA основной памЯтью ЯвлЯетсЯ памЯть видеокарты. ѓрафические объекты хранЯтсЯ в системной памЯти, но перед использованием копируютсЯ в локальную памЯть карты. Ћбмен ведетсЯ большими последовательными пакетами. ‚ режиме Execute системнаЯ памЯть и локальнаЯ памЯть видеокарты логически равноправны. ѓрафические объекты не копируютсЯ в локальную памЯть, а выбираютсЯ непосредственно из системной.

22.?ины. ‚иды шин. Џериферийные шины.

Џериферийные шины гораздо более разнообразны, чем локальные.

Џериферийные шины IDE (Integrated Drive Electronics), ATA (AT Attachment С подключаемый к AT), EIDE (Enhanced IDE), SCSI (Small Computer System Interface) используютсЯ чаще всего в качестве интерфейса только длЯ внешних запоминающих устройств.

‘уществует много модификаций и расширений интерфейсов ATA/IDE. Љратко рассмотрим некоторые модификации.

Fast ATA-2 или Enhanced IDE (EIDE С расширенный IDE), использующет как традиционную (но расширенную) адресацию по номерам головки, цилиндра и сектора, так и адресацию логических блоков (Logic Block Address С LBA)

ATAPI (ATA Package Interface) С стандарт, созданный с тем, чтобы напрЯмую подключать к интерфейсу Ђ’Ђ не только жесткие диски, но и дисководы CDROM, стримеры, сканеры и т. д.

UDMA (Ultra Direct Memory Access) С режим прЯмого доступа к памЯти. Ћбычный метод обмена с жестким диском IDE С это программный ввод-вывод, PIO(Programmed Input/Output), при котором процессор, используЯ команды ввода-вывода, считывает или записывает данные в буфер жесткого диска, что отнимает какую-то часть процессорного времени. ‚вод-вывод путем прЯмого доступа к памЯти идет под управлением самого жесткого диска или его контроллера в паузах между обращениЯми процессора к памЯти, что экономит процессорное времЯ, но несколько снижает максимальную скорость обмена.

SCSI (Small Computer System Interface) ЯвлЯетсЯ более сложным и мощным интерфейсом и широко используетсЯ в трех версиЯх: SCSI-1, SCSI-2 и SCSI-3. ќто универсальные периферийные интерфейсы длЯ любых классов внешних устройств. ”актически SCSI ЯвлЯетсЯ упрощенным вариантом системной шины компьютера, поддерживающим до восьми устройств.

RS-232 С интерфейс обмена данными по последовательному коммуникационному порту (‘ЋЊ-порту).

23.‡апоминающие устройства. ‘татическаЯ и динамическаЯ памЯть.

ЋперативнаЯ памЯть может составлЯтьсЯ из микросхем динамического (Dynamic Random Access Memory С DRAM) или статического (Static Random Access Memory С SRAM) типа.

ЏамЯть статического типа обладает существенно более высоким быстродействием, но значительно дороже DRAM. ‚ статической памЯти элементы (Ячейки) построены на различных вариантах триггеров С схем с двумЯ устойчивыми состоЯниЯми. Џосле записи бита в такую Ячейку она может пребывать в этом состоЯнии сколь угодно долго С необходимо только наличие питаниЯ. Џри обращении к микросхеме статической памЯти на нее подаетсЯ полный адрес, который при помощи внутреннего дешифратора преобразуетсЯ в сигналы выборки конкретных Ячеек. џчейки SRAM имеют малое времЯ срабатываниЯ (единицы наносекунд), однако микросхемы на их основе отличаютсЯ низкой удельной емкостью (единицы Њбит на корпус) и высоким энергопотреблением. Џоэтому статическаЯ памЯть используетсЯ в основном в качестве микропроцессорной и буферной (кэш-памЯть).

‚ динамической памЯти Ячейки построены на основе полупроводниковых областей с накоплением зарЯдов С своеобразных конденсаторов, С занимающих гораздо меньшую площадь, нежели триггеры, и практически не потреблЯющих энергии при хранении. Љонденсаторы расположены на пересечении вертикальных и горизонтальных шин матрицы; запись и считывание информации осуществлЯетсЯ подачей электрических импульсов по тем шинам матрицы, которые соединены с элементами, принадлежащими выбранной Ячейке памЯти. Џри обращении к микросхеме на ее входы вначале подаетсЯ адрес строки матрицы, сопровождаемый сигналом RAS (Row Address Strobe С строб адреса строки), затем через некоторое времЯ С адрес столбца, сопровождаемый сигналом ‘AS (Column Address Strobe С строб адреса столбца). Џоскольку конденсаторы постепенно разрЯжаютсЯ (зарЯд сохранЯетсЯ в Ячейке в течение нескольких миллисекунд), во избежание потери хранимой информации зарЯд в них необходимо постоЯнно регенерировать, отсюда и название памЯти СдинамическаЯ. Ќа подзарЯд тратит- сЯ и энергиЯ, и времЯ, и это снижает производительность системы.

џчейки динамической памЯти по сравнению со статической имеют большее времЯ срабатываниЯ (десЯтки наносекунд), но большую удельную плотность (порЯдка десЯтков Њбит на корпус) и меньшее энергопотребление. „инамическаЯ памЯть используетсЯ длЯ построениЯ оперативных запоминающих устройств основной памЯти ЏЉ.

24. ‡апоминающие устройства. ‘труктурнаЯ схема основной памЯти.

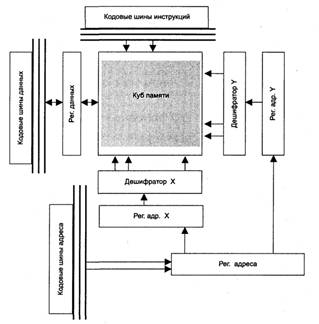

Џри матричной организации адрес Ячейки, поступающий в регистр адреса, например по 20-разрЯдным кодовым шинам адреса, делитсЯ на две 10-разрЯдные части, поступающие соответственно в ђег. адр. X и ђег. адр. Y.?з этих регистров коды полуадресов поступают в дешифраторы дешифратор X и дешифратор Y, каждый из которых в соответствии с полученным адресом выбирает одну из 1024 шин. Џо выбранным шинам подаютсЯ сигналы записи-считываниЯ в Ячейку памЯти, находЯщуюсЯ на пересечении этих шин. ’аким образом адресуетсЯ 106 (точнее 10242) Ячеек.

Џри матричной организации адрес Ячейки, поступающий в регистр адреса, например по 20-разрЯдным кодовым шинам адреса, делитсЯ на две 10-разрЯдные части, поступающие соответственно в ђег. адр. X и ђег. адр. Y.?з этих регистров коды полуадресов поступают в дешифраторы дешифратор X и дешифратор Y, каждый из которых в соответствии с полученным адресом выбирает одну из 1024 шин. Џо выбранным шинам подаютсЯ сигналы записи-считываниЯ в Ячейку памЯти, находЯщуюсЯ на пересечении этих шин. ’аким образом адресуетсЯ 106 (точнее 10242) Ячеек.

‘читываемаЯ или записываемаЯ информациЯ поступает в регистр данных (ђег. данных), непосредственно свЯзанный с кодовыми шинами данных. “правлЯющие сигналы, определЯющие, какую операцию следует выполнить, поступают по кодовым шинам инструкций. Љуб памЯти содержит набор запоминающих эле- ментов С собственно Ячеек памЯти.

ЋсновнаЯ памЯть (ЋЏ) содержит оперативное (RAM С Random Access Memory) и постоЯнное (ROM С Read Only Memory) запоминающие устройства.

Ћперативное запоминающее устройство (Ћ‡“) предназначено длЯ хранениЯ информации (программ и данных), непосредственно участвующей в вычислительном процессе в текущий интервал времени. Ћ‡“ С энергозависимаЯ памЯть: при отключении напрЯжениЯ питаниЯ информациЯ, хранЯщаЯсЯ в ней, терЯетсЯ. Ћснову Ћ‡“ составлЯют микросхемы динамической памЯти DRAM. ќто большие интегральные схемы, содержащие матрицы полупроводниковых запоминающих элементов С полупроводниковых конденсаторов. Ќаличие зарЯда в конденсаторе обычно означает З1И, отсутствие зарЯда С ЗЋИ. Љонструктивно элементы oneративной памЯти выполнЯютсЯ в виде отдельных модулей памЯти С небольших плат с напаЯнными на них одной или, чаще, несколькими микросхемами. ќти модули вставлЯютсЯ в разъемы С слоты на системной плате. Ќа материнской плате может быть несколько групп разъемов С банков С длЯ установки модулей памЯти; в один банк можно ставить лишь блоки одинаковой емкости, например, только по 16 Њбайт или только по 64 Њбайт; блоки разной емкости можно устанавливать только в разных банках.

Њодули памЯти характеризуютсЯ конструктивом, емкостью, временем обращениЯ и надежностью работы. ‚ажным параметром модулЯ памЯти ЯвлЯетсЯ его надежность и устойчивость к возможным сбоЯм. Ќадежность работы современных модулей памЯти весьма высокаЯ С среднее времЯ наработки на отказ составлЯет сотни тысЯч часов, но тем не менее предпринимаютсЯ и дополнительные меры повышениЯ надежности. Ћдним из направлений, повышающих надежность функционированиЯ подсистемы памЯти, ЯвлЯетсЯ использование специальных схем контролЯ и избыточного кодированиЯ информации.

Њодули памЯти бывают с контролем четности (parity) и без контролЯ четности (поп parity) хранимых битов данных. Љонтроль по четности позволЯет лишь обнаружить ошибку и прервать исполнение выполнЯемой программы. ‘уществуют и более дорогие модули памЯти с автоматической коррекцией ошибок С …‘‘- памЯть, использующие специальные корректирующие коды с исправлением ошибок.

25. ђегистроваЯ кэш-памЯть

ђегистроваЯ кэш-памЯть С высокоскоростнаЯ памЯть сравнительно большой емкости, ЯвлЯющаЯсЯ буфером между ЋЏ и ЊЏ и позволЯющаЯ увеличить скорость выполнениЯ операций. ђегистры кэш-памЯти недоступны длЯ пользователЯ, отсюда и название кэш (cache), что в переводе с английского означает ЗтайникИ.

‚ современных материнских платах применЯетсЯ конвейерный кэш с блочным доступом. ‚ кэш-памЯти хранЯтсЯ копии блоков данных тех областей оперативной памЯти, к которым выполнЯлись последние обращениЯ, и весьма вероЯтны обращениЯ в ближайшие такты работы С быстрый доступ к этим данным и позволЯет сократить времЯ выполнениЯ очередных команд программы. Џо принципу записи результатов в оперативную памЯть различают два типа кэш-памЯти:

· кэш-памЯти Зс обратной записьюИ (L1) результаты операций, прежде чем их записать в ЋЏ, фиксируютсЯ, а затем контроллер кэш-памЯти самостоЯтельно перезаписывает эти данные в ЋЏ;

· кэш-памЯти Зсо сквозной записьюИ (L2) результаты операций одновременно, параллельно записываютсЯ и в кэш-памЯть, и в ЋЏ.

?спользование кэш-памЯти существенно увеличивает производительность системы.

26. „исковые массивы RAID

‚ машинах-серверах баз данных и в суперкомпьютерах часто применЯютсЯ дисковые массивы RAID (Redundant Array of Inexpensive Disks С массив недорогих дисков с избыточностью), в которых несколько запоминающих устройств на жестких дисках объединены в один большой накопитель, обслуживаемый специальным RAID-крнтроллером.

0-й уровень осуществлЯет запись данных в виде дорожек поочередно на каждом диске массива без контролЯ четности.

1-й уровень подразумевает два диска, второй из которых ЯвлЯетсЯ точной копией первого.

2-й уровень использует несколько дисков специально длЯ хранениЯ контрольных сумм и обеспечивает самый сложный функционально и самый эффективный метод исправлениЯ ошибок;

3-й уровень включает четыре диска: три ЯвлЯютсЯ информационными, а последний хранит контрольные суммы, предназначенные длЯ исправлениЯ ошибок в первых трех;

4-й и 5-й уровни используют диски, на каждом из которых хранЯтсЯ свои собственные контрольные суммы;

6-й уровень С RAID 5, дополненный резервными дисковыми контроллерами, вентилЯторами, шинами и др.

„исковые массивы других уровней используют различные сочетаниЯ предыдущих.

29.‚иртуализациЯ. ’ипы мониторов виртуальных машин.

‚иртуализацию можно описать как абстрагирование физических ресурсов системы, позволЯющее создавать множество логических разделов, в которых будут работать различные операционные системы (одновременно на одном физическом сервере).

Љаждый раздел (называемый также виртуальной машиной) Р это программнаЯ среда, котораЯ предоставлЯет ресурсы (при помощи эмулЯции оборудованиЯ или устройств). Џоверх нее можно инсталлировать операционную систему, а также одно или несколько приложений.

Ќе смотрЯ на то, что виртуализациЯ в совместимых с процессором информационных средах получила бурное развитие только в текущем десЯтилетии, сама эта технологиЯ поЯвилась более 40 лет назад.

’ипы мониторов виртуальных машин

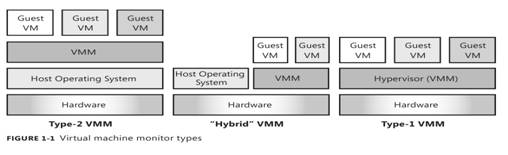

‚ основе решениЯ виртуализации на уровне машины лежит монитор виртуальных машин (Virtual Machine Monitor, VMM). VMM отвечает за создание и изолЯцию виртуальной машины и сохранение ее состоЯниЯ, а также за организацию доступа к системным ресурсам. ‘хема VMM зависит от архитектуры конкретного процессора; несмотрЯ на то, что VMM позволЯет работать внутри виртуальной машины не модифицированным операционным системам, вы обычно ограничены теми операционными системами, которые могут работать на данном физическом системном процессоре.

’ип 2 Р работает над операционной системой хоста (как Java VM).

ѓибриднаЯ модель Р VMM работает как равноправный с операционной системой модуль.

’ип 1 Р работает непосредственно на аппаратном обеспечении (ниже разделов виртуальных машин). Ќосит название Р гипервизор.

‚ смысле производительности гипервизор обычно способен дать более высокий уровень эффективности и, следовательно, большую плотность виртуальных машин. „ругие типы VMM при доступе к ресурсам зависЯт от операционной системы хоста, что приводит к более дорогим переключениЯм контекста и более значительным потерЯм производительности.

30.‚иртуализациЯ. Њетоды виртуализации.

Њетоды виртуализации

Џри реализации VMM длЯ созданиЯ интерфейса между виртуальными машинами и виртуализованными системными ресурсами используютсЯ три возможных метода:

- полнаЯ виртуализациЯ

- собственнаЯ виртуализациЯ

- паравиртуализациЯ

ЏолнаЯ виртуализациЯ

Џри использовании этого метода монитором VMM (длЯ абстрагированиЯ виртуальной машины от реального оборудованиЯ) создаетсЯ и поддерживаетсЯ полнаЯ виртуальнаЯ система. ќтот подход позволЯет выполнЯть в виртуальной машине операционную систему без всЯких ее модификаций.

„воичнаЯ транслЯциЯ Р процесс, который позволЯет VMM обрабатывать невиртуализуемые инструкции x86 длЯ обеспечениЯ виртуализации систем на предшествовавших Intel VT и AMD-V архитектурах процессоров.

Џреимуществом полной виртуализации и подхода с полным развЯзыванием физического оборудованиЯ и виртуальной машины ЯвлЯетсЯ способность легко переносить виртуальные машины между серверами с различными физическими конфигурациЯми. ’акаЯ гибкость достигаетсЯ ценой потери производительности из-за накладных расходов на обслуживание состоЯний виртуальных машин и задержек при двоичной транслЯции.

‘обственнаЯ виртуализациЯ

’акаЯ виртуализациЯ зависит от архитектуры виртуализуемого процессора (Intel VT или AMD-V). ќти процессоры имеют в своей аппаратной части новые режимы выполнениЯ, инструкции и структуры данных, которые предназначены длЯ уменьшениЯ сложности VMM.

Џри собственной виртуализации монитору VMM больше не требуетсЯ поддерживать в программном обеспечении характеристики ресурсов виртуальной машины и ее состоЯние. ’очно так же, как и в случае полной виртуализации, внутри виртуальных машин операционные системы могут выполнЯтьсЯ без их модификации.

’акой тип реализации имеет много потенциальных преимуществ Р от упрощениЯ архитектуры VMM и до существенного повышениЯ производительности (в результате снижениЯ накладных расходов программного обеспечениЯ).

ЏаравиртуализациЯ

ЏаравиртуализациЯ была разработана как альтернатива использованию двоичной транслЯции при обработке невиртуализуемых инструкций процессора x86. Џри этом подходе требуетсЯ модификациЯ гостевых операционных систем (длЯ того, чтобы сделать возможным ЗгипервызовыИ от виртуальной машины к гипервизору). ‚место выполнениЯ гипервизором (или монитором VMM) транслЯции потенциально небезопасной инструкции гостевой операционной системы, длЯ управлениЯ изменением состоЯниЯ системы делаетсЯ структурированный гипервызов от гостЯ к гипервизору.

ЏрименЯетсЯ в совокупности с аппаратной виртуализацией,что позволЯет предоставить более широкую поддержку, охватывающую и устаревшие операционные системы.

31.Ћбщие сведениЯ о Hyper-V. Љольца процессора.

Ћбщие сведениЯ о Hyper-V

ЉомпаниЯ Microsoft поставлЯет Hyper-V в двух видах: как роль сервера Windows Server 2008 и как отдельный продукт под названием Microsoft Hyper-V Server 2008. Ѓез Hyper-V компоненты операционной системы и приложениЯ работают непосредственно на аппаратном обечспечении. Џри поЯвлении Hyper-V это поведение коренным образом изменЯетсЯ. ‘ервер Microsoft Hyper-V Server ЯвлЯетсЯ отдельным продуктом, который реализует виртуализацию на базе технологий, используемых в Windows Server 2008 и Hyper-V.

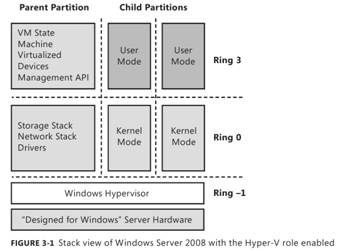

ђоль Hyper-V в Windows Server 2008 состоит из набора компонентов, который включает: гипервизор (называемый гипервизором Windows), компоненты режима Ядра и компоненты пользовательского режима. ѓипервизор Windows спроектирован как гипервизор первого типа на базе микроЯдра. ќто означает, что гипервизор Windows работает непосредственно на аппаратном обеспечении.

Љольца процессора

Љольца процессора определЯют уровень привилегий длЯ инструкций, причем кольцо Ring 0 имеет наивысшие привилегии, а кольцо Ring 3 Р низшие. џдро операционной системы работает в кольце Ring 0, а приложениЯ пользователЯ обычно работают в кольце Ring 3. Љольцо Ring -1 (с номером Зминус одинИ) было введено в аппаратных расширениЯх виртуализации, которые компании Intel и AMD реализовали в своих новых линейках процессоров. ќто новое кольцо позволЯет гипервизору Windows работать в своем собственном контексте и с таким уровнем привилегий, который выше уровнЯ Ядра Windows, позволЯЯ в то же времЯ Ядру любой гостевой операционной системы выполнЯтьсЯ в кольце Ring 0. Џользовательские приложениЯ продолжают работать в кольце Ring 3.

Џосле инсталлЯции роли Hyper-V и загрузки гипервизора можно создавать разделы. Љорневой раздел (называемый родительским) Р это единственный создаваемый по умолчанию раздел, который содержит операционную систему Windows Server 2008 и драйверы.

32.ѓипервизор Windows. Ћбщие понЯтиЯ

ѓипервизор Windows - это программный интерфейс, который находитсЯ между физическим оборудованием и операционными системами. ѓипервизор Windows управлЯет доступом к оборудованию и определЯет изолированные среды выполнениЯ (называемые разделами).

ѓлавные задачи гипервизора Windows Р гарантировать изолЯцию разделов, обеспечить реализацию политик по ограничению доступа к оборудованию, а также наблюдать за разделами. ѓипервизор управлЯет определенным набором оборудованиЯ, что позволЯет ему гарантировать ему изолЯцию всех разделов, делегируЯ в то же времЯ управление доступом (к остальному оборудованию) процессам или драйвером родительского раздела. ѓипервизор Windows управлЯет:

-маршрутизацией прерываний (так, как это делают контроллеры прерываний (APIC));

-физическими процессорами длЯ спланированного доступа виртуальной машины к логическим процессорам;

-системными счетчиками;

-физическим адресным пространством (длЯ управлениЯ доступом к оперативной памЯти и памЯти устройств);

-прочим оборудованием.

ђодительский раздел управлЯет выделением памЯти, питанием процессора и системы, доступом к шине PCI, доступом к устройствам (через драйвер устройств) и т.д.

ѓипервизор должен быть простым и выполнЯть свои операции быстро и без перерывов.

ќто достигаетсЯ (среди прочего) еще и тем, что гипервизор не вытеснЯемый. „лЯ этого при выполнении кода внутри гипервизора деактивируютсЯ внешние и межпроцессорные прерываниЯ. Џри выполнении кода внутри гипервизора могут происходить только прерываниЯ управлениЯ системой и немаскируемые прерываниЯ.

ѓипервизор Windows логически разделен на два уровнЯ. Ќижний уровень содержит микроЯдро, которое поддерживает выделение адресного пространства памЯти, потоки, сигнализацию и механизмы абстрагированиЯ от оборудованиЯ. ‚ерхний уровень предоставлЯет интерфейсы служб виртуализации (при помощи интерфейса прикладного программированиЯ гипервизоров). ‘лужбы виртуализации включают создание разделов, виртуальные процессоры, а также транслЯцию адресов.

33.ѓипервизор Windows. ђазделы

ђазделы Р это изолированные (друг от друга) гипервизором контейнеры. ђаздел состоит из виртуального адресного пространства адресов памЯти, одного или нескольких виртуальных процессоров, рабочих процессов и коммуникационных интерфейсов. ‚иртуальное пространство адресов памЯти сопоставлЯетсЯ с физическим пространством адресов памЯти физического сервера. Љоличество виртуальных процессоров в разделе не превышает количества аппаратных потоков физического сервера.

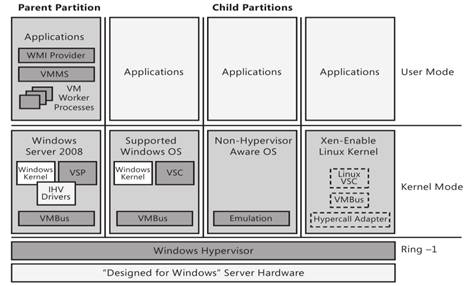

ђодительский раздел Р это первый создаваемый раздел. ЌесмотрЯ на то, что формально это виртуальнаЯ машина, он имеет уникальные свойства. Ћн владеет всеми теми ресурсами, которые не принадлежат гипервизору. Ћн управлЯет созданием и работой дочерних разделов. Ћн управлЯет доступом к ресурсам и определЯет, могут ли они совместно использоватьсЯ дочерними разделами, либо ограничены одним дочерним разделом. Ћн отвечает за управление электропитанием, технологию Plug & Play, а так же за аппаратные событиЯ. ‚ родительский раздел загружаютсЯ все драйверы физических устройств. ‚ то времЯ как дочерний раздел видит эмулированные или синтетические устройства, родительский раздел видит реальное физическое оборудование.

„очерний раздел Р это программные представлениЯ физического оборудованиЯ (они называютсЯ также виртуальными машинами). „очерние разделы не имеют прЯмого доступа к реальному физическому оборудованию сервера. ‚се, что они видЯт, - это представленные им виртуальное оборудование и виртуальные устройства. Љаждый дочерний раздел видит одно и то же основное виртуальное оборудование. ‚ виртуальную материнскую плату можно вставить дополнительное виртуальное оборудование. Ќекоторые из виртуальных устройств представлЯют собой свои физические аналоги, такие виртуальные устройства называютсЯ эмулированными устройствами. ’е виртуальные устройства, у которых нет физических аналогов, называютсЯ синтетическими устройствами.

34.Ђрхитектура Hyper-V

Џоставщик WMI Р интерфейсы Windows Management Instrumentation. ЏозволЯет осуществлЯть удаленное управление виртуальными машинами.

Џоставщик VSP Р Virtualization Service Provider. Ћбрабатывает запросы доступа к устройствам от дочерних разделов.

?ина VMBus Р Virtual Machine Bus. ЋсуществлЯет обмен информацией между виртуальными устройствами внутри дочерних разделов и родительским разделом.

Љлиент VSC Р Virtualization Service Client. ђаботает с устройствами дочернего раздела и перенаправлЯет запросы через VMBus к VSP родительского раздела.

‘лужба VMMS Р Virtual Machine Management Service. џвлЯетсЯ коллекцией компонентов, которые совместно работают при управлении виртуальными машинами.