Тема 4. Анализ и синтез логических схем на микросхемах малой и средней степени интеграции

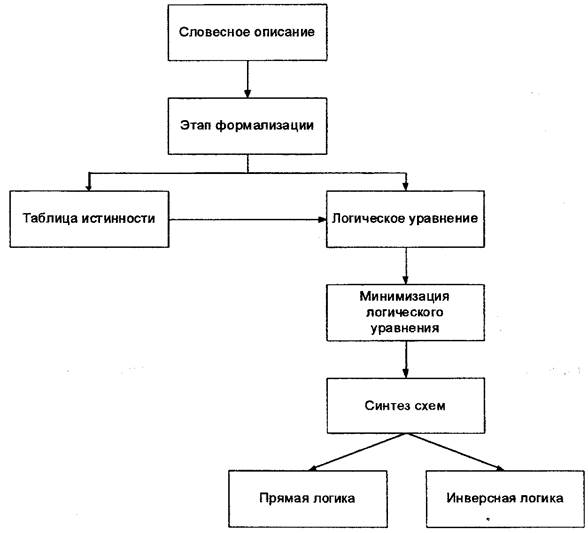

Пример синтеза логической схемы

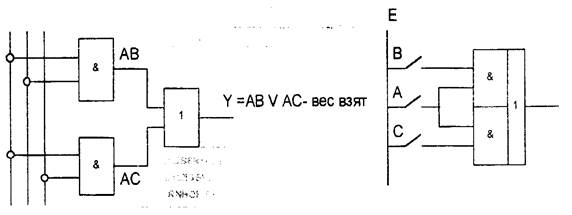

Нужно создать логическое автоматическое устройство для оповещения зрителей о результатах принятия решения судейской коллегии на соревнованиях по тяжелой атлетике. Судейская коллегия состоит из трех судей, один из которых старший -председатель. Если вес взят, то судья нажимает кнопку. Коллективное решение «вес взят» должно появляться при единогласном решении трех судей или двух из них при условии, что один - председатель.

Методологический прием формализации - метод «черного ящика».

Особенность синтеза логических схем с несколькими выходами

В некоторых случаях удается минимизировать логичеcкую схему за счет двоичных элементов, формирующих другие выходы.

у1 = f(a,b) - функция, равная единице в случае, если а>b

у2 = f(a,b) - функция, равная единице в случае, если а≥b

уз = f(а, b) - функция, равная единице в случае, если а<b

Разложение Шеннона

Формула разложения Шеннона:

Последовательное разложение Шеннона:

Если применить метод разложения к нескольким функциям, то можно обнаружить одинаковые подфункции.

Пример:

Имеем схему с двумя выходами:

В результате разложения Шеннона получили две одинаковые подфункции f12 и f21.

Анализ логических схем, построенных на микросхемах малой и средней степени интеграции

Известна логическая схема

Два метода анализа:

1) Построение таблицы истинности

2) Написание логического уравнения

Пример:

По первому способу строим таблицу истинности, подавая на вход различные комбинации входных сигналов, последовательно определяя реакцию промежуточных логических элементов.

Таблица истинности:

По второму способу вводим промежуточные переменные и пишем логические уравнения для каждого логического элемента.

Логическое уравнение:

у = х1х2х3 - минимизированное логическое уравнение

Примечание: Часто при анализе схем встречается задача нахождения уравнений, когда неизвестно внутреннее содержание логической схемы, но известны последовательности входных и выходных сигналов

Задача идентификации решается с помощью методов тестирования. Один из таких методов - табличный метод.

Синтез схем на микросхемах средней степени интеграции

Дешифратор, шифратор, мультиплексор, демультиплексор - представители данного класса схем.

Синтез схем на дешифраторах

Дешифратор - логический многополюсник, который имеет n входов и 2n выходов, причем при подаче на вход двоичной комбинации, возбуждается только один выход, который и указывает на наличие этой комбинации на выходе.

Дешифратор - это преобразователь двоичного кода в десятичный.

Как видно из уравнений выходов уi каждый такой выход является функцией от всех входных сигналов. Это обстоятельство позволяет задавать с помощью дешифратора любую логическую функцию, которая представлена в СДНФ

Синтез комбинационной схемы на дешифраторе сводится к объединению соответствующих выходов дешифратора с помощью дизъюнктора.

Пример:

Преимущества:

1) не нужно минимизировать логическое уравнение

2) этап технологического проектирования значительно упрощается

Недостатки:

1) ограниченное количество входов

2) логическая функция должна быть представлена в СДНФ

3) если функция представлена в ДНФ, то необходимо сначала найти ее СДНФ, что можно сделать двумя способами: либо с помощью таблицы истинности, либо через аналитические преобразования

Пример перехода от ДНФ к СДНФ: