ФУНКЦИОНАЛЬНАЯ И СТРУКТУРНАЯ ОРГАНИЗАЦИЯ ВС

Функциональная организация ВС - это абстрактная модель ВС, описывающая функциональные возможности системы и предоставляемые ею услуги. Определяется

• предъявляемыми к ней требованиями,

• уровнем подготовки потенциальных пользователей,

• типом решаемых ими задач,

• потребностями в развитии компьютера (по емкости ЗУ, производительности, разрядности, составу периферийных устройств и др.).

Предусматриваемые абстрактной моделью функции ВС реализуются на основе реальных, физических средств (устройств, блоков, узлов, элементов) в рамках определенной структуры.

Под структурной организацией ВС понимается некоторая физическая модель, устанавливающая состав, порядок и принципы взаимодействия основных функциональных частей машины (без излишних деталей их технической реализации). По степени детальности различают структурные схемы, составленные на уровне

• устройств,

• блоков,

• узлов,

• элементов.

Функциональная схема ВС

| Упрощённая схема работы ВС

|

Основное устройство, исполняющее команды - процессор

Основное устройство, управляющее ходом выполнения команд - процессор

Устройства управления задачей

•определения адреса следующей команды

•считывание команд из памяти

•дешифрация команд в мопы

•распределение мопов по устройствам обработки

Устройства обработки

• выборка данных по командам/мопам

• исполнение микроопераций

• изменение состояния задачи по результату

• сохранение результата

Внутренняя память процессора

• временное хранение адресов, битов состояния (флагов), кодов команд, мопов, данных, результатов

Функциональная схема процессора

2. Порядок выполнения машинной команды (фазы команды и блоки процессора их выполняющие), конвейер команд (принцип конвейерной обработки, ступени конвейера, причины простоев блоков CPU, пути их устранения

ПОРЯДОК ВЫПОЛНЕНИЯ ОДНОЙ МАШИННОЙ КОМАНДЫ

Фаза 1. Выборка команды – формирование адреса команды, чтение команды из памяти

Фаза 2. Декодирование – расшифровка кода команды и разбиение команды на мопы

Фаза 3. Выборка операндов – формирование адреса данных, чтение данных из памяти

Фаза 4. Исполнения – выполнение над операндами в исполнительных устройствах процессора действий, закодированных мопами

Фаза 5. Запись результата – сохранение результата операции по адресу, определяемому в команде

Фаза 6. Проверка исключений и прерываний появившихся во время исполнения команды

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3. Типы данных ВС (биты, символьные, целые двоичные числа без/со знаком, дробные двоичные числа, BCD, вектора, указатели, теги, дескрипторы), способы хранения многобайтовых элементов данных в памяти компьютера, система команд процессора (типы, формат, назначение полей, число адресов, длина, операнды и режим адресации операндов) на примере процессора Intel.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4. Программная (архитектурная) модель процессора на примере процессора Intel IA64: регистры (РОН, IP, Flags, Float, векторные, служебные), сегментация памяти (сплошная модель и сегментированная)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

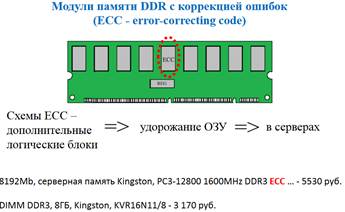

5. Иерархия памяти ВС. Оперативная память: характеристики, тип и принцип действия, расположение в ВС, логическая организация ОЗУ, расслоение памяти, методы защиты памяти, методы повышения эффективности схем ОП

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6. Иерархия памяти ВС. КЭШ-память: характеристики, тип и принцип действия, расположение в ВС, многоуровневая организация (назначение каждого уровня), основные функции КЭШпамяти, типовая структура ассоциативной КЭШ-памяти, виды отображения строк ОП на строки КЭШ, эффективность и методы её повышения

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|