Система параметров

К параметрам, характеризующим логические и схемотехнические возможности ЛЭ микросхем и больших интегральных схем (БИС), относятся:

1. реализуемая логическая функция;

2. нагрузочная способность n, характеризующая возможность подключения определенного числа идентичных ЛЭ (коэффициент разветвления по выходу);

3. коэффициент объединения по выходу m (mи — для реализации логической функции И; mили — для реализации логической функции ИЛИ) (коэффициент объединения по входу);

4. средняя задержка передачи сигнала τср (полусумма времени задержек передачи сигналов 1 и 0 со входа ЛЭ на его выход);

5. предельная рабочая частота fр (частота переключения триггера, составленного из рассматриваемых ЛЭ);

6. помехоустойчивость;

7. потребляемая мощность.

По виду реализуемой логической функции ЛЭ условно могут быть разбиты на два класса. К первому классу относятся функциональные элементы одноступенчатой логики. Это простейшие ЛЭ, реализующие функции И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ. Ко второму классу относятся функциональные элементы двухступенчатой логики, реализующие более сложные функции: И-ИЛИ, ИЛИ-И, НЕ-И-ИЛИ, И-ИЛИ-НЕ, И-ИЛИ-И и др.

Нагрузочная способность ЛЭ n определяет число входов идентичных элементов, которое может быть подключено к выходу каждого из них. При этом обеспечиваются неискаженная передача двоичных символов 0 и 1 в цифровом устройстве по цепи из произвольного числа последовательно включенных элементов при наихудших сочетаниях дестабилизирующих факторов. Дестабилизирующими факторами могут быть: изменение питающих напряжений, разброс параметров компонентов, изменение температуры и т.п.

Часто нагрузочная способность n называется коэффициентом разветвления по выходу (Краз) и выражается целым положительным числом (n=4, 5, 7, 10 и т. д.).

Чем выше нагрузочная способность ЛЭ, тем шире их логические возможности и тем меньше затраты при проектировании и построении цифрового устройства. Однако увеличение параметра n возможно до определенных пределов, поскольку при этом ухудшаются другие параметры ЛЭ: снижается быстродействие, ухудшается помехоустойчивость и увеличивается потребляемая мощность. Обычно в состав одной серии ИМС часто входят ЛЭ с различной нагрузочной способностью: основные ЛЭ с n=4…10 и буферные элементы — так называемые усилители мощности с n=20…50. Это позволяет более гибко проектировать цифровые устройства, достигая оптимальных показателей по потребляемой мощности и числу ЛЭ.

В зависимости от частотного диапазона работы логических МДП-микросхем (металл-диэлектрик-полупроводник) их нагрузочная способность может изменяться в широких пределах (n=10…100).

Коэффициент объединения по входу m (Коб) характеризует максимальное число логических входов функционального элемента. С увеличением параметра m расширяются логические возможности микросхемы за счет выполнения функций с большим числом аргументов на одном типовом элементе И-НЕ, ИЛИ-НЕ и т. п. Однако при увеличении числа входов, как правило, ухудшаются другие параметры функционального элемента, такие как быстродействие, помехоустойчивость и нагрузочная способность.

С точки зрения возможности увеличения коэффициента объединения по входу И или по входу ИЛИ логические схемы существенно отличаются друг от друга. Например, в ИМС где функция первой логической ступени выполняется на диодах или эмиттерных переходах многоэмиттерного транзистора, увеличение числа входов не требует существенных дополнительных затрат площади кристалла. В ИМС, где функция первой логической ступени выполняется на транзисторах, увеличение параметра m требует значительного увеличения числа компонентов ЛЭ и роста площади кристалла ИМС.

В существующих сериях интегральных микросхем основные логические элементы выполняются, как правило, с небольшим числом входов  . Увеличение числа входов m обеспечивается за счет введения в серию ЛЭ специального расширителя, подключение которого к основной ИМС дает возможность увеличить mили и mи до 10 и более.

. Увеличение числа входов m обеспечивается за счет введения в серию ЛЭ специального расширителя, подключение которого к основной ИМС дает возможность увеличить mили и mи до 10 и более.

К основным динамическим параметрам логического элемента относятся:

tф1 — фронт формирования уровня логической 1;

tф0 — фронт формирования уровня логического 0;

τ10 — задержка переключения из состояния 1 в состояние 0;

τ01 — задержка переключения из состояния 0 в состояние 1;

— длительность импульса;

— длительность импульса;

fp — рабочая частота.

Определение этих параметров обеспечивается при сравнении сигналов на входе и выходе ЛЭ, т.е. при рассмотрении процесса передачи информации через ЛЭ.

На рис. 1 приведены характеристики сигналов на входе и выходе инвертора и показаны уровни отчета, относительно которых определяются динамические параметры ЛЭ.

Рис. 1. К определению динамических параметров логического элемента (инвертора)

Уровням отcчета динамических параметров ЛЭ являются (рассматривается положительная логика, при которой высокий уровень выходного сигнала соответствует 1, а низкий — 0) максимальный уровень логического 0 и минимальный уровень логической 1. Задержка переключения τ10 определяется как временной интервал между уровнем 1 фронта нарастания входного импульса (положительный импульс) и уровнем 0 фронта спада выходного импульса (отрицательный импульс).

Задержка переключения τ01 определяется как временной интервал между уровнем 0 фронта спада входного импульса и уровнем 1 фронта нарастания выходного импульса.

Фронты импульса, определяемые между уровнями 1 и 0 спада импульса, обозначаются tф0, между уровнями 0 и 1 нарастания импульса — tф1.

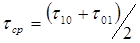

Средняя задержка τср ЛЭ определяется как полусумма задержек τ10 и τ01 и служит усредненным параметром быстродействия, используемым при расчете временных характеристик многоэлементных последовательно включенных логических микросхем.

Произведение средней задержки на число последовательно соединенных ЛЭ в устройстве дает наибольшую задержку сигнала в этом устройстве. Параметр τср приводится в технических условиях на ИМС. Для упрощения процесса расчета временных характеристик сложных логических цепей часто считают сигналы прямоугольными, т. е. tф0= tф1=0.

Помехоустойчивость. Базовый элемент ИМС в статическом режиме может находиться в одном из двух устойчивых состояний (0 или 1). По этой причине различают статическую помехоустойчивость ЛЭ по уровню 0 (Uno)и по уровню 1 (Un1). Статическая помехоустойчивость базовых элементов ИМС определяется значением напряжения, которое может быть подано на вход ИМС относительно уровня 0 или 1, не вызывая её ложного срабатывания (например, переход из состояния 1 в состояние 0 или наоборот).

Напряжение помехи либо повышает, либо понижает входное напряжение. Если на входе действует напряжение логического 0 (U0), то опасны помехи, имеющие положительную полярность, так как они повышают входное напряжение, что может привести к сбою в работе, т. е. ложному изменению выходных напряжений в цифровом устройстве. При поступлении на вход напряжения логической 1 (U1) и напряжения помехи отрицательной полярности также возможно ложное переключение. Максимально допустимые постоянные напряжения помехи положительной полярности (при напряжении логического 0 на входе) и отрицательной полярности (при напряжении логической 1 на входе) определяют помехоустойчивость ЛЭ по отношению к статическим (длительно действующим) помехам.

Внутренние помехи в цифровом устройстве возникают при переключении ЛЭ, поэтому их амплитуда пропорциональна логическому перепаду Uл.

Логическим перепадом называется разность напряжений логической 1 и логического 0:

.

.

Для оценки помехоустойчивости ЛЭ помимо напряжений Uп1 и Uп0 используют относительные величины:

;

;  ,

,

называемые коэффициентом помехоустойчивости.

Для повышения помехоустойчивости необходимо увеличивать логический перепад и уменьшать время переключения ЛЭ из состояния 1 в состояние 0 и наоборот.

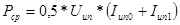

Потребляемая мощность ЛЭ (мощность, потребляемая ЛЭ от источника питания) зависит от его логического состояния, так как изменяется ток Iи.п. в цепи питания. ЛЭ потребляет ток

при

при  ;

;

при

при  .

.

Поэтому средняя потребляемая мощность в статическом режиме.

.

.

Зная среднюю мощность и число ЛЭ в цифровом устройстве Nл.э., можно вычислить среднюю мощность, потребляемую устройством; она равна  . Уменьшить потребляемую мощность можно, снизив напряжение или ток питания. Однако при этом понизятся помехоустойчивость, а для многих типов ЛЭ и быстродействие. Наиболее эффективный способ уменьшения мощности Pср реализован в ЛЭ на КМДП-транзисторах (комплементарный металл-диэлектрик-полупроводник). В этих элементах токи в статическом режиме малы, а мощность потребляется только при переключении. Мощность, потребляемую дополнительно в процессе переключения, называют динамической. Она пропорциональна частоте переключения ЛЭ. Поэтому динамическую мощность определяют при заданной рабочей частоте, близкой к максимальной.

. Уменьшить потребляемую мощность можно, снизив напряжение или ток питания. Однако при этом понизятся помехоустойчивость, а для многих типов ЛЭ и быстродействие. Наиболее эффективный способ уменьшения мощности Pср реализован в ЛЭ на КМДП-транзисторах (комплементарный металл-диэлектрик-полупроводник). В этих элементах токи в статическом режиме малы, а мощность потребляется только при переключении. Мощность, потребляемую дополнительно в процессе переключения, называют динамической. Она пропорциональна частоте переключения ЛЭ. Поэтому динамическую мощность определяют при заданной рабочей частоте, близкой к максимальной.

Интегральные элементы одноступенчатой логики

Логические элементы микросхем потенциального типа с одноступенчатой логикой по схемотехнической реализации и организации межэлементных связей делятся на следующие типы:

· резисторно-транзисторные (RTL[1]);

· транзисторные с непосредственной связью (DCTL);

· транзисторные с резистивными связями (TRL);

· транзисторные с резистивно-конденсаторными связями (RCTL);

· комплементарные с транзисторно-резистивной логикой (CRTL);

· диодно-транзисторные (DTL);

· транзисторные с эмиттерными связями (ECL);

· транзисторные с инжекционной логикой (И2Л).