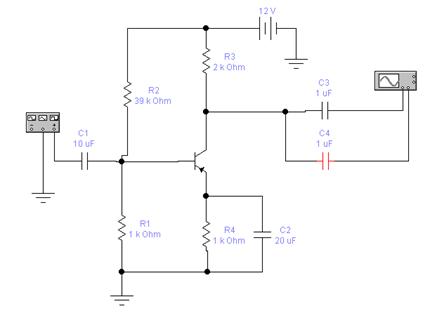

1. Собрать схему, изображенную на рисунке 4

Рис. 4

2. Установите значения на генератора согласно рисунку 5

Рис.5

3. Зарисовать осциллограмму усиленного синусоидального сигнала на выходе усилителя

4. Снять амплитудно-амплитудную характеристику усилителя(прим. рис. 2). Для этого, изменяя величину амплитуды на генераторе от 0 до 100 мВ, измерить величину выходного сигнала усилителя. Измерение производить с помощью осциллографа. Данные, полученные в результате измерения на входе и выходе усилителя занести в таблицу 1 и по ним построить график зависимости UВЫХ усилителя от UВХ.

Таблица 1

| F = const = 1000 Гц | |||||||

| № изм | |||||||

| UВХ ср1 | |||||||

| UВЫХ1 | |||||||

| UВЫХ2 |

5. Снять и построить АЧХ исследуемого усилителя(прим. рис. 3). Для этого, необходимо изменять частоту f входного напряжения от 50 Гц до 500кГц при UВX = const = 0,8UВХ max. Выходное напряжение измерять на выходах разделительных конденсаторов С3 и С4: Результаты измерений занести в таблицу 2. Амплитуда Ubx должна сохранятся постоянной на всех контролируемых частотах (UBX = const).

Таблица 2

| UВХ = const = мВ | |||||||||

| Частота f, Гц | |||||||||

| lg f | 1,7 | 2,7 | 4,7 | 5,3 | 5,7 | ||||

| UВЫХ С3 | |||||||||

| UВЫХ С4 |

6. Определить полосу пропускания усилителя (f нижнее; f верхнее), для чего от уровня UВЫХ max отнять 3дБ (примерно 0,71 UВЫХ max) и из точек пересечения уровня 0,71 UВЫХ max с частотной характеристикой опустить перпендикуляры на ось х (частота f Гц) и определить fН и fВ.

7. По построенной амплитудной характеристике определить коэффициент усиления по напряжению, для чего на линейном участке характеристики подсчитать отношение ΔUВЫХ,mB/ΔUВХ,mB=К4, а также определить динамический диапазон данного усилителя от UВХmin до UВХmax при условии неискаженной формы усиленного сигнала.

|

|

Контрольные вопросы

1. Для чего предназначены каскады предварительного усиления?

2. Каковы основные требования к каскадам предварительного усиления?

3. По какой схеме подключаются транзисторы в каскаде предварительного усиления и почему?

4. Приведите схему усилительного каскада с ОЭ?

5. Что такое амплитудная и амплитудно-частотная характеристика?

ЛАБОРАТОРНАЯ РАБОТА №5

Исследование шифраторов и дешифраторов

ЦЕЛЬ РАБОТЫ: ознакомление с принципом работы шифраторов и дешифраторов. Изучить принцип работы устройств кодирования и декодирования информации.

СОДЕРЖАНИЕ ОТЧЕТА:

1. Цель работы

2. Описание экспериментов

3. Выполненные задания

4. Ответы на контрольные вопросы

5. Вывод

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

Шифраторы и дешифраторы являются основными устройствами преобразования информации. При этом шифратор преобразует код «1 из N» в двоичный код, а дешифраторы, наоборот, из двоичного кода в код «1 из N». Так как число разрядов двоичного числа меньше N, условно такую операцию можно назвать сжатием данных. Шифратор и дешифратор являются КЦУ, т.к. не имеют элементов памяти. Поэтому для них существует возможность задания связи выходного сигнала с входным в виде таблицы истинности, или же логической функции.

|

|

Для синхронизации выходных сигналов этих преобразователей тактовыми импульсами используют дополнительные входы. Такие преобразователи называются стробируемыми. Стробирование – это выделение сигнала в определенный момент времени.

Рис. 11.2. Дешифратор «1 из 8».

Сфера применения дешифраторов – устройства индикации, управления, коммутаторы, служащие для распределения сигнала по различным цепям.

Различают полные и неполные дешифраторы (рис. 11.2, табл. 11.1). Число выходов у полного дешифратора Nвых = 2n, а у неполного Nвых < 2n, где n – число двоичных разрядов (входов). Существует два способа стробирования дешифраторов: введением дополнительного входа в каждый элемент (стробирование по выходу – рис. 11.2, б) и блокирование всех элементов через одну из выходных цепей (стробирование по входу – рис. 11.2, в).

Таблица 11.1. Таблица истинности дешифратора «1 из 8».

| Входная кодовая комбинация | Сигнал на выходе | |||||||||||

| C | x1 | x2 | x3 | Y0 | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | |

| Любые комбинации нулей и единиц |

Шифратор – это КЦУ, которое преобразует код «1 из N» в двоичный код. Полный шифратор имеет 2n входов и n выходов. Сфера применения шифраторов – ввод данных с клавиатуры, при котором нажатие на клавишу с десятичной цифрой должно приводить к передаче в устройство этой цифры в двоичном коде. При нажатии любой из десяти цифровых клавиш единица появляется только на одном из десяти входов шифратора X0, X1,…, X9. На выходе шифратора должен появиться двоичный код (y0y1y2y3) введенного десятичного числа. Из табл. 11.3 видно, что в этом случае нужен преобразователь с десятью входами и четырьмя выходами, т.е. так называемый шифратор «10-4».

|

|

На выходе y0 единица должна появиться при нажатии любой нечетной клавиши (X1, X3,X5,X7,X9), т.е.

;

;

;

;

;

;

.

.

Таблица 11.3. Таблица истинности шифратора «10 - 4».

| Десятичное число | Сигнал на входе | Выходная кодовая комбинация | |||||||||||||

| X0 | X1 | X2 | X3 | X4 | X5 | X6 | X7 | X8 | X9 | y3 | y2 | y1 | y0 | ||

3.1. Реализовать дешифратор «1 из 8» в соответствии с таблицей истинности табл. 11.1, проверить правильность его работы.

3.2. Реализовать преобразователь двоично-десятичного кода в код «3 из 5» в соответствии с таблицей истинности табл. 11.2, проверить правильность его работы.

3.3. Реализовать шифратор «10 - 4» в соответствии с таблицей истинности табл. 11.3, проверить правильность его работы.

Ход выполнения работы должен быть отражен в отчете по выполнению лабораторной работы.

Контрольные вопросы.

- Что называется шифратором?

- Что называется дешифратором?

3. Что такое стробирование?

4. Что называется полным и неполным дешифратором?

5. Что называется полным шифратором?

ЛАБОРАТОРНАЯ РАБОТА №6

Исследование цифровых компараторов

ЦЕЛЬ РАБОТЫ: ознакомление с принципом работы цифрового компаратора.

СОДЕРЖАНИЕ ОТЧЕТА:

1. Цель работы

2. Описание экспериментов

3. Выполненные задания

4. Ответы на контрольные вопросы

5. Вывод

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

Компараторы используются для сравнения двух сигналов и, в случае если эти сигналы не равны, позволяют определить больший из них. Цифровой компаратор необходим для сравнения двух двоичных чисел. В табл. 12.1 указаны выходные сигналы цифрового компаратора при поступлении на его входы 1 или 0.

Таблица 12.1. Таблица истинности цифрового компаратора.

| Входы | Выходы | |||

| a | b | Fa>b | Fa=b | Fa<b |

По известным правилам на основании табл. 12.1 можно записать следующие логические функции, характеризующие соотношение одноразрядных чисел:

;

;  ;

;  .

.

Если значения a и b таковы, что правая часть функции равна 1, то соотношение, указанное в левой части, выполняется. Если правая часть функции равна 0, то соотношение между a и b противоположно указанному.

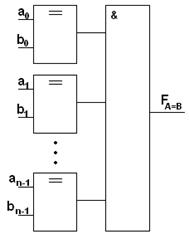

Схема одноразрядного компаратора, реализующая приведенные функции, показана на рис. 12.1.

Рис. 12.1. Схема цифрового одноразрядного компаратора.

Рассмотрим боле подробно функцию равенства чисел Fa=b, или функцию «Равнозначность». По смыслу данная функция противоположна функции Fa≠b «Неравнозначность». Т.к.  , то

, то  .

.

Поэтому проверку равенства пары одноименных разрядов двух двоичных чисел можно осуществлять с помощью элемента «Равнозначность» (рис. 12.2).

Рис. 12.2. Условное обозначение элемента «Равнозначность».

При этом два двоичных числа A и В равны, если в одноименных разрядах образующих их чисел находятся одинаковые цифры (a0=b0 И a1=b1 И … an-1=bn-1), или:

Рис. 12.3. Поразрядное сравнение.

Когда цифры в одноименных разрядах чисел А и В одинаковы, на выходах всех элементов «Равнозначность» (рис. 12.3) появляются 1, и значит FA=B=1. Если же хотя бы в одной из пар сравниваемых разрядов цифры различны, то на выходе элемента «Равнозначность» появится логический 0 и FA=B=0, а значит А и В не равны.

Порядок выполнения работы

Реализовать цифровой одноразрядный компаратор в соответствии со схемой, представленной на рис. 12.1, проверить правильность его работы.

Реализовать логический элемент «Равнозначность», проверить правильность его работы. Для этого, используя известное выражение:

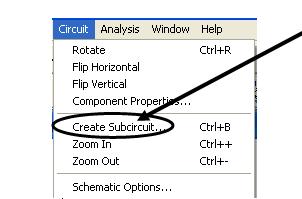

Для этого необходимо составить его схему и преобразовать ее в отдельный элемент. Этого делается с помощью пункта «Create Subcircuit» меню «Circuit» (рис. 12.4). Собрав схему, выделяем образующие ее логические элементы «мышью» и создаем элемент.

Рис. 12.4. Меню «Circuit ».

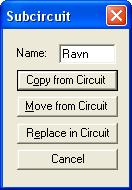

В поле «Name» появившегося диалога задаем имя элемента и создаем его. При этом если ввести имя уже существующего элемента, то с ним можно проделать ряд операций, например, изменить схему.

Рис. 12.5. Задание имени элемента.

Рис. 12.6. Инструмент «Favorites».

Вновь созданный элемент попадает в панель «Favorites » и становится доступным для работы с ним.

Увеличить количество входов логического элемента можно, установив необходимое их количество на закладке «Number of inputs » окна свойств, вызываемых двойным щелчком мыши на элементе.

Реализовать схему поразрядного сравнения двух двоичных чисел в соответствии со схемой, представленной на рис. 12.3, проверить правильность ее работы.

Контрольные вопросы.

- Что такое компаратор?

2. Как и с помощью какого элемента осуществляется поразрядное сравнение двоичных чисел?

ЛАБОРАТОРНАЯ РАБОТА №7

Исследование сумматоров

ЦЕЛЬ РАБОТЫ: ознакомление с принципом работы сумматора.

СОДЕРЖАНИЕ ОТЧЕТА:

1. Цель работы

2. Описание экспериментов

3. Выполненные задания

4. Ответы на контрольные вопросы

5. Вывод

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

Сумматор представляет собой комбинационное цифровое устройство (КЦУ), предназначенное для суммирования двоичных чисел, хотя с его помощью можно выполнять и другие операции.

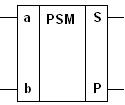

Полусумматорами (рис. 10.1 а-б) называют КЦУ с двумя входами (a,b) и двумя выходами, на одном из которых вырабатывается сигнал суммы (выход S), а на другом – сигнал переноса (выход Р). В табл. 10.1 представлена таблица истинности полусумматора.

а) условное обозначение; б) схема полусумматора.

Рис. 10.1. Полусумматор.

Таблица 10.1. Таблица истинности полусумматора.

| A | b | S | P |

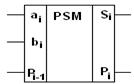

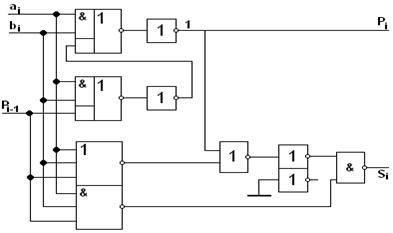

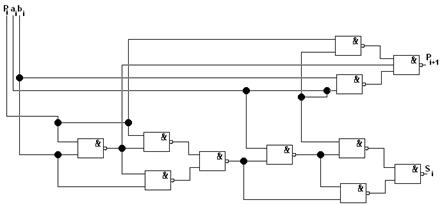

Одноразрядным сумматором (рис. 10.2 а-б) называют КЦУ с тремя входами и двумя выходами. Кроме двух входов для чисел, он имеет третий вход, на который подается сигнал переноса из предыдущего разряда. Одноразрядный сумматор является основным элементом многоразрядных сумматоров. Он выполняет арифметическое сложение одноразрядных двоичных чисел ai и bi и переноса Pi-1 из предыдущего разряда, с образованием на выходе суммы Si и переноса Pi в старший разряд. Отметим некоторые особенности логики работы сумматоров:

- сумма равна 1, если единичные значения принимает нечетное число аргументов;

- выходной перенос равен 1, если единичные значения принимают больше двух аргументов.

а) условное обозначение;

б) схема одноразрядного сумматора.

Рис. 10.2. Одноразрядный сумматор.

Таблица 10.2. Таблица истинности одноразрядного сумматора.

| ai | bi | Pi-1 | Si | Pi |

Рис. 10.3. Схема одноразрядного двоичного сумматора.

Булевы функции, описывающие работу одноразрядного двоичного сумматора (по табл. 10.2), можно записать в следующем виде:

Используя различные варианты преобразования этих функций, можно реализовать большое число структур одноразрядные двоичных сумматоров (например, рис. 10.3).

Задания для выполнения лабораторной работы.

Собрать схему, изображенную на рис. 10.1.

Собрать схему, изображенную на рис. 10.2.

Собрать схему, изображенную на рис. 10.3.

Ход выполнения работы должен быть отражен в отчете по выполнению лабораторной работы.

Контрольные вопросы.

- Что называется сумматором?

- Что называется полусумматором?

- Приведите схемы одноразрядного двоичного сумматора.

ЛАБОРАТОРНАЯ РАБОТА №8

Исследование мультиплексоров и демультиплексоров

ЦЕЛЬ РАБОТЫ: ознакомление с принципом работы мультиплексора и демультиплексора.

СОДЕРЖАНИЕ ОТЧЕТА:

1. Цель работы

2. Описание экспериментов

3. Выполненные задания

4. Ответы на контрольные вопросы

5. Вывод

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

Коммутатор – устройство, переключающее электрические цепи. В основном в вычислительной техничке используются два типа коммутаторов: осуществляющие подключение с нескольких входов на один выход, и, наоборот, с одного входа на несколько выходов.

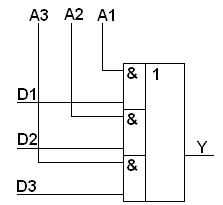

Коммутатор типа «несколько входов – один выход» (рис. 13.1, а) дает возможность подключать канал Y к разным источникам информации (D1, D2, D3). Выбор присоединяемого источника (одного из информационных входов коммутатора) осуществляется сигналом на адресном входе. При этом информация будет поступать из того канала, на элемент И которого подается разрешение в виде логической 1 с одного из адресных входов А1, А2, А3. Рассмотренный нами коммутатор выполнен на одной микросхеме, содержащей в корпусе три элемента И, выходы которых соединены с входами элемента ИЛИ.

Аналогичную задачу решает мультиплексор – коммутатор, в котором выбор входа по его номеру (адресу) осуществляется двоичным кодом.

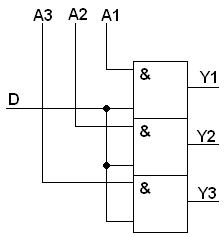

На рис. 13.1, б приведен коммутатор типа «один вход – несколько выходов», который позволяет подключать канал источника цифровой информации D к разным каналам на выходе (Y1, Y2, Y3). Выбор выходного канала осуществляется подачей логической 1 с одного их адресных входов А1, А2, А3, активизирующей соответствующий конъюнктор. Коммутатор выполнен на одной микросхеме, содержащей в одном корпусе несколько элементов И.

Аналогичную задачу решает демультиплексор. В отличие от коммутатора выбор выхода демультиплексора осуществляется кодом, подаваемым на все адресные входы.

Сфера применения мультиплексора (рис. 13.2) - использование для записи в регистры кодов, которые поступают из разных запоминающих устройств или устройств ввода. В цифровой телефонии он широко используется для передачи большого количества телефонных разговоров по одному каналу связи.

а) несколько входов – один выход;

б) один вход – несколько выходов.

Рис. 13.1. Типы коммутаторов.

В системах автоматического управления – для подачи выходных сигналов от нескольких источников (например, датчиков измерения температуры) к одному приемнику (показывающему прибору). При этом подсоединение к источникам сигналов производится последовательно (системы обегающего контроля) или адресно – по выбору оператора.

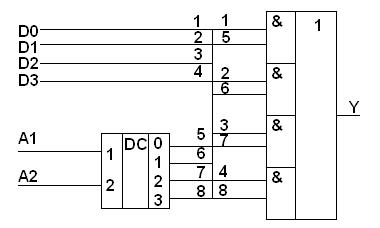

Рис. 13.2. Мультиплексор.

Показанный на рис. 13.2 мультиплексор позволяет подключать к выходу Y один из четырех информационных входов D0, D1, D2, D3.

Выбор информационного входа осуществляется подачей на два адресных входа А1 и А2 соответствующего кода: 00, 01, 10, 11. Например, при подаче на адресные входы сигнала 11 (т.е. десятичная тройка) на выходе 3 дешифратора DC появляется 1, которая по входу 8 поступает на двухвходовый логический элемент И. На другой вход этого элемента поступает информационный сигнал по каналу D2.

Значит, именно третий информационный вход будет подсоединен к выходу Y мультиплексора. Мультиплексор позволяет передавать информацию по одному каналу связи от нескольких источников, но не одновременно. Следовательно, можно сказать, что выход Y представляет собой канал с временным разделением сигналов.

После получения информации по такому единственному каналу связи Y ее необходимо разделить между соответствующими приемниками информации.

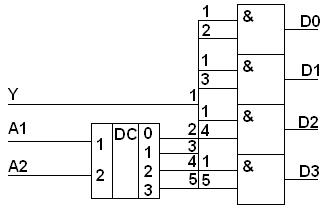

Рис. 13.3. Демультиплексор.

Эту задачу решает демультиплексор (рис. 13.3). Выбор соответствующего информационного выхода осуществляется с помощью адресного входа. Как и в схеме мультиплексора, используется дешифратор DC.

Например, при подаче на адресные входы А1 и А2 сигнала 10 на выходе 2 появляется 1 и входной сигнал Y проходит на информационный выход D2

Рис. 13.4. Цифровые элементы «Electronics Workbench».

Задания для выполнения лабораторной работы.

Реализовать коммутатор «несколько входов – один выход» в соответствии со схемой, представленной на рис. 13.1, а, проверить правильность его работы.

Реализовать коммутатор «один вход – несколько выходов» в соответствии со схемой, представленной на рис. 13.1, б, проверить правильность его работы.

Реализовать мультиплексор в соответствии со схемой, представленной на рис. 13.2, проверить правильность его работы.

Реализовать демультиплексор в соответствии со схемой, представленной на рис. 13.3, проверить правильность его работы.

Контрольные вопросы.

- Что называется коммутатором?

2. Объясните принцип работы коммутатора «несколько входов – один выход».

3. Объясните принцип работы коммутатора «один вход – несколько выходов».

4. Для чего нужны мультиплексор и демультиплексор, в чем разница между ними?

5. Объясните принцип работы мультиплексора.

6. Объясните принцип работы демультиплексора.

7. Назовите основные сферы применения мультиплексора и демультиплексора.

ЛАБОРАТОРНАЯ РАБОТА №9

Исследование триггеров

ЦЕЛЬ РАБОТЫ: ознакомление с принципом работы RS- и D-триггеров

СОДЕРЖАНИЕ ОТЧЕТА:

1. Цель работы

2. Описание экспериментов

3. Выполненные задания

4. Ответы на контрольные вопросы

5. Вывод

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

Триггер является основным устройством, способным запоминать информацию. Он имеет два устойчивых состояния – 1 или 0. Наибольшее распространение получили полупроводниковые триггеры, выпускаемые в виде интегральных микросхем и представляющие собой двухкаскадные усилители постоянного тока с положительной обратной связью.

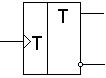

Рис. 7.1. Цифровые элементы «Electronics Workbench».

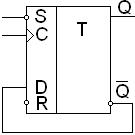

а) RS-триггер; б) D-триггер;

Рис. 7.2. Условные обозначения.

Перевод триггера из одного состояния в другое осуществляется подачей положительных или отрицательных импульсов на коллектор одного или другого транзистора. При этом один из двух имеющихся входов принимают устанавливающим триггер в состояние 1 и называют S входом (от англ. Set - установить), а другой, устанавливающий (сбрасывающий) триггер в состояние 0, называют входом R (от англ. Reset - сбросить). Такой триггер получил название RS-триггера (рис. 7.1). Его условное обозначение показано на рис. 7.2 (а).

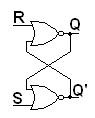

RS-триггеры обычно строятся на двух базовых логических элементах – либо «ИЛИ-НЕ», рис. 7.3 (а), либо на двух «И-НЕ». Поясним работу этого триггера.

а) схема; б) диаграмма сигналов.

Рис. 7.3. RS-триггеры на базе «ИЛИ-НЕ».

После поступления сигнала 1 на вход S триггер переключается в состояние 1, если он был в состоянии 0, или сохраняет 1 на выходе Q, если он уже находился в этом состоянии. Соответственно при поступлении 1 на вход R триггер переключается в 0 или сохраняет это состояние. Исходное состояние триггера (сразу после включения и при отсутствии сигналов 1 на входах S и R) не определено, оно является случайной величиной. Таким образом, триггер работает в соответствии с таблицей истинности, приведенной в табл. 7.1.

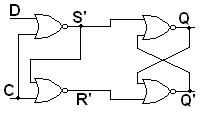

Триггеры разделяются по способу записи информации на асинхронные и синхронные. Состояние (выходной сигнал) асинхронного триггера может изменяться в любой момент – тогда, когда придет входной сигнал. В синхронном триггере состояние может меняться только в определенные моменты времени – тогда, когда поступает дополнительный синхронизирующий сигнал. RS-триггер является асинхронным. На его базе может быть построен синхронный D-триггер (рис. 7.2 б).

Таблица 7.1. Состояние выходов RS-триггеров.

| S | R | Q | Q’ |

| без изменений | без изменений | ||

| не определено | не определено |

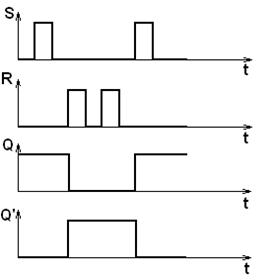

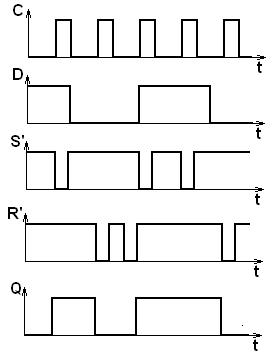

Сигналы, предназначенные для записи в триггер, поступают на информационный вход D. Сигналы, определяющие момент записи, поступают на вход С. Изменение состояния статического D-триггера возможно только в течение того времени, когда С=1. Если же на вход С поступает сигнал 0, то изменение сигнала на выходе триггера не происходит, он сохраняет предыдущее состояние. На диаграмме сигналов (рис. 7.5) видно, что по окончании первого синхроимпульса на информационный вход D поступал уже сигнал 0, однако состояние триггера, соответствующее этому сигналу, возникло только тогда, когда пришел второй синхроимпульс.

Рис. 7.4. Схема синхронного D-триггера.

Аналогичным образом состояние 1 на выходе Q сохранялось от третьего до пятого синхроимпульса, хотя сигнал 1 на выходе D сменился на сигнал 0 раньше, чем пришел пятый синхроимпульс. Поскольку такой триггер задерживает выходной сигнал до прихода очередного синхроимпульса, он получил название D-триггер (от англ. Delay - задержка).

Рис. 7.5. Диаграмма сигналов синхронного D-триггера.

Задания для выполнения лабораторной работы.

Используя Word Generator, Red Probe и RS-триггер собрать схему, которая иллюстрирует работу RS-триггера.

Используя Word Generator, Red Probe и D-триггер собрать схему, которая иллюстрирует работу D-триггера.

Контрольные вопросы.

- Что называется триггером?

- Объясните принцип работы RS-триггера.

- Объясните принцип работы D-триггера.

ЛАБОРАТОРНАЯ РАБОТА №10

Исследование регистров

ЦЕЛЬ РАБОТЫ: ознакомление с принципом работы параллельного и последовательного регистров.

СОДЕРЖАНИЕ ОТЧЕТА:

1. Цель работы

2. Описание экспериментов

3. Выполненные задания

4. Ответы на контрольные вопросы

5. Вывод

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

Регистр представляет собой набор триггеров, число которых соответствует числу разрядов запоминаемого слова. Регистр используется для хранения n-разрядного слова и выполнения над ним логических преобразований. При этом в регистре могут выполняться следующие микрооперации:

· прием (запись) слова;

· передача слова в другой регистр;

· поразрядные логические операции;

· сдвиг слова влево или вправо на заданное число разрядов;

· преобразование последовательного кода слова в параллельный и обратно;

· установка регистра в начальное состояние (сброс).

Кроме того, регистр может осуществлять преобразование двоичного кода из прямого в обратный (когда единицы заменяются нулями, а нули – единицами), и наоборот.

В каждом из триггеров, составляющих регистр, хранится соответствующая цифра разряда числа. Поэтому по способу ввода и вывода разряда числа регистры разделяются на параллельные, последовательные и параллельно-последовательные.

В параллельном регистре ввод или вывод слова осуществляется одновременно для всех разрядов. В последовательном регистре разряды числа вводятся и выводятся последовательно один за другим. В параллельно-последовательном регистре ввод осуществляется в параллельной форме, а вывод в последовательной, или наоборот.

Рис. 8.1. Цифровые элементы «Electronics Workbench».

Функциональная схема параллельного регистра на RS-триггерах приведена на рис. 8.2. Подготовка к приему информации (обнуление триггеров) составляет первый такт. Во втором такте по сигналу «1», подаваемому по шине П (прием), двоичное число x1x2x3x4 всеми разрядами одновременно (параллельно) через конъюнкторы (элементы И) записывается в разряды регистра. Выдача сигнала в прямом коде осуществляется по сигналу, подаваемому по шине Впр, в обратном - Вобр.

В последовательных регистрах двоичное число вводится и выводится последовательно разряд за разрядом. Разряды самого регистра соединены последовательно. Каждый разряд выдает информацию в следующий разряд и одновременно принимает новую информацию из предыдущего. Для этого каждый разряд должен иметь два запоминающих элемента, т.е. двухступенчатый триггер. Двухступенчатый триггер (например, JK-триггер, D-триггер) представляет собой совокупность двух запоминающих элементов. Если в цепи таких триггеров выходы одного соединить с входами другого, то по фронту тактового импульса, подаваемого на вход С, во входную (первую) ступень каждого триггера будет заноситься информация из выходной (второй) ступени предыдущего триггера, а по спаду импульса она будет переписываться в выходную ступень.

Рис. 8.2. Схема параллельного регистра на RS-триггерах.

Рис. 8.3. Условное обозначение 8-битного параллельного регистра (74165).

Функциональная схема последовательного регистра приведена на рис. 8.4. Разряды двоичного числа, начиная с младшего, последовательно поступают на входы старшего разряда регистра. Поступление разрядов числа на входы J и K чередуются с поступлением импульсов сдвига на входы С, которыми вводимые разряды продвигаются вдоль регистра, пока младший разряд n-разрядного числа не окажется в младшем разряде регистра.

Рис. 8.4. Функциональная схема последовательного регистра.

Для выдачи записанного числа в последовательной форме надо на выходы старшего разряда регистра подать xi=0, xi=1, а на шину импульсов сдвига – n импульсов. Первый импульс выдвинет из младшего разряда регистра младший разряд числа, на его место передвинется второй разряд числа и. т.д. В итоге все число сдвинется вдоль регистра на один разряд, а в старший разряд регистра будет записан 0. После n импульсов сдвига число будет полностью выведено из регистра, а его разряды окажутся заполнены 0.

Для выдачи записанного числа в последовательной форме надо на выходы старшего разряда регистра подать xi=0, xi=1, а на шину импульсов сдвига – n импульсов. Первый импульс выдвинет из младшего разряда регистра младший разряд числа, на его место передвинется второй разряд числа и. т.д. В итоге все число сдвинется вдоль регистра на один разряд, а в старший разряд регистра будет записан 0. После n импульсов сдвига число будет полностью выведено из регистра, а его разряды окажутся заполнены 0.

Задания для выполнения лабораторной работы.

Собрать схему, изображенную на рис. 8.2 и записать в нее двоичное число от 0000 до 1111 в соответствии с выражением n+1, где n – номер варианта. Результаты на выходе регистра должны быть получены в прямом и обратном кодах.

Ход выполнения работы должен быть отражен в отчете по выполнению лабораторной работы.

Контрольные вопросы.

- Что называется регистром и для чего он необходим?

- В чем заключаются отличия параллельного, последовательного и параллельно-последовательного регистров.

- Объясните принцип работы параллельного регистра.

- Объясните принцип работы последовательного регистра.

ЛАБОРАТОРНАЯ РАБОТА №11

Исследование счётчиков

ЦЕЛЬ РАБОТЫ: ознакомление с принципом работы счётчика импульсов.

СОДЕРЖАНИЕ ОТЧЕТА:

1. Цель работы

2. Описание экспериментов

3. Выполненные задания

4. Ответы на контрольные вопросы

5. Вывод

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

Счетный триггер, или Т-триггер, который показан на рис. 9.1. (а) имеет два выхода и один вход. При положительном перепаде напряжения на счетном входе Т-триггера сигналы на его выходах меняются на противоположные. В качестве основы построения счетного триггера может быть использован динамический D-триггер. При этом его инверсный выход должен быть соединен с информационным входом (рис. 9.1 б).

а) условное обозначение; б) схема на D-триггере;

Рис. 9.1. Счетный триггер.

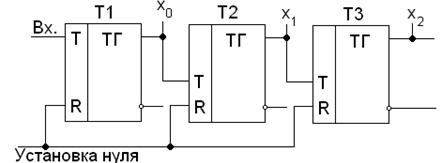

Рассмотрим простой трехразрядный двоичный счетчик импульсов, состоящий из трех Т-триггеров, которые имеют входы R для установки нуля (рис. 9.2).

В исходном состоянии все триггеры находятся в 0 состоянии (рис. 9.3.). После подачи первого входного импульса триггер Т1 переходит в состояние 1, а после второго в состояние 1 переходит Т2, а Т1 возвращается в состояние 0 и. т.д.

Рис. 9.2. Трехразрядный двоичный счетчик импульсов.

Рис. 9.3. Диаграммы сигналов в счетчике импульсов.

Из табл. 9.1 видно, что по состоянию триггеров можно определить сколько импульсов было подано на вход счетчика. В общем случае емкость счетчика равна 2n, где n – число триггеров в счетчике.

Таблица 9.1. Состояние триггеров счетчика импульсов.