I: {{241}}; К=А

S: Электронным ключом называется устройство предназначенное для

+:бесконтактной коммутации электрических цепей

-: запуска блокинг-генератора

-: запуска ждущего мультивибратора

-: запуска фантострона

I: {{242}}; К=А

S: Режимами работы транзисторного ключа является режим

-: активный

-: отсечки

-: насыщения

+:отсечки и насыщения

+:отсечки и насыщения

I: {{243}}; К=В

S:На рисунке изображена схема

+:транзисторного ключа

-: мультивибратора

-: триггера

-: фантастрона

I: {{244}}; К=В

S:При работе транзистора в режиме насыщения электронный ключ

+: замкнут

-: разомкнут

-: находится в неопределенном состоянии

-: этот режим не является рабочим для электронного ключа

I: {{245}}; К=В

S: При работе транзистора в режиме отсечки электронный ключ

-: замкнут

+: разомкнут

-: находится в неопределенном состоянии

-: этот режим не является рабочим для электронного ключа

I: {{246}}; К=В

S: На рисунке изображена схема, реализующая логическую операцию

S: На рисунке изображена схема, реализующая логическую операцию

+: НЕ

-: И

-: ИЛИ

-:И-НЕ

I: {{247}}; К=В

S: На рисунке изображена схема, реализующая логическую операцию

-: НЕ

-: НЕ

-: И

-: 2ИЛИ-НЕ

-:И-НЕ

I: {{248}}; К=В

S: Приведенная таблица истинности, соответствует элементу, выполняющему операцию

| x | y |

+: инверсии (НЕ)

-: умножения (И)

-: сложения (ИЛИ)

-: стрелку Пирса (ИЛИ-НЕ)

I: {{249}}; К=С

S: Приведенная таблица истинности, соответствует элементу, выполняющему операцию

| x1 | x2 | y |

-: инверсии (НЕ)

+: умножения (И)

-: сложения (ИЛИ)

-: стрелку Пирса (ИЛИ-НЕ)

I: {{250}}; К=С

S: Приведенная таблица истинности, соответствует элементу, выполняющему операцию

| x1 | x2 | y |

-: инверсии (НЕ)

|

|

-: умножения (И)

+: сложения (ИЛИ)

-: стрелку Пирса (ИЛИ-НЕ)

I: {{251}}; К=А

S: Шифратор – это

-: устройство для преобразования двоичного входного кода в позиционный выходной код

+: устройство для преобразования позиционного входного кода в двоичный выходной код

-: устройство, предназначенное для управляемой передачи данных от нескольких источников информации в один выходной канал

-: устройство, предназначенное для управляемой передачи данных от одного источника информации в несколько выходных каналов

I: {{252}}; К=А

S: Дешифратор – это

+: устройство для преобразования двоичного входного кода в позиционный выходной код

-: устройство для преобразования позиционного входного кода в двоичный выходной код

-: устройство, предназначенное для управляемой передачи данных от нескольких источников информации в один выходной канал

-: устройство, предназначенное для управляемой передачи данных от одного источника информации в несколько выходных каналов

I: {{253}}; К=В

S: Мультиплексор – это

-: устройство для преобразования двоичного входного кода в позиционный выходной код

-: устройство для преобразования позиционного входного кода в двоичный выходной код

+: устройство, предназначенное для управляемой передачи данных от нескольких источников информации в один выходной канал

-: устройство, предназначенное для управляемой передачи данных от одного источника информации в несколько выходных каналов

I: {{254}}; К=В

S: Демультиплексор – это

-: устройство для преобразования двоичного входного кода в позиционный выходной код

|

|

-: устройство для преобразования позиционного входного кода в двоичный выходной код

-: устройство, предназначенное для управляемой передачи данных от нескольких источников информации в один выходной канал

+: устройство, предназначенное для управляемой передачи данных от одного источника информации в несколько выходных каналов

I: {{255}}; К=В

S: Максимальное число входов шифратора с 4-разрядным выходом равно:

-: 3

-: 4

-: 8

+: 16

I: {{256}}; К=В

S: Максимальное число выходов шифратора с 8-разрядным входом равно:

+: 3

-: 4

-: 8

-: 16

I: {{257}}; К=В

S: Число адресных входов мультиплексора c 8 информационными входами равно:

-: 1

-: 2

+: 3

-: 4

I: {{258}}; К=В

S: Число выходов мультиплексора c 4 информационными входами равно:

+: 1

: 2

-: 3

-: 4

-: 4

I: {{259}}; К=С

S: На рисунке изображена схема

+:многоразрядного мультиплексора

-: многоразрядного демультиплексора

-: многоразрядного шифратора

-: многоразрядного дешифратора

I: {{260}}; К=С

|

S:На рисунке изображена схема

-: двухразрядного демультиплексора

-: двухразрядного шифратора

+:двухразрядного дешифратора

I: {{261}}; К=А

S:Триггером называется устройство обладающее

+: памятью

-: большим входным сопротивлением

-: малым входным сопротивлением

-: малой потребляемой мощностью

I: {{262}}; К=А

S: Сколько информационных входов имеет RS- триггер

-: 1

+:2

-: 3

-: 4

I: {{263}}; К=В

S:На рисунке изображена схема

S:На рисунке изображена схема

-: Т-триггера

+:RS-триггера

-: D-триггера

-: JK-триггера

I: {{264}}; К=В

S: На рисунке приведены временные диаграммы сигналов на входах R и S асинхронного RS-триггера. Определить состояние выхода Q в моменты времени, соответствующие точкам B и E. Исходное состояние выхода Q=0.

|

|

|

I: {{265}}; К=В

S: На рисунке приведены временные диаграммы сигналов на входах R и S асинхронного RS-триггера. Определить состояние выхода Q в моменты времени, соответствующие точкам A и D. Исходное состояние выхода Q=0.

|

I: {{266}}; К=В

S:На рисунке изображена схема и условное обозначение

S:На рисунке изображена схема и условное обозначение

I: {{267}}; К=В

S:На рисунке изображена схема и условное обозначение

|

+:Т-триггера

-: RS-триггера

-: D-триггера

-: JK-триггера

I: {{268}}; К=В

S:На рисунке изображена схема и условное обозначение

| |||

| |||

-: Т-триггера

-: RS-триггера

-: D-триггера

+: JK-триггера

I: {{269}}; К=С

S: На рисунке изображена таблица истинности

|

-: Т-триггера

-: RS-триггера

+: D-триггера

-: JK-триггера

I: {{270}}; К=С

S: На рисунке изображена таблица истинности

|

-: RS-триггера

-: D-триггера

+: JK-триггера

I: {{271}}; К=А

S: Регистром называется цифровое устройство, служащее для

-: приема информации

-: хранения информации

-: преобразования и выдачи информации

+: для всех перечисленных целей

I: {{272}}; К=А

S:Приведенная на рисунке схема иллюстрирует общий принцип построения

+: регистра

-: триггера

-: дешифратора

-: мультиплексора

I: {{273}}; К=В

S:На рисунке представлено условное обозначение

S:На рисунке представлено условное обозначение

+: параллельного

регистра

-: последовательного

регистра

-: двоичного счетчика

-: двоично-десятичного

счетчика

I: {{274}}; К=В

S:Сдвигающие регистры строятся на основе

-: Т-триггеров

+: D-триггеров

-: RS-триггеров

-: JK-триггеров

I: {{275}}; К=В

S:На рисунке представлена схема

-: параллельного регистра

+: последовательного сдвигающего регистра

-: реверсивного регистра

-: двоично-десятичного счетчика

I: {{276}}; К=В

S:На рисунке представлена схема

|

-: последовательного регистра

-: параллельного регистра

+: делителя частоты

-: двоичного счетчика

I: {{277}}; К=В

S:Счетчик строится на основе

+:Т-триггеров

-: D-триггеров

-: RS-триггеров

-: JK-триггеров

-: JK-триггеров

I: {{278}}; К=В

S:На рисунке представлена схема

иллюстрирующая принцип работы

+: суммирующего счетчика

-: вычитающего счетчика

-: реверсивного счетчика

-: двоично-десятичного счетчика

I: {{279}}; К=С

I: {{279}}; К=С

S: На рисунке представлена схема

иллюстрирующая принцип работы

-: суммирующего счетчика

+: вычитающего счетчика

-: реверсивного счетчика

-: двоично-десятичного счетчика

I: {{280}}; К=С

S: На рисунке представлена схема иллюстрирующая принцип работы

|

-: суммирующего счетчика

-: вычитающего счетчика

+: реверсивного счетчика

-: двоично-десятичного счетчика

I: {{211}}; К=А

S: Операционным усилителем называется

+: унифицированный многокаскадный усилитель постоянного тока

-: унифицированный многокаскадный усилитель переменного тока

-: унифицированный универсальный многокаскадный усилитель

-: любой многокаскадный усилитель

I: {{212}}; К=А

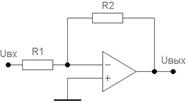

S: На рисунке изображена схема:

S: На рисунке изображена схема:

+: инвертирующего усилителя

-: неинвертирующего усилителя

-: суммирующего усилителя

-: вычитающего усилителя

I: {{213}}; К=В

S: На рисунке изображена схема:

|

-: инвертирующего усилителя

+: неинвертирующего усилителя

-: суммирующего усилителя

-: вычитающего усилителя

I: {{214}}; К=В

S: На рисунке изображена схема:

S: На рисунке изображена схема:

-: инвертирующего усилителя

-: неинвертирующего усилителя

+: суммирующего усилителя

-: вычитающего усилителя

I: {{215}}; К=В

S: На вход схемы подается напряжение U вх=5 В. Выходное напряжение U вых данной схемы равно:

S: На вход схемы подается напряжение U вх=5 В. Выходное напряжение U вых данной схемы равно:

+: 5 В

-: -5 В

-: 0 В

-: 1 В

I: {{216}}; К=В

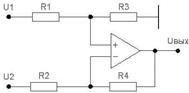

S: На рисунке изображена схема:

-: инвертирующего усилителя

-: инвертирующего усилителя

-: неинвертирующего усилителя

-: суммирующего усилителя

+: вычитающего усилителя

I: {{217}}; К=В

S: На рисунке изображена схема:

S: На рисунке изображена схема:

-: суммирующего усилителя

-: вычитающего усилителя

-: интегрирующего усилителя

+: дифференцирующего усилителя

I: {{218}}; К=В

I: {{218}}; К=В

S: На рисунке изображена схема:

-: суммирующего усилителя

-: вычитающего усилителя

+: интегрирующего усилителя

-: дифференцирующего усилителя

I: {{219}}; К=С

S: Коэффициент усиления по напряжению для данной схемы может быть найден по формуле:

S: Коэффициент усиления по напряжению для данной схемы может быть найден по формуле:

+: KU = - R 2/ R 1

-: KU = - R 1/ R 2

-: KU =1+ R 2/ R 1

-: KU =1+ R 1/ R 2

I: {{220}}; К=С

S: При выполнении условия R 1= R 2= R 3= R выходное напряжение данной схемы может быть найдено по формуле:

-: U вых= U 1+ U 2

-: U вых= U 1+ U 2

+: U вых= -(U 1+ U 2)

-: U вых= U 1- U 2

-: U вых= U 2- U 1