Проверка четности – метод обнаружения ошибок памяти, без возможности восстановления. Каждый байт данных связан с одним битом четности (паритетным битом P). Этот бит устанавливается во время записи, и затем рассчитывается и сравнивается во время чтения. Изменение состояния этого бита говорит о возникшей ошибке. В случае изменения состояния двух битов, вычисление паритетного бита совпадет с записанным, тогда система не определит ошибку, и произойдет экстренная остановка системы.

Большинство всех нерегулярных ошибок происходит именно с одиночным разрядом и проверки четности бывает достаточно.

6.Триггеры: классификация, таблицы переходов.

Класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов.Он мб сброшен (0), установлен (1), переключаться (не определен).

- По способу управления

| синхронные (тактируемые) | асинхронные |

- Синхронные триггеры по воздействию на вход делятся на триггеры со статическим (действие на 1-це либо 0, если есть кружок) и динамическим (косая черта на входе при перекдючении 1/0 сверху вних и наоборот) управлением, а также триггеры типа «мастер-помощник».

• По функциональному признаку – RS-триггеры (reset-set), D- триггеры (delay - задержка), Т- триггеры (из 2-ух RS), JK-триггеры (jump - kill) универсальный.

RS-триггер JK-триггер

RS-триггер JK-триггер

7. Синтез автоматов с памятью

Все автоматы с памятью делятся на синхронные и асинхронные. В асинхронных переключение триггеров производится под воздействием информационных сигналов, скорость переключения определяется задержками в цепях распространения сигналов. В синхронных автоматах имеется глобальный сигнал синхронизации, под воздействием которого все элементы памяти переключаются одновременно, при этом все переходные процессы завершаются в паузах между синхроимпульсами.

В настоящее время считается, что основным способом построения автоматов с памятью следует считать применение синхронных устройств.

Синтез автоматов с памятью:

• Техническое задание (ТЗ) • Формализация задания (в виде графа)• Оптимизация графа и коррекция ТЗ• построение таблицы переходов• Выбор структуры автомата• Синтез функций возбуждения

Формализация задания проектирования осуществляется путем перехода к таблицам, логическим функциям и диаграммам состояния.

Оптимизация и кодирование состояний осуществляются различными способами, в частности, путем объединения состояний с одинаковыми состояниями триггеров. При автоматизированном проектировании возможна автоматизация данного процесса.

Автоматы могут быть построены на базе любых триггеров, однако наибольшее распространение получили JK-триггеры (универсальные), или D-триггеры (что сокращает число требуемых функций возбуждения). Число триггеров (n) в устройстве может быть определено по формуле: n=log2N

где N - число состояний.

Gри высоких требованиях к быстродействию автомата целесообразно воспользоваться способом кодирования «1 из N» (One Hot Encoding), при кото-

ром число триггеров равно числу состояний в таблице переходов n=N.

8. Стандартные последовательностные ЦУ (автоматы с памятью)

На базе триггеров можно построить любые автоматы. Часто используют следующие.

Цифровые счетчики.

- Количество переключающих сигналов, которое надо подать на вход счетчика для того чтобы счетчик вернулся в исходное состояние, равное числу состояний счетчика, называется коэффициентом пересчета или модулем счетчика – Ксч.

- Счетчик называется двоичным, если Ксч = 2m, где т -целое число, m>0, и десятичным, если Ксч = 10p, где р целое число, р > 0

- асинхронные и синхронные

- суммирующие, вычитающие, реверсивные

Асинхронный. fa0=fтакт/2. На выходе из каждого триггера f/4, f/8… Это суммирующий счетчик. Каждый триггер меняет своё время задержки, в итоге на выходе n·tзад, n-число триггеров. Если tзад>Твкл, то счетчик не работает.

Синхронный с параллельным переносом

быстродействие выше, вычисления переключаются синхронно. Но более простой вариант для реализации: синхронный счетчик с комбинированным переносом. tзадержки=ΣtЛЭ. Быстродействие меньше.

Кольцевой счетчик: в простейшем случае по кольцу циркулирует одна кодовая единица, так что коэффициент пересчета счетчика равен числу входящих в него триггеров.

Счетчик Джонса - кольцевой счетчик, который тоже строится на основе замкнутого регистра сдвига, но с одной перекрестной (инверсной) связью.

Реверсивные счетчики могут работать как в режиме сложения, так и в режиме вычитания. Как следует из рис. 164, 165, для изменения режима работы необходимо подключать или прямой, или инверсный выход предыдущего триггера, входящего в счетчик, к Т входу последующего.

Счетчики на схеме обозначают буквами СТ.

Регистры.

Параллельные регистры - это устройства, предназначенные для записи, хранения и выдачи информации, представленной в виде двоичных кодов

Сдвигающий, или сдвиговый регистр (shift register) это регистр, содержимое которого при подаче управляющего сигнала СДВИГ может сдвигаться в сторону старших или младших разрядов, он похож на кольцевой счетчик.

На схеме регистры обозначают буквами RG.

9. ОЗУ

Микросхемы ОЗУ по типу элементов памяти (ЭП) разделяют на статические (SRAM) и динамические (DRAM). В микросхемах статических ОЗУ в качестве элементов памяти применены статические триггеры на биполярных или МДП - транзисторах. Для сохранения записанной информации достаточно поддерживать напряжение питания.

В микросхемах динамических ОЗУ элементы памяти выполнены на основе электрических конденсаторов, сформированных внутри полупроводникового кристалла. Такие ЭП не могут долгое время сохранять свое состояние и поэтому нуждаются в периодическом восстановлении (регенерации). Микросхемы динамических ОЗУ отличаются от микросхем статических ОЗУ большей информационной емкостью, что обусловлено меньшим числом компонентов в одном ЭП и. более плотным их размещением в полупроводниковом кристалле. Динамические ОЗУ сложнее в применении. DRAM менее чувствительны к действию внешних помех типа космических лучей.

Принято различать синхронную и асинхронную память, операции чтения-записи в синхронных SRAM происходят одновременно с тактовыми сигналами контроллера памяти, тогда как в асинхронной памяти данные появляются на выходе через определенные промежутки времени без привязки к синхросигналам.

В асинхронных ЗУ обычно сигналы задаются уровнем, в синхронных - часть сигналов задается фронтом.

Существуют четыре фундаментальных способа чтения данных из SRAM:

• последовательный (Flow thru);

• конвейерный (Pipeline);

• регистровый (Register to Latch);

• пакетный (Burst).

За исключением последнего режима, главное различие между этими типами SRAM заключается в моменте появления данных на выходе по отношению к синхронизирующему импульсу. Пакетный же режим может использоваться совместно с последовательным и конвейерным.

Динамические ОЗУ.

В ОЗУ динамического типа функции элемента памяти выполняет конденсатор, образованный внутри МДП - структуры. Наличие заряда соответствует логическому 0, а отсутствие – логической 1. Так как время хранения заряда на конденсаторе ограничено, то динамические ОЗУ предусматривают периодическую регенерацию информации. При каждом обращении к матрице накопителю происходит автоматическая регенерация информации в выбранной строке.

10. Энергонезависимые ЗУ

Постоянные запоминающие устройства предназначены для хранения информации, которая остается неизменной в течение всего времени работы устройства (до откл. питания). Поэтому в ПЗУ возможен только режим считывания информации, причем это не сопровождается ее разрушением.

Энергонезависимая память – ЗУ, записи в которых не стираются при отключении электропитания.

Массочные ПЗУ.

Информация записывается непосредственно в процессе изготовления. Технологический процесс их изготовления: проецирование рисунка через фотошаблон - маску. От сюда и название.

Прожигаемые ПЗУ.

Класс устройств однократно программируемые их же потребителем ПЗУ. По своей структурной схеме это устройство с одномерной адресацией, в котором для выделения выходного информационного слова нужной длины используется выходной селектор.

Репрограммируемые ПЗУ.

По сути, являются электростатическими ЗУ. Логика построения их ЭЗЭ (электр. запом. устр-ва) подобна логике ЭЗЭ динамического ОЗУ. Отличие в том, что непосредственным носителем информации в них является не конденсатор, а специализированный МДП-транзистор.

РПЗУ:

1) Устройства, использующие в качестве элемента памяти так называемый транзистор с «плавающим» затвором.

2) Устройства, использующие в качестве элемента памяти МДП-транзистор с двухслойным диэлектриком-МНОП-транзистор.

FRAM (Ferroelectric RAM) - ферроэлектрическая память, альтернатива флэш-памяти. Главная особенность FRAM - она сохраняет информацию при выключении питания. Однако это не перепрограммируемое ПЗУ, так как у нее отсутствует явно выраженный цикл стирания информации.

Флеш-память – разновидность п/п технологии электрически перепрограммируемой памяти.

+ Высокая скорость доступа к данным.Экономное энергопотребление. Устойчивость к вибрациям. Удобство подключения к компьютеру. Компактные размеры.

-Ограниченное количество циклов записи.

Информационная емкость – это максимально возможный объем хранимой информации. Выражается в битах или словах (в частности, в байтах). В зависимости от архитектуры доступ к ячейкам осуществляется побитно или пословно. 1M×16 1K×8 65536×1.

11. АЦП

АЦП – устройство, преобразующее входную аналоговую величину в соответствующий ей цифровой эквивалент – код, являющийся выходным сигналом преобразователя. АЦП обеспечивает как дискретизацию непрерывного сигнала по времени, так и его квантование по уровню.

Выходной код АЦП определяется по формуле:

N=Uвх/Uоп·2n

Структура дискретной системы

Аналоговый сигнал задан в вольтах. Устройство выборки и хранения выполняется дискретизацию.

Теорема Котельникова (критерий Найквиста):

Частота дискретизации fs сигнала с шириной полосы fs должна удовлетворять условию fs>2 fa, в противном случае информация о сигнале будет потеряна. Эффект наложения спектров возникает, когда fs<2 fa. Эффект наложения спектров широко используются в таких задачах, как прямое преобразование промежуточной частоты в цифровую форму.

Uout=Uцифр

Uout=Uцифр

Uref=Uопорное

Uопорное для преобраз. изменят. от 0 до U0оп или от - U0оп до + U0оп

может существовать различие до ½

LSB между реальным входным аналоговым сигналом и точным значением выходного цифрового сигнала. Этот эффект известен как ошибка (погрешность) или неопределенность квантования Δk. Это методическая погрешность, вызванная конечным значением шага квантования h (единица младшего разряда ЕМР), она находится в пределах Δk = ± 0,5 h. Мощность шума квантования определяется средне-квадратичным отклонение СКО=Δ/√12, где Δ – шаг квантования. Отношение сигнал/шум: SNR(дБ)=6,02N+1,76, при ширине полосы fs/2, n-число разрядов.

LSB между реальным входным аналоговым сигналом и точным значением выходного цифрового сигнала. Этот эффект известен как ошибка (погрешность) или неопределенность квантования Δk. Это методическая погрешность, вызванная конечным значением шага квантования h (единица младшего разряда ЕМР), она находится в пределах Δk = ± 0,5 h. Мощность шума квантования определяется средне-квадратичным отклонение СКО=Δ/√12, где Δ – шаг квантования. Отношение сигнал/шум: SNR(дБ)=6,02N+1,76, при ширине полосы fs/2, n-число разрядов.

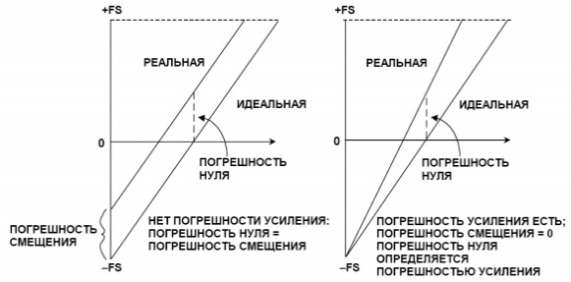

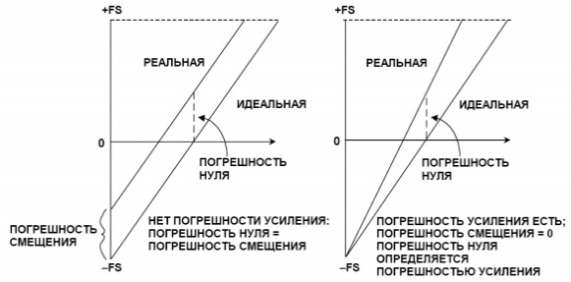

Погрешность смещения нуля преобразователя (1) и погрешность усиления или мультипликативная погрешность (2).

Обычно погрешность исправляют ВЧ фильтром, лучше всего подходит фильтр Бесселя.

Разновидности АЦП.

Самый простой и популярный – АЦП последовательного приближения.

Самый простой и популярный – АЦП последовательного приближения.

Задается начальная шкала и с каждым циклом она делится пополам, т.о. подбирается наиболее подходящее приближение.

Параллельный АЦП

Параллельный АЦП

квантование сигнала выполняется с помощью набора компараторов К, включенных параллельно источнику сигнала. Пороговые уровни компараторов устанавливают с помощью резистивных делителей. Таким образом, в регистр записывается число, определяемое количеством сработавших компараторов, а на выходе появляетсясоответствующий двоичный код.

8-разрядный конвейерный АЦП

8-разрядный конвейерный АЦП

несколько параллельных АЦП работают последовательно, при этом каждый следующий АЦП обрабатывает результат вычитания из сигнала его оценки, сделанной на предыдущем этапе. Для повышения точности результат усиливают в соответствующее число раз. При этом возможна конвейерная обработка сигнала, когда во время обработки сигнала ошибки вторым АЦП, первый обрабатывает следующую выборку.

Сигма-дельта АЦП. Сигма означает наличие в схеме интегратора, дельта — диф-ференциаль-ного усилителя. В основе работы лежат два принципа: усреднение результатов измерения и автоматический перенос спектра шума квантования в более высокочастотную область при высокочастотной дискретизации низкочастотного сигнала.

12.ЦАП

Выходной код ЦАП определяется по формуле:

Uвых=Uоп·Uоп/2n

Время установления ЦАП

Погрешности

Интегральная нелинейность ЦАП аналогична нелинейности усилителя и определяется как максимальное отклонение фактической характе-ристики передачи преобразователя от прямой линии.

Другой тип нелинейности преобразователей – дифференциальная нелинейность (DNL). Она связана с нелинейностью кодовых переходов преобразователя. В идеальном случае изменение на единицу младшего разряда цифрового кода точно соответствует изменению аналогового сигнала на величину единицы младшего разряда. Если дифференциальная нелинейность ЦАП меньше, чем –1 LSB на любом переходе, ЦАП называют немонотонным, и его характеристика передачи содержит один или несколько локальных максимумов или минимумов. Дифференциальная нелинейность, большая чем +1 LSB, не вызывает нарушения монотонности, но также нежелательна.

По принципу действия схемы ЦАП бывают:

строковые,

с суммированием и делением напряжения,

с суммированием токов.

Широтно-импульсный модулятор

ЦАП передискретизации

ЦАП взвешивающего типа

ЦАП лестничного типа

13. Гарвардская и фон-неймановская архитектура вычислительных систем. Типовые узлы микропроцессоров/микроконтроллеров.

Гарвардская архитектура — архитектура ЭВМ, отличи-тельными признаками которой являются:

Гарвардская архитектура — архитектура ЭВМ, отличи-тельными признаками которой являются:

1. Хранилище инструкций и хранилище данных представляют собой разные физические устройства.

2. Канал инструкций и канал данных также физически разделены.

Обеспечивает более высокую скорость выполнения программы по сравнению с фон-неймановской за счет возможности реализации параллельных операций. Выборка следующей команды может происходить одновременно с выполнением предыдущей.

Особенностью фон-неймановской архитектуры - использование общей памяти для хранения программ и данных. Основное преимущество архитектуры Фон-Неймана – упрощение устройства МПС, так как реализуется обращение только к одной общей памяти. Размещение стека в общей памяти облегчало доступ к его содержимому.

Типовые узлы МП

Индексный регистр содержит адрес операнда (указывает на операнд, находящийся в памяти при косвенной адресации). Счетчик команд (Program Counter) содержит адрес следующей команды, указывается на следующую команду. Стек – это область памяти, доступ к которой осуществляется последовательно по принципу Last In – First Out. Указатель стека содержит адрес текущей вершины стека. Шина данных служит для обмена информацией между устройствами компьютера, например, между оперативной памятью и контроллерами устройств. Адресная шина используется процессором при чтении данных из оперативной памяти. По ней процессор сообщает оперативной памяти адрес ячейки, из которой нужно считать данные. Информация по адресной шине передается только в одном направлении – от процессора к памяти. Шина управления передает ряд служебных сигналов: запись/чтение, готовность к приему/передачи данных, подтверждение приема данных, аппаратного прерывания, управление и инициализации контролеров и др.

14. Организация прерываний, ПДП.

Взаимодействие CPU с внешними устройствами происходит через прерывания.

Векторная система прерываний. Каждое прерывание имеет свой обработчик прерываний (вектор). Каждый вектор имеет уровень приоритета. При возникновении запроса прерывания процессор передает управление соответствующему вектору (незамаскированному или имеющ. высший приоритет). Система прерываний с опросом. В системе есть только один вектор прерывания. Обработчик прерывания выясняет источник прерывания методом опроса флагов запросов прерываний. Схема приоритетов отсутствует. Схема приоритетов. Запрос с более высоким уровнем приоритета может прерывать обработку прерывания с более низким приоритетом. Запрос с равным или более низким приоритетом ожидает своей очереди. При одновременном поступлении первым обрабатывается запрос с более высоким уровнем приоритета. Маскируемые прерывания можно запрещать установкой соответствующих битов в регистре маскирования прерываний. Немаскируемые прерывания не могут быть запрещены программно или имеют свой индивидуальный бит маскировки.

Типы прерываний

Аппаратные – формируются периферийными устройствами и происходят в произвольные моменты асинхронно с основной программой. Программные – происходят синхронно с выполнением программы вследствие выполнения каких-либо инструкций. Программные прерывания (исключения).

Исключения ошибки – вызвавшая их команда не может быть выполнена. Исключения обслуживания – выполнение вызвавшей их команды откладывается до завершения обработчика. Исключения отладки (ловушки) – используются для отладки программы

Обработка прерываний: завершается текущая команда, сохраняется текущее значение счетчика команд (например, в стеке), управление передается обработчику прерывания с наивысшим приоритетом, выполняется обработка, по команде возврата из обработчика в счетчик команд загружается ранее сохраненное значение (адрес возврата).

Прямой доступ к памяти (ПДП) предполагает отказ процессора от монопольного управления шиной адреса и временную передачу этого управления периферийному устройству по его запросу.

Ожидание предполагает приостановку выполнения команды процессором до выполнения каких-либо условий. Это снижает производительность устройства (необходимо минимизировать) и должно предусматривать прекращение по истечении тайм-аута.

15. Интерфейсы МП систем.

Под интерфейсом следует понимать унифицированное программно-аппаратное устройство, предназначенное для организации обмена информацией между микропроцессором и внешними устройствами, объединенными в единую систему.

Пример параллельного: параллельный порт подключения принтера. Последовательного: интерфейсы локальных и глобальных сетей. Последовательный интерфейс для передачи данных использует одну сигнальную линию, по которой информационные биты передаются друг за другом последовательно.

В асинхронном режиме каждый байт данных сопровождается специальными сигналами "старт" и "стоп". Назначение этих сигналов состоит в том, чтобы, во-первых, известить приемник о приходе данных и, во-вторых, чтобы дать приемнику достаточно времени для выполнения некоторых функций, связанных с синхронизацией, до поступления следующего байта. Сигнал "старт" имеет продолжительность в один тактовый интервал, а сигнал "стоп" может длиться один, полтора или два такта. Асинхронным описанный режим называется потому, что каждый принятый байт может быть смещен во времени относительно переданного байта на случайный промежуток времени. Это резко снижает требования к характеристикам системы передачи. В то же время, такая асинхронность передачи не влияет на корректность принимаемых данных, так как в начале каждого байта происходит дополнительная синхронизация приемника с источником за счет битов "старт". Такой режим удобен при невысоком качестве канала связи (например, высокий уровень помех), при передаче информации от устройств, которые генерируют байты данных в случайные моменты времени.

При синхронном режиме передачи пользовательские данные собираются в кадр, который предваряется байтами синхронизации (на рис.3 - флаги). Старт-стопные биты между соседними байтами отсутствуют. Байт синхронизации - это байт, содержащий заранее известный код, например 0111110, который оповещает приемник о приходе кадра данных. Его обычно называют флагом. При его получении приемник должен войти в байтовый синхронизм с передатчиком, то есть правильно понимать начало очередного байта кадра.

16. МК PIC18, архитектура, особенности

PIC — серия микроконтроллеров, имеющих гарвардскую архитектуру. Под маркой PIC фирмой Microchip выпускаются 8-, 16- и 32-битовые микроконтроллеры и цифровые сигнальные контроллеры. 8-битовые микроконтроллеры имеют модифицированную гарвардскую архитектуру и делятся на два больших семейства: PIC10/12/16 и PIC18. Семейства микроконтроллеров PIC18 имеют следующие свойства:

• Эффективное кодирование на C

• Продвинутая архитектура (16-и разрядные слова программ)

• Низкая цена

• Гибкость самопрограммирования

• Поддержка широкораспространенных протоколов связи (в т.ч. SPI, I2C)/

PIC18Fxxxx - микоконтроллеры общего назначения

Микроконтроллеры общего назначения выпускаются в корпусах от 18 до 80-и выводов, с объемом Flash памяти программ до 128КБ. Все контроллеры имеют встроенный АЦП, последовательные интерфейсы, часть контроллеров выпускается по NanoWatt технологии и имеют встроенный программируемый генератор/

Особенности:

Работа сторожевого таймера в семействах PIС18 и PIC24F может быть разрешена в слове конфигурации прибора. Выход из энергосберегающих режимов SLEEP и IDLE может осуществляться при переполнении сторожевого таймера. Сторожевой таймер сбрасывается при выполнении микроконтроллером следующих инструкций: CLRWDT, переход в энергосберегающий режим, изменение частоты внутреннего RC генератора.

17. Организация памяти PIC18

Память программ.

PIC-контроллеры обладают гарвардской архитектурой. Встроенная память программ, выполненная по FLASH - технологии, имеет объем до 32К (128K). Память программ PIC18 организована в виде 16-битных слов, однако может адресоваться побайтно. Это означает, что старшее и младшее слово инструкции могут быть доступны при использовании косвенной адресации. Память программ выровнена по младшему байту слова, при линейном выполнении кода программный счетчик всегда увеличивается на 2.

Максимальный объем адресуемой памяти в PIC18 определяется разрядностью программного счетчика (PC - Program Counter). Семейство PIC18 использует 21-битный PC. Конфигурационное пространство (Configuration Space) в верхней половине адресуемой памяти программ физически не реализуется, кроме нескольких областей, предназначенных для конфигурации микроконтроллера и идентификационного слова Device ID. В семействе PIC18 три слова программы в верхней (с меньшим адресом) части доступной области памяти зарезервированы для аппаратных векторов перехода. Это вектор сброса (0x00), вектор прерывания низкого приоритета (0x08) и вектор прерывания высокого приоритета (0x18). Область конфигурации семейства PIC18 расположена в конфигурационном пространстве (диапазон адресов 0x300000 - 0x30000F). Большинство микроконтроллеров PIC18 имеют независимый блок памяти, объемом от 1 тыс. до 4 тыс. слов который может использоваться для хранения бутлоадера. Этот блок может быть защищен от чтения и табличной записи из другой части программы индивидуальным битом конфигурации. Архитектура PIC18 поддерживает использование внешних устройств памяти в качестве памяти программ. Это обеспечивается наличием в некоторых микроконтроллерах модуля интерфейса с внешней памятью (EMI - External Memory Interface), который на самом деле является частью ядра и имеет прямой доступ к шине адреса программ. В большинство микроконтроллеров семейств PIC18 в качестве памяти программ используется Flash память с возможностью перепрограммирования. Микроконтроллеры PIC18 имеют побайтный доступ к памяти программ с помощью табличных инструкций чтения. Большинство микроконтроллеров PIC18 имеют на кристалле энергонезависимую EEPROM память для хранения констант, программных настроек или записи редко меняющихся данных. Память EEPROM доступна для чтения и записи, доступ к ней осуществляется при помощи тех же регистров, которые используются для работы с Flash памятью программ. Имеют аппаратный стек для сохранения адреса возврата, который не отображен в память данных и имеет глубину 32 уровня.

Память данных

Теоретически память данных линейна и может быть прозрачно доступна некоторым инструкциям. Однако для использования большинства инструкций применяется сегментная модель памяти данных, разделенной на банки. Это связано с ограниченным размером машинного кода инструкции - большинство инструкций имеют 8-битное поле адреса операнда. Таким образом, для этих инструкций память данных делится на 16 банков по 256 байт. Для обращения к определенному банку используется служебный регистр выбора банка BSR, который содержит четыре старших бита адреса операнда. Адрес каждой ячейки – 12 разрядный. Регистры специального назначения (регистры управления ядром, периферией, и т. п.) расположены обычно в самом низу памяти данных, как правило, по адресам с 0xF60 по 0xFFF включительно. Возможно два режима доступа: я использованием регистра BSR и без него. При косвенной адресации BSR игнорируется.

18. Система прерываний PIC18

Система прерываний имеет два вектора: с высоким и низким приоритетом. Обработчик прерывания с высоким приоритетом располагается по адресу 000008h., с низким приоритетом – по адресу 000018h. Можно настроить систему прерываний на работу с одним вектором (адрес 000008h). Можно настраивать приоритет некоторых источников прерываний. При переходе к обработчику в стеке сохраняется PC. В режиме «быстрого возврата», дополнительно сохраняются WREG, STATUS, BSR.

При переходе на подпрограмму обработки прерывания автоматически независимо от состояния регистра IE запрещаются все прерывания, которые имеют уровень приоритета, равный уровню приоритета обслуживаемого прерывания, - то есть вложенные прерывания с равным уровнем приоритета запрещены. Таким образом, низкоприоритетное прерывание (имеющее "0" в соответствующем разряде регистра IP) может прерываться высокоприоритетным (имеющим "1" в соответствующем разряде регистра IP), но не низкоприоритетным. Обслуживание высокоприоритетного прерывания не может быть прервано другим источником.

Пример: программа выполняет основной цикл, совершенно асинхронно приходит разрешенное прерывание от любого модуля. Микроконтроллер выполняет текущую команду до конца, затем автоматически сохраняет текущий указатель команд PC (адрес возврата из прерывания) в стек. Далее исполнение программы начинается с вектора, соответствующего приоритету соответствующего прерывания (исполняется обработчик прерываний). Когда обработчик прерываний завершил свою работу, выход из прерываний осуществляется командой RETFIE. После этой команды, микроконтроллер восстанавливает из стека адрес возврата и переходит на выполнение команды, расположенной по этому адресу (следующая команда основного цикла).

Прерывания с высоким приоритетом, могут вызываться как из основного цикла, так и из обработчика прерываний с низким приоритетом.

Так как обработчик прерываний это та же программа, которая будет модифицировать основные регистры ядра WREG, обработчика эти регистры необходимо сохранить, а после - восстановить. Для этого используется одноуровневый аппаратный быстрый стек.

19. Система команд PIC18. Команды пересылок, виды адресации

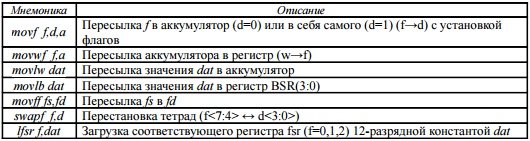

Система команд. Операнд может находиться в памяти или в команде (константа). Результат большинства операций может сохраняться в аккумуляторе (WREG) или в памяти, что определяется битом «d». Тип доступа к памяти (с использованием BSR или без него) определяется битом «а». Различают команды пересылки, арифметические команды, логические команды, битовые команды, команды передачи управления, специальные команды.

Пример команды.

| 15 10 | 7 0 | ||

| OPCODE | d | a | f (FILE #) |

ADDWF (мнемоника операции

) MYREG (адрес операнда), W(запись W означает d=0 (по умолчанию d=1)), B (В – доступ с применение BSR (по умолчанию BSR не используется)

+таблица команд

Команды пересылок

Прямая адресация (адрес операнда содержится в команде)

Архитектура PIC18 позволяет адресовать любой байт из памяти данных. Однако так как для прямой адресации в большинстве инструкций в качестве операнда используется 8-битная константа, память данных PIC18 условно разделена на 16 банков. Текущий банк определяется значением служебного регистра BSR.

Косвенная адресация (адрес операнда содержится в регистре) - обращение к регистрам осуществляется через один и тот же псевдорегистр INDF0/1/2. Для косвенной адресации используется набор регистров специального назначения (указателей) и набор виртуальных регистров. При этом в три указателя FSR0, FSR1 и FSR2 может быть загружена 12-битная константа. Для выполнения косвенной адресации, в качестве операнда используется один из виртуальных регистров. В зависимости от того, какой из виртуальных регистров является операндом, может быть выполнена дополнительная операция над указателем, например инкремент или декремент.

- POSTINC0/1/2 – постинкремент FSR

- POSTDEC0/1/2 – постдекремент FSR

- PREINC0/1/2 – предынкремент FSR

- PLUSW0/1/2 – используется адрес (FSR+WREG) без модификации FSR

Таким образом, только три указателя и соответствующие им виртуальные регистры могут быть использованы для косвенной адресации.

• Регистры FSR состоят из 2-х частей (FSR0=(FSR0H:FSR0L)

• Допускается одновременная загрузка FSR командой LFSR

20. Система команд PIC18. Команды арифметических и логических операций

Система команд. Операнд может находиться в памяти или в команде (константа). Результат большинства операций может сохраняться в аккумуляторе (WREG) или в памяти, что определяется битом «d». Тип доступа к памяти (с использованием BSR или без него) определяется битом «а». Различают команды пересылки, арифметические команды, логические команды, битовые команды, команды передачи управления, специальные команды.

Пример команды.

| 15 10 | 7 0 | ||

| OPCODE | d | a | f (FILE #) |

ADDWF (мнемоника операции

) MYREG (адрес операнда), W(запись W означает d=0 (по умолчанию d=1)), B (В – доступ с применение BSR (по умолчанию BSR не используется)

+таблица команд

21. Таймеры PIC18, режимы, применение

Таймер – это многофункциональный счетчик, работающий в режиме счета внешних импульсов (режим счетчика) или машинных циклов (режим таймера). Таймеры поддерживают специальные режимы (CAPTURE/COMPARE/PWM). В PIC18 имеется 4 таймера (Timer0/1/2/3).

Таймер0 может работать в режиме таймера или счетчика внешних событий (с программным выбором реакции на фронт или спад импульса) и снабжен управляемым предделителем. Переполнение счетчика вызывает прерывание микроконтроллера.

Таймер1 может также работать в режиме таймера/счетчика, кроме того, он работает в составе модулей CAPTURE, COMPARE и имеет возможность синхронизации от отдельного внешнего тактового генератора. Имеется также возможность синхронизации импульсной последовательности внешнего генератора с тактовым генератором микроконтроллера.

Таймер2 может работать в режиме таймера с генерацией прерывания в момент совпадения содержимого счетчика с содержимым регистра PR2, а также служит для тактирования модулей PWM микроконтроллера. Кроме этого модуль синхронного приемопередатчика может использовать таймер 2 в качестве задающего генератора.

Таймер3 имеет схему, аналогичную таймеру 1 и использует те же внешние выводы при работе в режиме счетчика.

Режим CAPTURE

В контроллере имеется два модуля CAPTURE, базой для которых являются таймер 1 итаймер 3. Биты в регистре T3CON указывают, какой из таймеров является базой для модулей CATURE. Возможно три варианта выбора: таймер1 для обоих модулей, таймер3 для обоих модулей, таймер1 для CCP1 и таймер3 для CCP2. Принцип действия модулей. Когда на выводе микроконтроллера появляется фронт/спад импульса, содержимое выбранного таймера счетчика записывается в регистры CCPRXH:CCPRXL и устанавливается флаг прерывания CCPXIF. Модули CAPTURE удобно применять для измерения временных интервалов (период или длительность импульсов).

Режим COMPARE

В режиме COMPARE используются те же самые модули, однако, принцип другой. Значение сравнения заранее записывается в регистры CCPRXH:CCPXL и постоянно сравнивается с текущим значением выбранного таймера. Когда обнаруживается совпадение, на выводах микроконтроллера формируется событие (сброс, установка или переключение), генерируется запрос прерывания и устанавливается триггер специального события. Этот триггер может быть использован для запуска АЦП.

Режим генерации ШИМ

Режим генерации ШИМ сигнала используется для формирования последовательности прямоугольных импульсов с управляемыми периодом и длительностью. Наиболее часто используется схема с постоянным периодом и переменной длительностью. С помощью НЧ фильтрации из ШИМ сигнала может быть выделен аналоговый сигнал произвольной формы. В некоторых микроконтроллерах имеется несколько таких модулей для управления многофазными двигателями или модуль ШИМ с расширенной функциональностью. Базой для модуля ШИМ является таймер2.

22. Режимы пониженного энергопотребления и синхронизации

Режим ожидания: прекращает работу центральный процессор, но продолжают функционировать периферийные модули, которые контролируют состояние объекта управления. При необходимости сигналы от периферийных модулей переводят МК в активный режим, и рабочая программа формирует необходимые управляющие во