Асинхронный RS-триггер с инверсными входами.

RS-триггер с инверсными входами.

Логическая структура триггера приведена на рис. 4.2,а. Отличие от логической структуры рассмотренного выше RS-триггера с прямыми входами состоит лишь в том, что здесь использованы логические элементы И-НЕ.

рис 4.2

При этом активным логическим уровнем на входах является уровень лог. 0, пассивным - лог. 1. Для того чтобы активными были, как и в предыдущем триггере, входные сигналы S = 1 и R=1, будем считать, что на входы подаются инверсии  и

и  . Тогда при S = 1 (или R = 1)

. Тогда при S = 1 (или R = 1)  = 0 (или

= 0 (или  = 0) и на входе триггера будет действовать активный уровень лог. 0. Другое удобство такого обозначения входных величин состоит в том, что триггер с инверсными входами описывается той же таблицей состояний (рис. 4.1.б), что и триггер с прямыми входами.

= 0) и на входе триггера будет действовать активный уровень лог. 0. Другое удобство такого обозначения входных величин состоит в том, что триггер с инверсными входами описывается той же таблицей состояний (рис. 4.1.б), что и триггер с прямыми входами.

Рассмотрим устойчивые состояния триггера. Пусть на входах действуют пассивные уровни S = 0 и R = 0 ( = l и

= l и  = 1). В состоянии 0 триггера Q = 0, этот уровень передается на вход элемента В и вызывает на его выходе уровень Q = l, уровень 1 с выхода элемента В подается на вход элемента А, и так как на обоих входах элемента А уровень 1, то на выходе этого элемента Q = 0. Аналогично определяется второе устойчивое состояние триггера.

= 1). В состоянии 0 триггера Q = 0, этот уровень передается на вход элемента В и вызывает на его выходе уровень Q = l, уровень 1 с выхода элемента В подается на вход элемента А, и так как на обоих входах элемента А уровень 1, то на выходе этого элемента Q = 0. Аналогично определяется второе устойчивое состояние триггера.

При подаче активного уровня  = 0 (S = 1) на выходе элемента А устанавливается уровень Q = l, на выходе элемента В - уровень

= 0 (S = 1) на выходе элемента А устанавливается уровень Q = l, на выходе элемента В - уровень  = 0 и триггер оказывается установленным в состояние 1. При подаче активного уровня

= 0 и триггер оказывается установленным в состояние 1. При подаче активного уровня  = 0 (R = 1) триггер устанавливается в состояние 0. Как и для триггера с прямыми входами, одновременная подача активных уровней на оба входа не допускается.

= 0 (R = 1) триггер устанавливается в состояние 0. Как и для триггера с прямыми входами, одновременная подача активных уровней на оба входа не допускается.

На рис. 4.2,б показано условное обозначение RS-триггера с инверсными входами.

Структура микроконтроллера AVR AT90S8515. Назначение блоков РОН, АЛУ, регистра состояния.

Микроконтроллер AVR - восьмиразрядный RISC-микроконтроллер с Гарвардской архитектурой и пониженным энергопотреблением. Набор команд, ограниченность которого свойственна RISC-архитектурам, в данном случае необычно широк (120 команд), однако при этом сохранено основное преимущество RISC-архитектур - повышенное быстродействие и сокращенное число операций обмена с памятью программ. Почти все команды размещаются в одной ячейке программной памяти и выполняются за один такт синхросигнала. Типичен режим с частотой синхронизации 1 МГц. Максимальная частота синхросигнала составляет 8 МГц. Доступ к памяти программ и памяти данных осуществляется через собственные шины этих модулей, поэтому можно не только сделать различными разрядности шин, но и реализовать параллелизм операций в процессах выполнения текущей команды и выборки и дешифрации следующей, т.е. ввести в работу МК элементы конвейеризации.

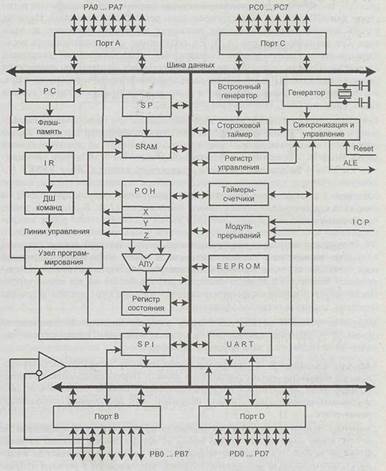

На рис. 2.1 показана схема МК AVR типа AT90S85J5. Микроконтроллер имеет восьмиразрядную шину данных, посредством которой его модули обмениваются информацией.

Рис. 2.1. Структура микроконтроллера AVR

Сердцем микроконтроллеров AVR является 8-битное микропроцессорное ядро или центральное процессорное устройство (ЦПУ), построенное на принципах RISC-архитектуры. Основой этого блока служит арифметико-логическое устройство (АЛУ). По системному тактовому сигналу из памяти программ в соответствии с содержимым счетчика команд (Program Counter - PC) выбирается очередная команда и выполняется АЛУ. Во время выбора команды из памяти программ происходит выполнение предыдущей выбранной команды, что и позволяет достичь быстродействия 1 MIPS на 1 МГц.

АЛУ подключено к регистрам общего назначения РОН (General Purpose Registers - GPR). Регистров общего назначения всего 32, они имеют байтовый формат, то есть каждый из них состоит из восьми бит. РОН находятся в начале адресного пространства оперативной памяти, но физически не являются ее частью. Поэтому к ним можно обращаться двумя способами (как к регистрам и как к памяти). Такое решение является особенностью AVR и повышает эффективность работы и производительность микроконтроллера.

Отличие между регистрами и оперативной памятью состоит в том, что с регистрами можно производить любые операции (арифметические, логические, битовые), а в оперативную память можно лишь записывать данные из регистров.

Регистр состояния (Status Register) – данный регистр содержит информацию о результате исполнения предыдущей ассемблерной интсрукции. При помощи данного результата, можно менять ход исполнения (ветвление) программы, то есть принимать решения в зависимости от результата предыдущей операции. Арифметические, логические и операции с битами приводят к изменению регистра состояния. Все остальные ассемблерные команды не изменяют поля регистра состаяния.

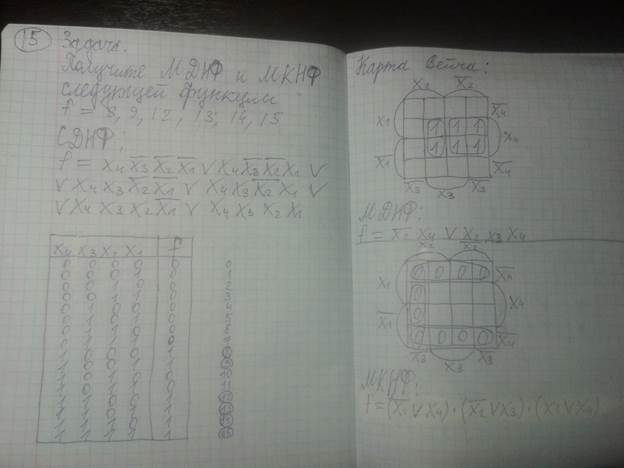

3. Задача