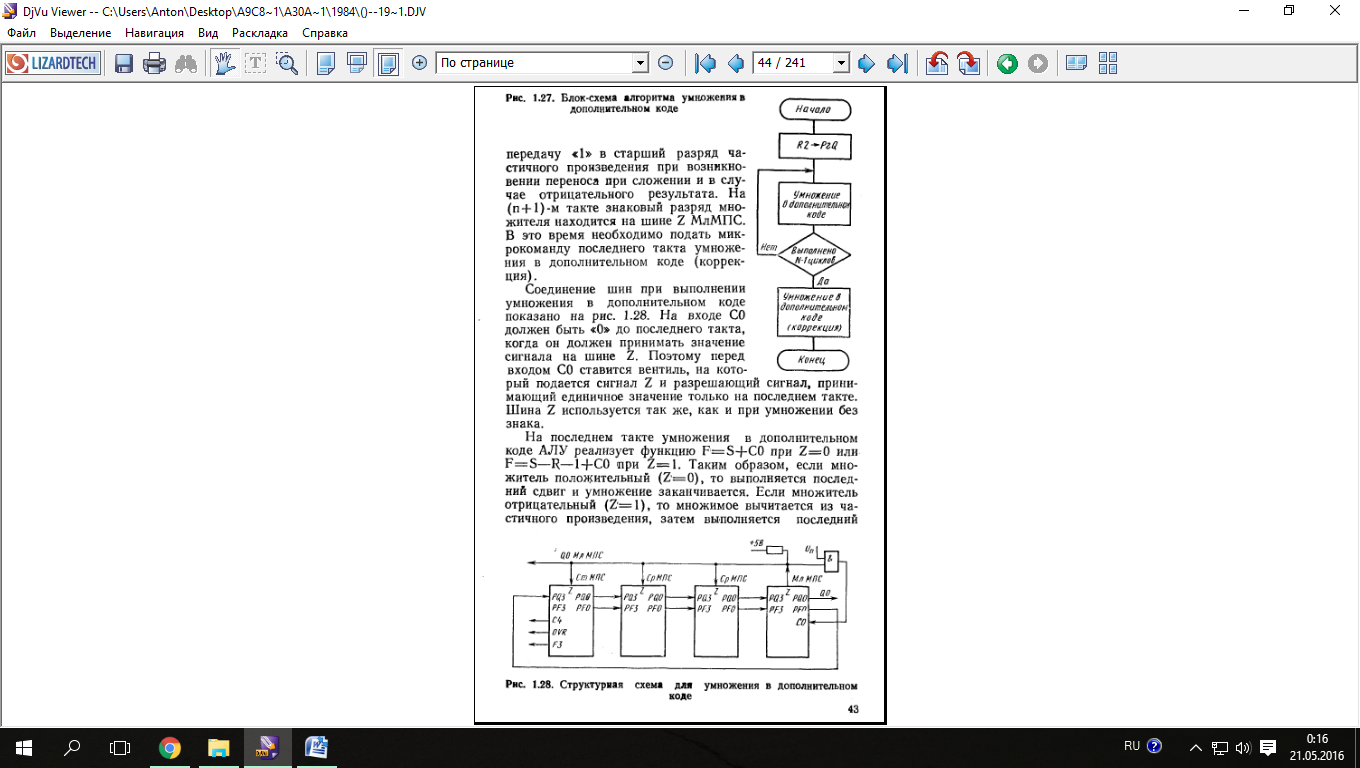

Описание алгоритма блок-схемы.

Алгоритм Умножение дробных двоичных чисел в дополнительном коде со знаком. В случае умножения двух 16-разрядных чисел команда “Умножение в дополнительном коде” должна подаваться в течение 15 микроциклов. Во время выполнения сдвигов вправо в разряд Y3 четвертого ПЭ помещается значение вырабатываемого этим ПЭ сигнала OVR. Через 15 микроциклов знаковый разряд множителя поступит на выход Z первого ПЭ. Теперь на ширину команд нужно подать команду “Последний цикл умножения в дополнительном коде”. В том случае, если знак множителя отрицателен, то переднему фронту следующего тактового импульса будет произведена коррекция частичного произведения путем вычитания дополнительного кода множимого. Если же знак множителя положителен, коррекция частичного произведения осуществляться не будет

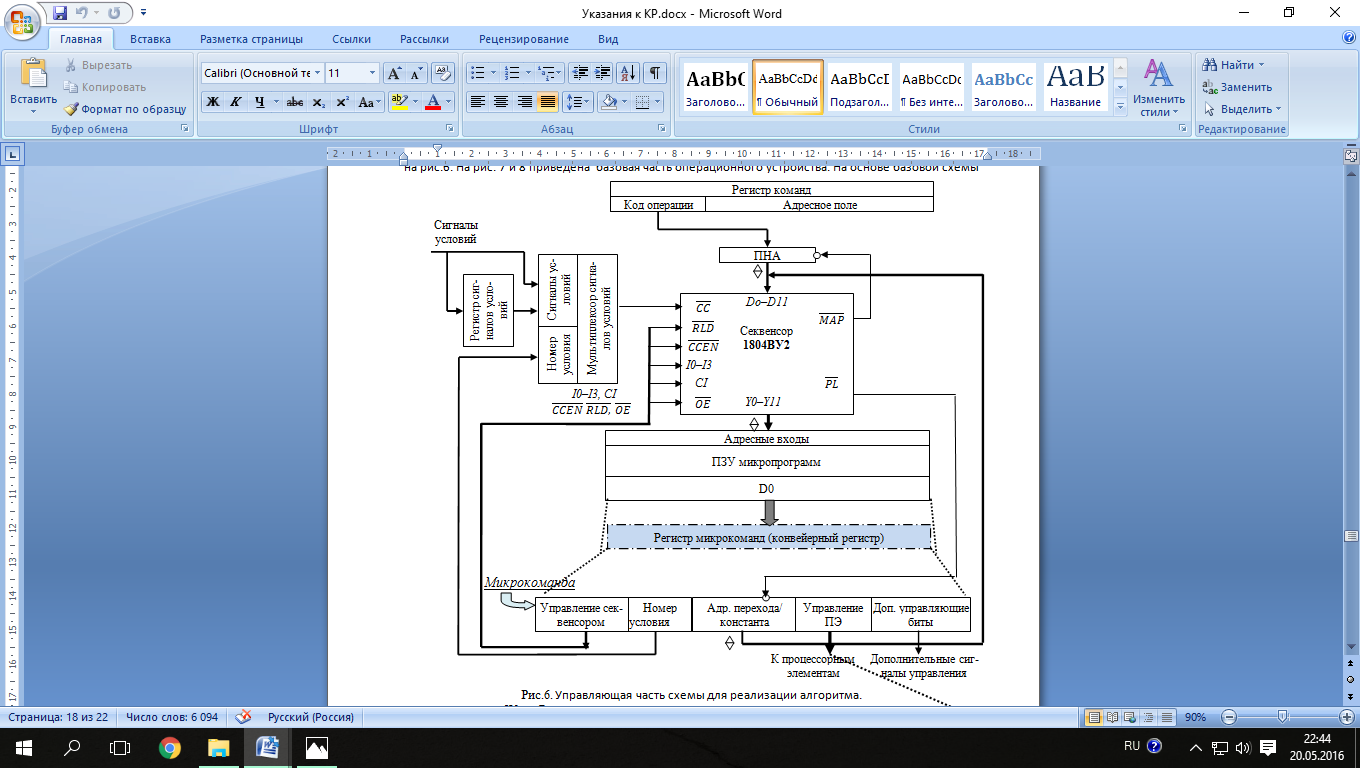

Структурная схема устройства для реализации алгоритма.

Операционные устройство основано на базе 4-х разрядного процессорного элемента ПЭ-ВС2. Так как исходные данные имеют 16-ое значение, то требуемая разрядность операционного устройства обеспечивается объединением 4-х микропроцессорных секций.

| +5V R |

| Схема каскадирования четырех ПЭ К1804ВС2 |

Z

PQ3 PQ0

PR3 PR0

C4 C0

1804ВС2

старшая

/ OVR / OVR

/F3 A0−A3 /F3 A0−A3

B0−B3 B0−B3

I0−I8,

I0−I8,

|

Z

PQ3 PQ0

PR3 PR0

C4 C0

1804ВС2

средняя

A0−A3

B0−B3 B0−B3

I0−I8,

I0−I8,

|

Z

PQ3 PQ0

PR3 PR0

C4 C0

1804ВС2

средняя

A0−A3

B0−B3 B0−B3

I0−I8,

I0−I8,

|

Z

PQ3 PQ0

PR3 PR0

C4 C0

1804ВС2

младшая

A0−A3

B0−B3 B0−B3

I0−I8,

I0−I8,

|

| +5V |

| +5V |

| 5V |

Микропрограмма умножение двоичных чисел в дополнительном коде.

| Адрес | Действие УМП | Секвенсор | Операционный блок | Комментарии | ||||||||

| Команда | Адрес | CCE | Инструкции | Адреса | CO | |||||||

| Код | Мнемон. обзн. | I8I7I6 I5 Ист. | I4I3I2 I1 Опер. | I0 Прием. | A | B | ||||||

| Получение адреса из ПНА | JMAP | - | - | - | - | - | - | - | Переход по адресу 1 | |||

| Загрузка счетчика | PUSH | - | - | - | - | - | Загрузка 13 в сч, помещение сл мк в стек | |||||

| Повторение цикла | RFCT | R0 | R1 | операция умножения в доп коде | ||||||||

| Условный возврат из мп | CRTN | - | R0 | R1 | Операция умножения в доп коде(коррекция) |

|

|

Порядок выполнения микропрограммы.

Микрокоманда 1. На входы I0-I3 подаются сигналы, определяющие инструкцию PUSH, которая используется для организации циклов в микропрограмме. Независимо от выполнения условия в стек загружается адрес, равный Атекущий+1, а при выполнении условия, кроме этого, в регистр–счётчик (далее просто счётчик) загружается число, записанное в поле адрес перехода/счетчик микрокоманды.

Микрокоманда 2. На входы I0-I3 подаются сигналы, определяющие инструкцию RFCT. На входах и схемы секвенсора “1”. Это значит, что будет выполнена микрокоманда 2 “умножение в дополнительном коде”, адрес которой записан в вершину стека, если счетчик не равен нулю. Когда содержимое счетчика равно нулю, выполняется переход к следующей по порядку микрокоманде. Одновременно производится выталкивание из стека.

Микрокоманда 3. На входы I0-I3 подаются сигналы, определяющие инструкцию CRTN, сигналы на входах CCE и RLD не меняются. Входы D не используются. Поскольку CCE=1, то данная инструкция организует безусловный возврат из подпрограммы путём перехода к адресу записанному в стеке. Одновременно происходит выталкивание из стека.

|

|

Список литературы.

1. Проектирование цифровых систем на комплектах микропрограммируемых БИС. С. С. Булгаков, В. М. Мещеряков, В. В. Новоселов, Л. А. Шумилов; Под ред. В. Г. Колесникова.

2. Гребенников В.Ф. Курс лекций по дисциплине “Архитектура средств вычислительной техники”.

3. Гребенников В.Ф. Введение в КР2

4. Проектирование микропроцессорных устройств с разрядно-модульной организацией/ Автор: Мик Дж., Брик Дж.