Саратовский государственный технический университет

Имени Гагарина Ю.А.

ПРОЕКТИРОВАНИЕ и ОПТИМИЗАЦИЯ УСТРОЙСТВА ЦИФРОВОГО УПРАВЛЕНИЯ

Методические указания и задания

для выполнения контрольной работы

по дисциплине

Проектирование автоматизированных систем

направления подготовки

«Автоматизация технологических процессов и производств »

Одобрено

редакционно-издательским советом

Саратовского государственного

технического университета

Саратов 2019

Цель работы: получение практических навыков в моделировании устройства цифрового управления, создании его логической и принципиальной схемы, а также в разработке печатной платы данного устройства.

Содержание работы: проектирование устройства цифрового управления с решением задач оптимизации компоновки и размещения элементов, что в себя включает:

Ø составление таблицы истинности и получение исходного логического выражения;

Ø составление карты Карно и получение минимизированного логического выражения;

Ø составление моделей логической и принципиальной электрической схемы соединений элементов, описаниеэлементов схемы и подтверждение её работоспособности путем моделирования в приложении EWB;

Ø построениеГКС, ГЭК и ВГС;

Ø обеспечение оптимального размещения элементов на плате;

Ø выполнение трассировки в приложении SprintLayout.

ПРОЕКТИРОВАНИЕ УСТРОЙСТВА ЦИФРОВОГО УПРАВЛЕНИЯ

Рассмотрим порядок выполнения работы на примере.

Задана функция f = ∑ 1, 2, 9.

1. Составим таблицу истинности для заданной функции (рис. 1):

| A | B | C | D | Y | |

Рис.1. Таблица истинности

На основании составленной таблицы истинности получим исходное логическое выражение схемы:

Y =

2. Для минимизации схемы составим карту Карно для заданного выражения:

|

|

|

| ||

| |||||

| 1 | ||||

| |||||

|

Рис.2. Карта Карно

Логическое выражение минимизированной схемы имеет вид:

Y =

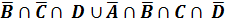

3. По минимизированному логическому выражению составим логическую схему в программе «WORKBENCH»:

| A |

| YL |

| C |

| B |

| D |

Рис.3. Логическая схема в программе «WORKBENCH»

Для реализации принципиальной электрической схемы выбираем соответствующие микросхемы из приложения 1:

SN7404N (1 штука) – реализует шесть логических элементовНЕ;

SN7408N(2штуки) – реализует четыре двухвходовых логических элемента И;

SN7432N (1 штука) –реализует четырёхвходовый логический элемент ИЛИ.

Данные микросхемы построены по технологии КМОП, напряжение питания Uпит = 5 В, все микросхемы установлены в стандартных корпусах DIP14 с 14 выводами, расстояние между выводами равно 2,56 мм.

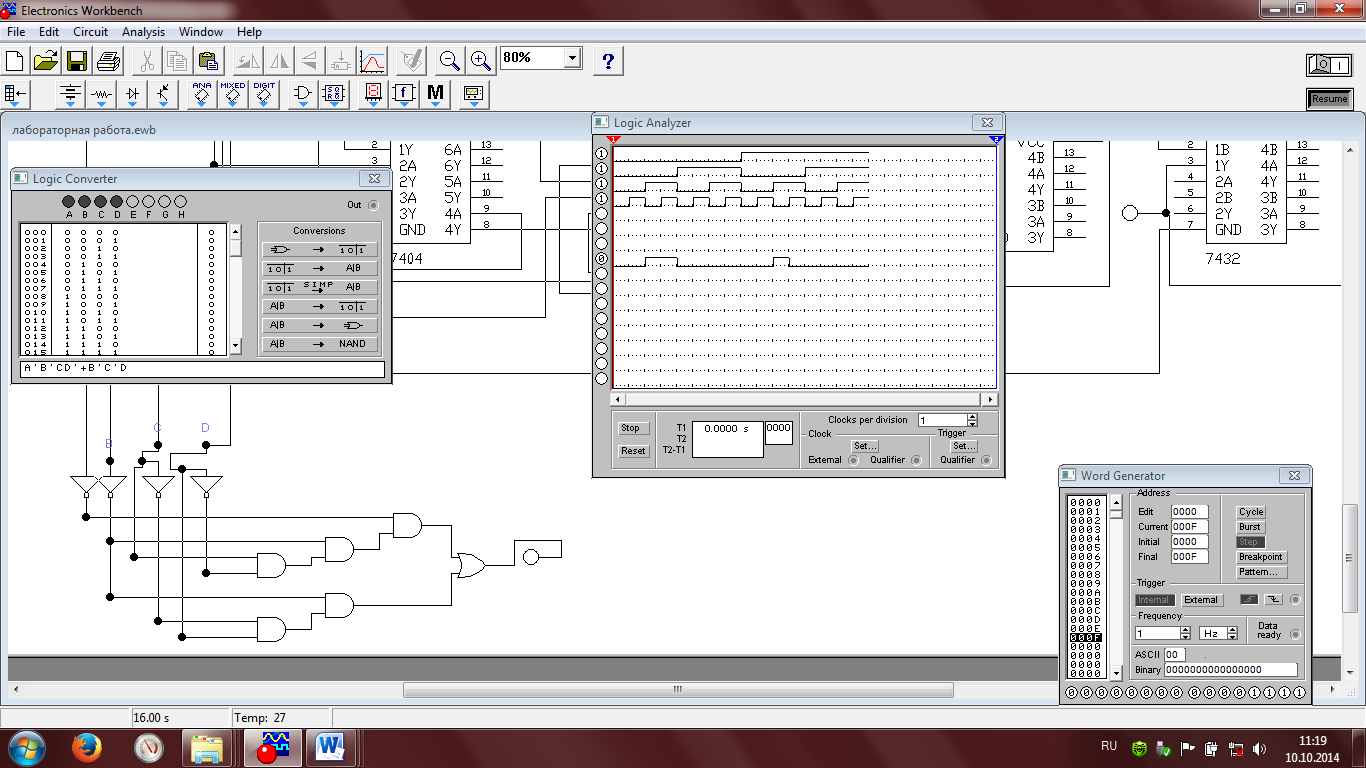

Смоделируем принципиальную электрическую схему (рис.4):

| A B CD |

| YL l |

| YП |

| LA |

Рис.4. Модель электрической принципиальной схемы

К выходам обоих схем подключим логический анализатор (LA), показания которого подтверждают работоспособность смоделированных логической (YL) и принципиальной(YП) схем (рис.5):

| A |

| YL l |

| YП |

| D |

| B |

| C |

| A |

Рис.5. Показания логического анализатора

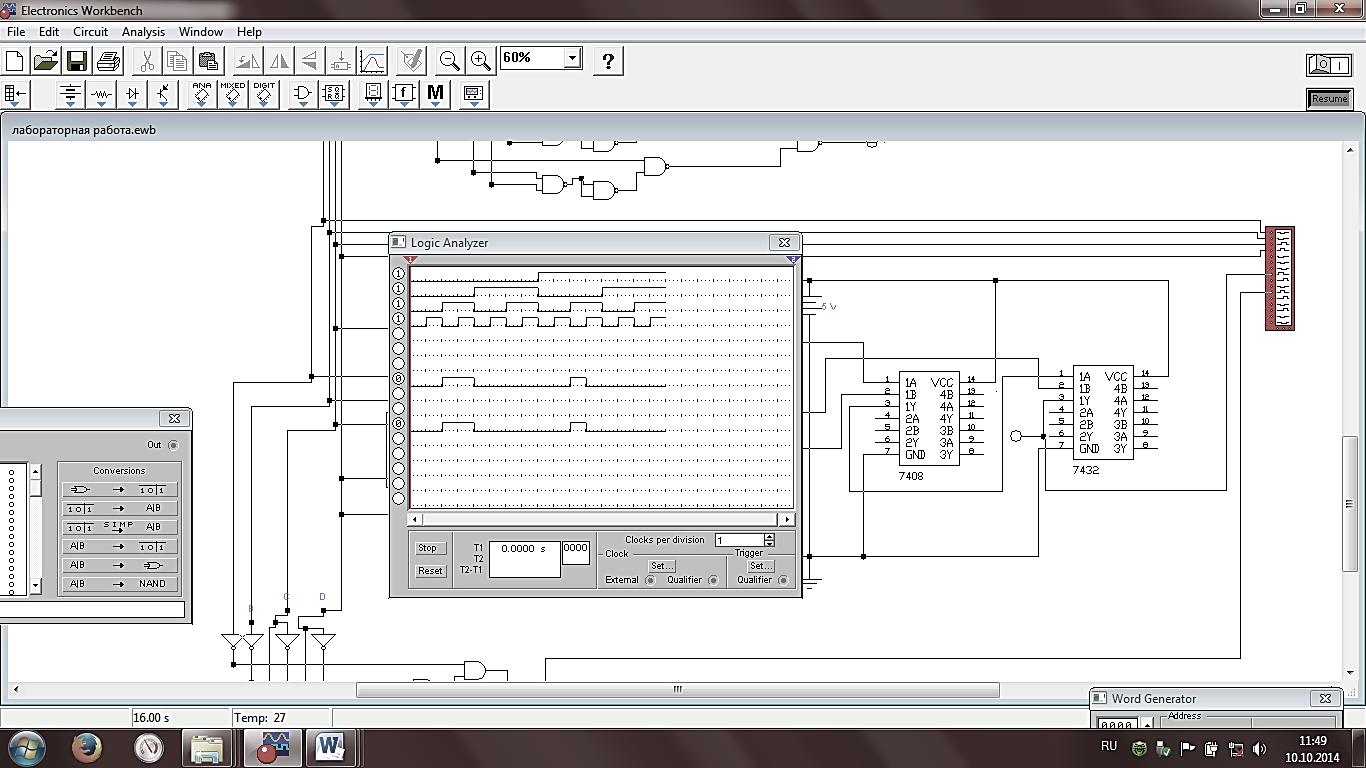

4. Для подробного описания электрической схемы используется граф коммутационной схемы (ГКС):

ГКС = (Е, С, V, А, В),

где: Е – множество элементов, |Е| = n;

С – множество выводов, |С| = k;

V – множество цепей (комплексов), |V| = m;

A – матрица связей между комплексами и выводами;

В – матрица связей между элементами и выводами.

На схеме (рис.6) обозначим множество элементов - (E), множество контактов - (С) и множество цепей (комплексов) - (V).

E = {ei}, i =

V = {vi}, i =

C = {ci}, i =

По полученным данным сформируем матрицу связи между комплексами и выводами (Матрица А) и матрицу связей между элементами и выводами (Матрица В).

Рис.6.

Матрица А. А = ççаijçççVï´êCï =

| С\V | |||||||||||||||||||||||||||||||||||||||||

Матрица В. B = êêbijïïêEï´çCï =

| С\Е | |||||||||||||||||||||||||||||||||||||||||

Матрицы А и В являются сильно разрежёнными и информация, содержащаяся в них, является избыточной для задач проектирования. Поэтому используем более компактное представление данных о проектируемой схеме в виде графа элементных комплексов (ГЭК):

ГЭК = (E, V, Q),

где: Е и V – множества элементов и цепей (комплексов);

Q – матрица отношений между этими множествами.

Рис.7. Граф элементных комплексов

Ребрами связаны вершины, принадлежащие разным множествам. Такой граф называется двудольным. Отношение между вершинами этого графа описывает матрица Q.

Матрица Q. Q = ççqijïççEï´çVï =

| E\V | ||||||||||||||||

| nS |

ns – количество «единиц» в s-м столбце матрицы Q.

n1 = n5 = 5;

n4 = n6 = 3;

n2 = n3 = n7 = n8 = n9 = n10 = n13 = n14 = n15 = n16= 2;

n11 = n12 = 1.

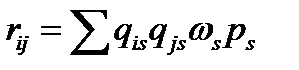

Н аиболее компактным формализованным представлением схемы, используемым при решении задачи компоновки и размещения, является взвешенная граф схема (ВГС):

ВГС = (E, R)

где: Е – множество элементов;

R – матрица смежности, элементы rij которой отображают связность элемента ei с элементом ej.

Для решения задачи компоновки и размещения необходимо оценивать связность элементов между собой. Для такой оценки показателя связности rij элемента ei с элементом ej рассчитываем математическое ожидание (вероятность) – ps появления ребра полного графа при построении дерева s -й цепи по формуле:

p1 = p5 = 2/5;

p4 = p6 = 2/3;

p2 = p3 = p7 = p8 = p9 = p10 = p13 = p14 = p15 = p16= 1;

p11 = p12 = 2.

| 16 |

| S=1 |

Так как все цепи в нашей схеме имеют одинаковую важность, принимаем ωs = 1. Вычисляем значения rij и формируем матрицу R:

Матрица R.

| e | ||||||

| e | 64/15 | 32/15 | 12/15 | 27/15 | ||

| 64/15 | 77/15 | 27/15 | 12/15 | |||

| 32/15 | 77/15 | 27/15 | 27/15 | |||

| 12/15 | 27/15 | 27/15 | 27/15 | |||

| 27/15 | 12/15 | 27/15 | 27/15 |

Строим взвешенный граф схемы (ВГС):

Массив связи между элементами:

| элементы e | Вес связи | |

| 64/15 | ||

| 32/15 | ||

| 12/15 | ||

| 27/15 | ||

| 77/15 | ||

| 27/15 | ||

| 12/15 | ||

| 27/15 | ||

| 27/15 | ||

| 27/15 |

5. На плате размещаем пять элементов: разъём (e0) и четыре микросхемы (e1, e2, e3 и e4). Источник питания, светодиод и кодовый генератор размещаем вне платы. Их подключаем через семиконтактный разъём e0.

Выбираем неперемещаемый элемент, в данном случае это разъем e0. Устанавливаем его в начало нашей платы. С него и начнем решать задачу размещения элементов на плате. Далее по взвешенному графу схемы находим тот элемент, который по весу наиболее связан с e0, то есть вес их связей наибольший - это элемент e1 (64/15). На плате его расположим рядом с элементом e0. С элементами e0 и e1 наибольшую суммарную связь имеет элемент e2 (109/15), поэтому размещаем его за элементом e1. Элемент e3 и e4 можно разместить после элемента е2 в произвольном порядке, так как вес их связи с уже размещёнными элементами e0 , e1, e2 одинаков (66/15).

6.Разрабатываем печатную плату в соответствии с проведённой оптимизацией размещения:

Сторона монтажа:

Сторона пайки:

| e1 |

| e2 |

| e3 |

| e4 |

| S1,5 s |

ВЫВОД

В ходе выполнения контрольной работы выполнили синтез схемы устройства цифрового управления, создали его логическую и принципиальную схемы, путем моделирования убедились в его работоспособности, а также произвели конструирование печатной платы. При проектировании были выполнены необходимые расчеты и построены матрицы и графы для оптимизации компоновки и размещения элементов на плате.

ЗАДАНИЕ

Разработать, спроектировать и смоделировать схему устройства цифрового управления в соответствии с номером зачетной книжки.

При конструировании печатной платы решить задачи оптимизации компоновки и размещения элементов на плате.

СПИСОК ЛИТЕРАТУРЫ

1. Колосов В.Г., Мелехин В.Ф. “Проектирование узлов и систем автоматики и вычислительной техники”.

2. Тарабрин Б.В. “Справочник по интегральным микросхемам”.

3. БедрековскийМ.А., КосырбасовА.А., МальцевП.П.

“Интегральные микросхемы: взаимозаменяемость и аналоги”.

ОПТИМИЗАЦИЯ КОМПОНОВКИ И РАЗМЕЩЕНИЯ

ЭЛЕМЕНТОВ НА ПЕЧАТНЫХ ПЛАТАХ

Методические указания

для выполнения контрольной работы

Составил Виноградов Михаил Владимирович

Приложение 1.

| Функциональное назначение | Отечественные микросхемы серии К155 и КМ155 | Зарубежные аналоги |

| Ждущий мультивибратор с логическим элементом на входе | АГ1 | SN 74121N |

| 2 ждущих мультивибратора | АГ3 | SN 74123N |

| 2 ждущих мультивибратора | АГ3 (М) | SN 64123J |

| Двоично-десятичный/десятичный дешифратор с высоковольтным выходом | ИД1 | SN 74141N |

| Двоично-десятичный/десятичный дешифратор с высоковольтным выходом | ИД1 (М) | SN 64151J |

| Дешифратор/демультиплексор(4*6) | ИД3 | SN 74154N |

| Два дешифратора/демультиплексора (2*4) | ИД4 | SN 74155N |

| Два дешифратора/демультиплексора (2*4) | ИД4 (М) | SN 64155J |

| Двоично-десятичный/десятичный дешифратор с повышенной нагрузочной способностью | ИД10 | SN 74145N |

| Восьмеричный шифратор приоритетов(8*3) | ИВ1 | SN 74148N |

| Десятичный счетчик (деление на2 и 5) | ИЕ2 | SN 7490N |

| Десятичный счетчик (деление на2 и 5) | ИЕ2 (М) | SN6490J |

| Счетчик-делитель на 12 (деление на 2 и 6) | ИЕ4 | SN 7492N |

| Счетчик-делитель на 12 (деление на 2 и 6) | ИЕ4 (М) | SN6492J |

| Четырехразрядный двоичный счетчик (Деление на 2 и 8) | ИЕ5 | SN 7493N |

| Четырехразрядный двоичный счетчик (Деление на 2 и 8) | ИЕ5 (М) | SN6493J |

| Синхронный реверсивный двоично- десятичный счетчик | ИЕ6 | SN 74192N |

| Синхронный реверсивный двоично- десятичный счетчик | ИЕ6 (М) | SN64192J |

| Синхронный реверсивный двоичный счетчик | ИЕ7 | SN 74193N |

| Синхронный реверсивный двоичный счетчик | ИЕ7 (М) | SN64193J |

| Шестиразрядный двоичный синхронный умножитель | ИЕ8 | SN 7497N |

| Шестиразрядный двоичный синхронный умножитель | ИЕ8 (М) | SN6497J |

| Четырехразрядный синхронный десятичный счетчик | ИЕ9 | SN 74160N |

| Четырехразрядный асинхронный десятичный счетчик | ИЕ14 | SN 74196N |

| Одноразрядный полный сумматор | ИМ1 | SN 7480N |

| Одноразрядный полный сумматор | ИМ1 (M) | SN 6480J |

| Двухразрядный двоичный полный сумматор | ИМ2 | SN 7482N |

| Функциональное назначение | Отечественные микросхемы серии К155 и КМ155 | Зарубежные аналоги |

| Двухразрядный двоичный полный сумматор | ИМ2 (М) | SN6482J |

| Четырехразрядный двоичный полный сумматор | ИМ3 | SN7483N |

| Четырехразрядный двоичный полный сумматор | ИМ3(М) | SN6483J |

| Восьмиразрядная схема контроля четности и нечетности | ИП2 | SN74180N |

| Восьмиразрядная схема контроля четности и нечетности | ИП2 (М) | SN64180J |

| Четырехразрядное арифметическо- логическое устройство | ИП3 | SN74181N |

| Схема ускоренного переноса для арифметическо-логических устройств …181…и ИП3 | ИП4 | SN74182N |

| Схема ускоренного переноса для арифметическо-логических устройств …181…и ИП3 | ИП4 (М) | SN64182J |

| Четырехразрядный универсальный регистр сдвига с параллельным вводом и выводом инф-ии. | ИР1 | SN7495N |

| Четырехразрядный универсальный регистр сдвига с параллельным вводом и выводом инф-ии. | ИР1 (M) | SN6495J |

| Восьмиразрядный универсальный регистр сдвига | ИР13 | SN74198N |

| Четырехразрядный регистр с тремя состояниями выхода | ИР15 | SN74173N |

| Четырехразрядный регистр с тремя состояниями выхода | ИР15 (М) | SN64173J |

| Регистровый файл(4*4) с открытым коллекторным выходом | ИР32 | SN74170N |

| Селектор/мультиплексор(16*1) | КП1 | SN74150N |

| Два селектора/мультиплексора(4*1) | КП2 | SN74153N |

| Два селектора/мультиплексора(4*1) | КП2(M) | SN74153J |

| Селектор/мультиплексор(8*1) | КП5 | SN74152N |

| Селектор/мультиплексор(8*1) | КП5(M) | SN74152J |

| Селектор/мультиплексор(8*1) со стробированием | КП7 | SN74151N |

| Селектор/мультиплексор(8*1) со стробированием | КП7(M) | SN74151J |

| 2 логических элемента 4И-НЕ | ЛА1 | SN7420N |

| 2 логических элемента 4И-НЕ | ЛА1 (М) | SN6420J |

| Логический элемент 8И-НЕ | ЛА2 | SN7430N |

| Логический элемент 8И-НЕ | ЛА2(М) | SN6430J |

| 4 логических элемента 2И-НЕ | ЛА3 | SN7400N |

| 4 логических элемента 2И-НЕ | ЛА3(М) | SN6400J |

| Функциональное назначение | Отечественные микросхемы серии К155 и КМ155 | Зарубежные аналоги |

| 3 логических элемента 3И-НЕ | ЛА4 | SN7410N |

| 3 логических элемента 3И-НЕ | ЛА4 (М) | SN6410J |

| 2 логических элемента 4И-НЕ с повышенной нагрузочной способностью | ЛА6 | SN74140N |

| 2 логических элемента 4И-НЕ с повышенной нагрузочной способностью | ЛА6 (М) | SN64140J |

| 2 логических элемента 4И-НЕ с открытым коллекторным выходом | ЛА7 | SN7422N |

| 2 логических элемента 4И-НЕ с открытым коллекторным выходом | ЛА7 (М) | SN6422J |

| 4 логических элемента 2И-НЕ с открытым коллекторным выходом | ЛА8 | SN7401N |

| 4 логических элемента 2И-НЕ с открытым коллекторным выходом | ЛА8(М) | SN6401J |

| 3 логических элемента 3И-НЕ с открытым коллекторным выходом | ЛА10 | SN7412N |

| 3 логических элемента 3И-НЕ с открытым коллекторным выходом | ЛА10(М) | SN6412J |

| 4логических элемента 2И-НЕ с высоковольтным открытым коллекторным выходом | ЛА11 | SN7426N |

| 4логических элемента 2И-НЕ с высоковольтным открытым коллекторным выходом | ЛА11(М) | SN6426J |

| 4 логических элемента 2И-НЕ с повышенной нагрузочной способностью | ЛА12 | SN7437N |

| 4 логических элемента 2И-НЕ с повышенной нагрузочной способностью | ЛА12(М) | SN6437J |

| 4 логических элемента 2И-НЕ с открытым коллекторным выходом и повышенной нагрузочной способностью | ЛА13 | SN7438N |

| 4 логических элемента 2И-НЕ с открытым коллекторным выходом и повышенной нагрузочной способностью | ЛА13(М) | SN6438J |

| 2 4-ех входовых расширителя по ИЛИ с инверсией и без инверсии на выходе | ЛД1 | SN7460N |

| 2 4-ех входовых расширителя по ИЛИ с инверсией и без инверсии на выходе | ЛД1(M) | SN6460J |

| 4 логических элемента 2ИЛИ-НЕ | ЛЕ1 | SN7402N |

| 4 логических элемента 2ИЛИ-НЕ | ЛЕ1 (М) | SN6402J |

| 2 логических элемента 4ИЛИ-НЕ со стробированием и расширителем по ИЛИ | ЛЕ2 | SN7427N |

| 2 логических элемента 4ИЛИ-НЕ со стробированием | ЛЕ3 | SN7425N |

| 2 логических элемента 4ИЛИ-НЕ со стробированием | ЛЕ3 (М) | SN6425J |

| 3 логических элемента 3ИЛИ-НЕ | ЛЕ4 | SN7427N |

| 4 логических элемента 2ИЛИ-НЕ с повышенной нагрузочной способностью | ЛЕ5 | SN7428N |

| Функциональное назначение | Отечественные микросхемы серии К155 и КМ155 | Зарубежные аналоги |

| 4 логических элемента 2ИЛИ-НЕ для работы на магистрали | ЛЕ6 | SN74128N |

| 4 логических элемента 2И | ЛИ1 | SN7408N |

| 4 логических элемента 2И | ЛИ1(М) | SN6408J |

| 6 логических элементов НЕ | ЛН1 | SN7404N |

| 6 логических элементов НЕ | ЛН1(М) | SN6404J |

| 6 логических элементов НЕ с открытым коллекторным выходом | ЛН2 | SN7405N |

| 6 ЛЭ НЕ с высоковольтным открытым коллекторным выходом и повышенной нагрузочной способностью | ЛН3 | SN7406N |

| 6 ЛЭ НЕ с высоковольтным открытым коллекторным выходом и повышенной нагрузочной способностью | ЛН5 | SN7416N |

| 6 шинных драйверов с 3 состояниями выхода без инверсии | ЛН6 | SN74366N |

| 4 логических элемента 2ИЛИ | ЛЛ1 | SN7432N |

| 4 логических элемента 2ИЛИ | ЛЛ1(M) | SN6432J |