ЭМУЛЯТОР ВОСЬМИРАЗРЯДНОГО

ПРОЦЕССОРА

МЕТОДИЧЕСКИЕ УКАЗАНИЯ ПО ВЫПОЛНЕНИЮ ЛАБОРАТОРНЫХ РАБОТ ДЛЯ СТУДЕНТОВ СПЕЦИАЛЬНОСТИ 220100 «ЭВМ, СИСТЕМЫ, КОМПЛЕКСЫИ СЕТИ» ПО ДИСЦИПЛИНЕ «ОРГАНИЗАЦИЯ ЭВМ И СИСТЕМ»

МОСКВА,2001

Составители: Е.Л. Иванов, Е.В. Бражникова, Б.И. Нефедов, Ю.Д. Тювин

Составители: Е.Л. Иванов, Е.В. Бражникова, Б.И. Нефедов, Ю.Д. Тювин

Редактор В.А. Губарев

Печатается по решению редакционно – издательского Совета Московского институра радиотехники электроники и автоматики, (технический университет).

Рецензенты: К.С.Хомяков, В.И. Лебедев

Ó Московский институт

радиотехники, электроники

и автоматики, (технический унверситет),2001.

Цель лабораторных работ.

Целью лабораторных работ является изучение структуры и принципов функционирования 8 – разрядного процессора типа КР580ВМ80.

Изучение выполняется на эмуляторе в потактном, покомандном и автоматическом режимах.

Исследуются основные группы команд в потактном режиме и изучается структура процессора, взаимодействие основных его блоков при выполнении команд различного типа. Эмулятор позволяет фиксировать в каждом такте состояние процессора, а именно состояние всех регисторов, счетчиков, флагов, управляющих сигналов, № текущего такта и № текущего цикла выполнение команды.

Эмулятор позволяет исследовать структуру процессора на программном уровне в покомандном и автоматическом режимах.

Описание эмулятора.

Эмулятор 8 – разрядного процессора реализован на ЭВМ типа IBM – PCAT.

При входе в эмулятор открывается окно ПМК КР580ВМ80, в котором изображена структура “стенда”.

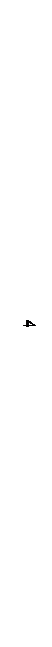

В верхней части окна (рис.1) указываются режимы работы: “файл”, “структурная схема”, “система команд”, “помощь”.

Строкой ниже указывается адрес (состояние шины адреса в шестнадцатиричной системе счисления), данные (состаяние шины данных в шестнадцатиричной системе счисления).

Далее показано окно, в котором указывается адрес ОЗУ и его содержимое, или номер регистра и его содержимое.

В окне флагов записывается состояние флагов Z, S, P, C, AC на данный момент выполнения команды процессором, где

Z – признак нулевого результата,

S – знак,

| |||||

| |||||

| |||||

P – признак четного количества единиц результата,

С – признак переноса из старшего разряда,

АС – признак дополнительного переноса из старшего разряда младшей тетрады байта.

Для ввода информации используется клавиатура, которая подразделяется на цифровую от 0 до F и режимную SpL, SpH, PcL, PcH, ОЗУ, Сброс ОЗУ, Регистр, Сброс рег.

Для ввода информации ОЗУ необходимо нажать кнопку «ОЗУ»,затем кнопку «Ввод». После этого ввести в данную ячейку код команды или данные.

Для ввода информации в регистры требуется нажать клавишу «Регистр», клавишу «Ввод», а затем на цифровой клавиатуре произвести ввод данных.

Клавиши SpL, SpH и PcL, PcH позволяют записывать адреса в указатель стека и счетчик команд.

При вводе любой информации необходимо выполнить нажатия “мышкой” на клавишу “ввод”.

В первой части “окна” расположены регистры процессора:

А – аккумулятор;

В,С,D,Е,H,L – общие регистры RON, PC – программный счетчик;

SP – указатель стека.

Указатель стека – указывает вершину стека FFFF (перевернутый стек).

В области окна “выполнение программы” задается режим:

- автоматический режим – при нажатии кнопки “автоматический режим” – выполняется программа до команды HLT;

- покомандный режим – при нажатии кнопки “покомандный режим” реализуется весь цикл исполнения команды;

- потактный режим – при каждом нажатии кнопки “выполнить” осуществляется выполнение одного такта работы процессора.

В правой части окна экрана расположено “окно”, в котором указана “Позиция” адресного пространства ОЗУ, в котором производится набор программы: адрес команды, КОП, ассемблерный код команды. “Позиция” указывает область адресного пространства ОЗУ, в котором прокруткой “∆” или “Ñ” можно указывать начало требуемого адресного пространства.

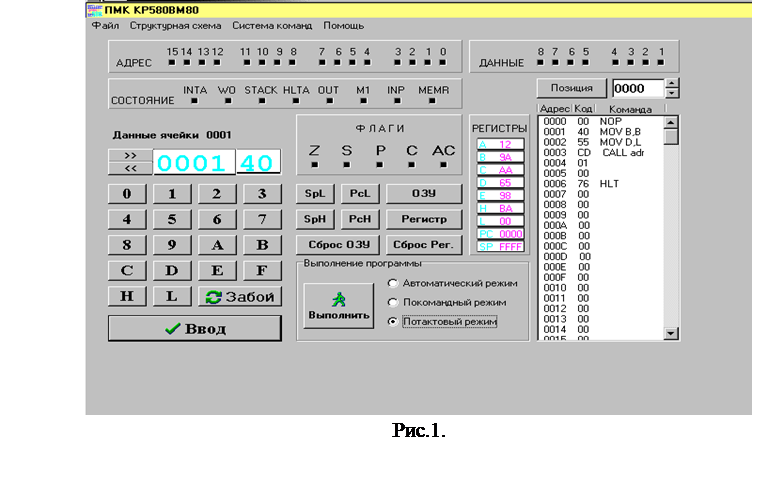

При указании “мышью” позиции “структурная схема” раскрывается следующее окно, в котором показана структурная схема процессора (рис.2).

Структурная схема 8-разрядного процессора включает АЛУ с входными регистрами(“Аккумулятор”, “Буф.Регистр 1”, “Буф.Регистр 2”), “Рег.Признаков”, “Схема десятичной коррекции”; “Регистр команд”, “Деш. команд”, “Блок синхронизации и управления”, “Регистры временного хранения W и Z”, “регистры общего назначения B,C,D,E,H,L”, указатель стека, счетчик команд, схемы инкремента и декремента.

Указанные схемы подключены к внешним шинам адреса и данных через “Буферные регистры” адреса и данных.

Для организации режимов работы, как и в предыдущем окне, в данном расположена клавиатура ввода информации, аналогичная клавиатуре предыдущего окна, и соответствующие режимные клавиши, а также клавиши режима работы:

автоматический режим – AT;

покомандный режим – КМ;

потактный режим – ТК.При потактном режиме можно исследовать выполнение любой команды.

При каждом нажатии кнопки “Вып.” реализуется очередной такт работы процессора. При этом фиксируется на экране все состояния его регистров, номер такта, номер цикла, состояния управляющих сигналов, регистр состояния и PSW.

Режим работы с клавиатурой соответствует предыдущему окну.

|

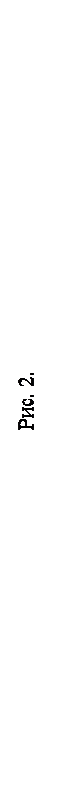

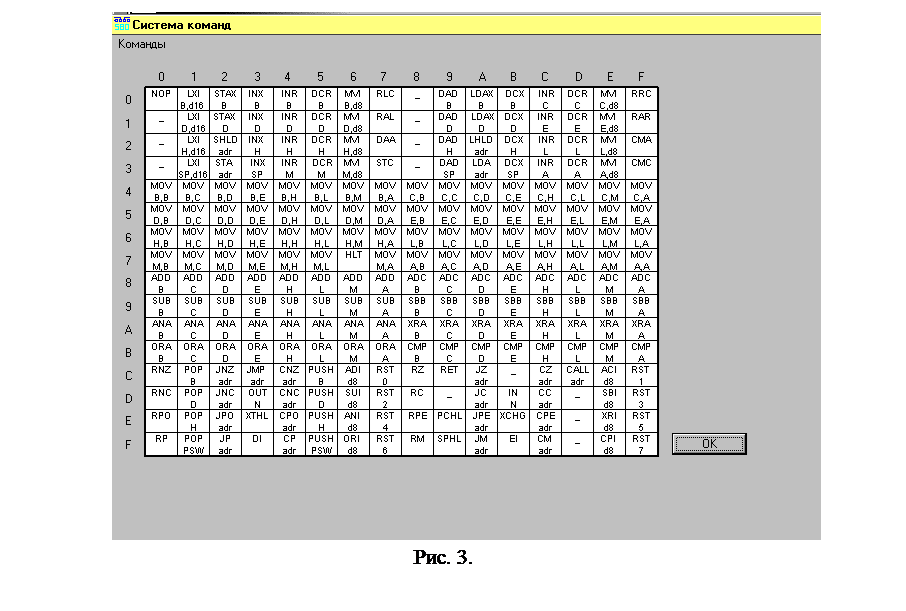

При указании “мышью” в окне “ПМК КР580ВМ80” на позицию. “Система команд”, раскрывается окно “Команды” в

котором предоставлена таблица (рис.3) системы команд. Код команды определяется по матрице в 16-ричной системе счисления по столбцу и строке таблицы: например: MOV B, C – 41 или HLT – 76.

Система команд процессора.

Команды процессора представлены следующими форматами: однобайтным, двухбайтным и трехбайтным. За одно обращение к памяти выбирается один байт команды и размещается в регистре команд. Если команда имеет 2 или 3 байта, то второй и третий байты записываются в программно недоступные регистры W и Z, которые называются регистрами временного хранения.

В процессоре применяются четыре следующие способа адресации:

- прямая адресация (относится к командам обращение к памяти, причем во втором и третьем байтах команды записывается адрес ОЗУ);

- регистровая адресация (используется для обращения к внутренним регистрам процессора);

- непосредственная адресация (в поле команды размещается операнд);

- регистровая косвенная адресация (в поле команды размещается адрес регистровой пары, в которой записан адрес ОЗУ); в качестве регистровых пар могут быть использованы пары регистров В-С, D-Е, H-L, причем последняя пара H-L – адресует ячейку памяти М, которая называется псевдорегистром.

Система команд процессора включает 5 групп команд:

1) команды пересылок;

2) команды арифметических операций;

3) команды логических операций;

4) команды передачи управления;

| |||

|

5) команды обращение к стеку, ввода-вывода и управление МП – системой.

Группы команд пересылок

Эти команды производят обмен между регистрами POН и ОЗУ.

| 1. МОV R1,R2 | передать с регистра на регистр, (R2) ® R1 |

| 2. MOV R,M | передать из памяти ОЗУ ® РОН, т.е. [HL] ® R, (H) – старший полуадрес ячейки памяти, (L)- младший полуадрес; |

| 3. MOV M,R | передать в память (POH) ® ОЗУ, т.е. содержимое регистра R записать в ОЗУ по адресу, указанному в регистровой паре HL: (R) ® ОЗУ [HL] |

| 4. MVI R, data | передать непосредственный операнд, в R передается 8 – разрядный операнд, который находится во втором байте команды; |

| 5. MVI M, data | передать в память непосредственный операнд <data> ® ОЗУ [HL]. |

| 6. LXI RP, data | загрузить непосредственный 16-разрядный операнд. Команда 3-байтная. Здесь RP=BC, DE,HL Ri байт 3 Ri+I байт 2, где Ri – B, D,H. Ri+I – C, E, L. |

| 7. LDA addr | загрузить аккумулятор содержимым ячейки памяти адреса addr; команда трехбайтная, 2 и 3. |

| 8. STA addr | запомнить содержимое аккумулятора в ОЗУ по <addr>, т.е. (A) ® ОЗУ [байт3, байт2 адреса <addr>]. |

| 9. LHLD addr | загрузить регистры H и L операндом из ОЗУ по addr; команда выполняется следующим образом: 1 этап: (addr) ®L. 2 этап: инкремент адреса (addr) +I. 3 этап: (addr) + I®H. |

| 10 SHLD addr | запомнить содержимое регистров H и L в ОЗУ по адресу addr; команда выполняется следующим образом: 1 этап: (L) ® ОЗУ [addr]. 2 этап: инкремент адреса [(addr) + I]. 3 этап: (H) ® ОЗУ [(addr) +I]. |

| 11. LDAX RP | загрузить А с косвенной адресацией, т.е. из ОЗУ, адрес ячейки которого указан в регистровой паре, прочитать операнд и передать его в аккумулятор. |

Группа команд арифметических операций

Эти команды выполняют арифметические операции и поразрядные булевы операции над данными, размещенными в регистрах РОН и в памяти. Они вырабатывают признаки, которые поступают в регистр признаков. Эти признаки еще называются флажками. Сложение и вычитание делаются в дополнительном коде.

| 1.ADD R | сложить с регистром (R)+(A) ®A |

| 2. ADD M | сложить с памятью (A)+[HL] ®A |

| 3. ADI data | сложить непосредственно (A)+<data> ®A., т.е. сложить содержимое аккумулятора со вторым байтом команды, результат записать в аккумулятор. |

| 4. ADC R | сложить с регистром и с битом переноса (A)+(R)+C. ®A |

| 5.ADC M | сложить с памятью и с битом переноса (A)+[HL]+C ®A |

| 6.ACI data | сложить с непосредственным операндом и битом переноса (A)+<data>+C ®A |

| 7.SUB R | вычесть содержимое регистра (A)-(R) ®A |

| 8.SUB M | вычесть содержимое памяти (A)-[HL] ®A |

| 9.SUI data | вычесть непосредственный операнд |

| 10. SBB R | вычесть содержимое регистра с займом (A)-(R)-C ®A |

| 11. SBB R | вычесть содержимое памяти с займом (A)-(R)-C ®A |

| 12. SBI data | вычесть непосредственный операнд с займом (A)-<data>-C ®A |

| 13. INR R | увеличить на “I” содержимое регистра (R)+I ®R |

| 14. INR M | увеличить на “I” содержимое памяти по адресу, указанному в HL. |

| 15. DCR R | уменьшить на “I” содержимое регистра (R)-I ®R |

| 16.DCR M | уменьшить на “I” содержимое памяти по адресу, указанному в HL. |

| 17. INX RP | увеличить на “I” содержимое регистровой пары. |

| 18. DAD RP | сложить содержимое регистров HL RP и результат записать в регистровую пару HL. |

| 19. DAA | выполнить десятичную коррекцию содержимого аккумулятора; десятичная операция выполняется по правилам десятичной арифметики. |

Примечание. Команды 13-17 используются для организации счетчиков циклов в программах.

Группа команд логических операций.

| 1. ANA R | логическая “И” c регистром РОН; (A)&(R) ® A,C:=0, AC:=0. Команда используется для выделения части слова: 00110111&00001111=00000111 |

| 2. ANA M | логическая “И” c памятью; [HL]&(A) ® A,C:=0, AC:=0. |

| 3. ANI data | логическая “И” c непосредственным операндом; <data>&<R> ® A,C:=0, AC:=0. |

Примечание. Команды 1-3 используются для выделения частей машинных слов.

| 4. XRA R | сложение по mod 2 с регистром (A)Å(R). ®A |

| 5. XRA M | сложить по mod2 содержимое А с содержимым памяти по адресу HL. |

| 6. XRI data | сложить по mod2 содержимое А с непосредственным операндом. |

| 7. ORA R | “ИЛИ” с регистром (А)Ú(R) ®A,C:=0, AC:=0. |

| 8. ORA M | “ИЛИ” с памятью [HL]Ú(A) ®A,C:=0, AC:=0. |

| 9. ORA data | “ИЛИ” с непосредственным операндом (A)Ú <data> ®A,C:=0, AC:=0. |

| 10. CMP R | сравнить с регистром. Сравнение делается через вычитание (A)-(R) результат в А не записывается, но регистр признаков устанавливается в соответствии с результатом вычитания: если(A)=(R), то Z:=1, если (A) ¹ (R),то S:=1, иначе Z:=0, S:=0. |

| 11. CMP M | сравнение с памятью (A) –[HL]. |

| 12. CPI data | сравнение с непосредственным операндом; (A)-<data>. В остальном – аналогично команде CMP R. |

| 13. RLC | циклический сдвиг влево. Все сдвиги делаются только над содержимым А. Сдвиг на один разряд: косая передача в АЛУ. Сдвиг на n разрядов можно организовать только программно). |

| 14. RRC | циклический сдвиг вправо A(n+1) ® A(n) |

| 15. RAL | арифметический сдвиг влево. |

| 16. RAR | арифметический сдвиг вправо. |

| 17. STS | установить в единицу триггер переноса: 1 ®C. |

| 18. CMC | инвертировать содержимое триггера переноса ùC ® C. |

| 19. CMA | инвертировать содержимое аккумулятора ù(A) ®A. |

Группа команд передачи управления

Данная группа команд образует условные, безусловные переходы и обращения к подпрограммам.

| 1. JMP addr | безусловный переход по адресу, указанному во втором и третьем байтах команды. | |

| 2. JC addr | условный переход по единичному значению признака переноса С; если условие выполняется, то адрес перехода записывается на счетчик команд СК, иначе содержимое СК увеличивается на три. | |

| 3. JNC addr | условный переход по нулевому значению признака переноса С. | |

| 4. JZ addr | условный переход по единичному значению признака результата. | |

| 5. JNZ addr | условный переход по нулевому признака Z результата. | |

| 6. JP addr | условный переход по положительному значению результата. | |

| 7. J M addr | условный переход по отрицательному значению результата. | |

| 8. JPE addr | условный переход по четности кода результата. | |

| 9. JPO addr | условный переход по нечетности кода результата. | |

| 10. CALL addr | безусловный переход к подпрограмме; содержимое СК побайтно загружается в стек, а адрес <addr>, указанный в команде, передается на счетчик команд; указатель стека перед каждой загрузкой уменьшается на 1. | |

| 11. RET | возврат из подпрограммы; команда ставится в конце подпрограммы и обеспечивает чтение из стека и загрузку побайтно адреса возврата в счетчик команд; после каждого обращения к стеку указатель стека УС увеличивается на “1”. | |

Группа команд обращения к стеку, ввода, вывода, управления МП системой:

| 1. PUSH RP | записать в стек содержимое регистровой пары; команда выполняется следующим образом: а) УС уменьшается на “1”, б) (R) ®ОЗУ (УС – 1), в) (P) ® ОЗУ (УС-2). |

| 2.PUSH PSW | поместить в стек словосостояния процессора, которое включает содержимое А и PSW. Команда выполняется следующим образом: а) УС уменьшается на “1”, б) (A) записывается в ОЗУ по адресу УС-1; УС уменьшается на “1”, в) (PSW) записывается в ОЗУ по адресу УС-2. |

| 3. POP RP | загрузка регистровой пары из стека; команда выполняется следующим образом: а) из ОЗУ по адресу УС читается слово и загружается в регистр Р; указатель стека увеличивается на “1”; б) из ОЗУ по адресу УС+1 читается слово и загружается в регистр R; указатель стека увеличивается на “1”. |

| 4. POP PSW | загрузка аккумулятора и регистра признаков из стека; команда выполняется следующим образом: а) из ОЗУ по адресу УС читается слово и загружается в PSW; указатель стека увеличивается на “1”, б) из ОЗУ по адресу УС+1 читается слово и загружается в А; указатель стека увеличивается на “1”. |

| 5. XTHL | поменять местами содержимое стека и регистровой пары HL; команда выполняется следующим образом: а) меняется местами содержимое регистра H и ячейки ОЗУ по адресу УС, затем УС увеличивается на “1”, б) меняется местами содержимое регистра H и ячейки ОЗУ по адресу УС+1, затем УС увеличивается на “1”. Обмен производится через регистры Z и W. |

| 6. SPHL | передать содержимое регистровой пары HL в счетчик команд: (HL) ®СК. |

| 7. IN port | команда ввода: во втором байте указан адрес порта. |

| 8. OUT port | команда вывода. |

| 9. HLT | команда останова. |

| 10. NOP | пустая команда; после ее выборки счетчик команд автоматически увеличивается на “1”. |

Длительность выполнения команды зависит от типа и формата команды. Самая короткая команда может быть выполнена за 1 цикл и содержать до 5 тактов. Самая длинная команда может выполняться за 5циклов, имея по 5 тактов в каждом цикле.

В окне команд (рис.3) можно получить “помощь” по назначению команды и правилам ее выполнения, указав эту команду “мышкой” и щелкнув ее 2 раза левой кнопкой.

Формат данных.

Процессор обрабатывает двоичные и двоично-десятичные числа, представленные в следующих форматах: целое двоичное число без знака, целое двоичное число со знаком, двоично–десятичное число.

Нумерация разрядов справа налево, знак занимает 8-разряд.

Лабораторная работа №1

Цель лабораторной работы заключается в исследовании работы процессора при выполнении команд различных типов.

Порядок выполнения:

1. Войти в “окно”, “структурная схема микропроцессора”;

2. Установить потактный режим работы, указав “мышкой” кнопку “Тк”;

3. Установить режим “ОЗУ” указав “мышкой” кнопку “ОЗУ”, набрать на цифровой клавиатуре адрес ОЗУ, “нажать” кнопку “Ввод”, затем ввести код требуемой команды согласно варианту задания. Если данная команда требует участия регистров или регистровых пар, необходимо записать в указанные регистры информацию следующим образом: войти в режим работы с регистровой памятью, указав кнопку “Рег.”, а затем, “нажав” на соответствующий регистр “мышкой”. После этого можно осуществлять ввод в регистр информации. Любая процедура записи в ОЗУ или в регистры завершается “нажатием” кнопки “Ввод”.

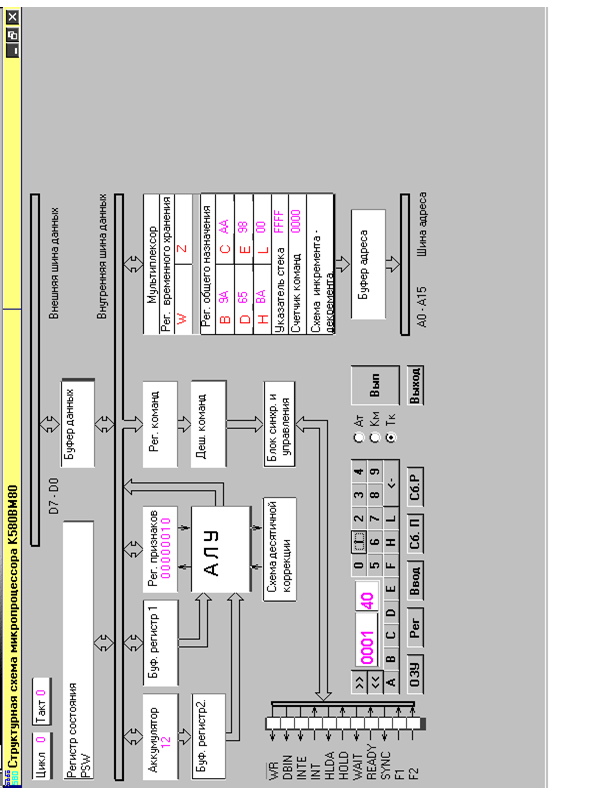

4. Установить адрес ячейки ОЗУ, по которому записана команда.

5. Нажимая “мышкой” кнопку “Вып.”, выполнить команду в потактном режиме, фиксируя в таблице (рис.4), состояние процессора в каждом такте каждого цикла. Структурная схема позволяет проследить в этом режиме последовательность всех процедур выполнения команды.

Варианты заданий

|

| 0A | 1A | 3A | 0E | 1E | 3E | |||||||||

| 4A | 4B | 4D | ||||||||||||

| 6Е | 6E | 7E | 5E | |||||||||||

| C1 | D1 | E1 | D1 | ||||||||||

| 2А | F9 | 2A | C5 | D5 | 2A | D6 | D5 | F9 | 2A | |||||

| B8 | B9 | BA | BB | BC | BD | BE | BF | B8 | B9 | BA | BF | |||

| 0F | 1F | 0F | 1F | 0F | 1F | |||||||||

| 0B | 0C | 0D | 1B | 1C | 1D | 2B | 2C | 2D | 3B | 3C | 3D | |||

| 8A | 8B | 8C | ||||||||||||

| 8E | 9E | 8E | 9E | 8E | 9E | |||||||||

| 2F | 3F | 2F | 3F | 2F | 3F | 2F | 3F | |||||||

| A0 | A1 | A2 | A3 | A4 | A5 | A6 | A7 | A8 | A9 | AA | AB | |||

| B0 | B1 | B2 | B3 | B5 | B6 | B4 | B7 | B0 | B2 | B3 | B4 | |||

| C2 | D2 | E2 | F2 | C3 | CA | DA | EA | FA | C3 | D2 | C2 | |||

| E9 | E9 | E9 | E9 | E9 | E9 | E9 | E9 | E9 | E9 | E9 | E9 | |||

| CD | CD | CD | CD | CD | CD | CD | CD | CD | CD | CD | CD | |||

| C9 | C9 | C9 | C9 | C9 | C9 | C9 | C9 | C9 | C9 | C9 | C9 | |||

| C0 | D0 | E0 | F0 | C4 | D4 | E4 | F4 | CC | DC | EC | CF |

Содержание отчета

Отчет должен содержать:

1. Структурную схему процессора;

2. Таблицы состояния процессора для исследования выполнения каждой команды;

| |||

| |||

| Таблица состояний процессора | Оценка правильности выполнения командой своих функций | ||||||||||||||||||||||

| Состояние регистров общ. назначения | Состояние флагов | ||||||||||||||||||||||

| команда | N цикла | N такта | РК | РС | SP | Буф. адр. | Буф. данных | W | Z | A | B | C | D | E | H | L | Z | S | P | C | AC | ||

|

3. Экспертную оценку выполнения процессором каждой команды (экспертная оценка записывается в правой колонке таблицы; если есть замечания, то указываются процедуры, которые выполнены с ошибкой).

Лабораторная работа №2

Цель лабораторной работы заключается в освоении команд процессора и приобретении навыков составления простых программ в кодах команд. Для выполнения работы необходимо вспомнить алгоритмы выполнения длинных операций (в наборе команд процессора команды длинных операций отсутствуют и реализуются длинные операции программным способом), знать особенности выполнения каждой команды, в том числе, какие признаки формируются в регистре признаков.

Порядок выполнения.

1. Войти в первое окно “ПМК КР580ВМ80”;

2. Установить командный режим;

3. Для каждой задачи разработать функциональную схему алгоритма;

4. По функциональной схеме алгоритма составить программу и ввести ее в ОЗУ (адресное пространство выбрать самостоятельно, но таким образом, чтобы каждой программе отводилось своя область). Поскольку процессор имеет ограниченное число регистров, желательно предусмотреть в каждой программе их автоматическую загрузку;

5. Отладить программы в командном режиме;

|

| n= | n= | n= | n= | n= | n= | n= | n= | n= | n= | n= | n= | |||

| n= | n= | n= | n= | n= | n= | n= | n= | n= | n= | n= | n= | |||

| n= | n= | n= | n= | n= | n= | n= | n= | n= | n= | n= | n=9 | ||

| 5,6,7 |

Задание 1

Составить программу вычисления выражения:

|

|

где аi – число натурального ряда, начиная с “1”.

n – количество чисел.

Задание 2

Составить программу вычисления выражения, приведенного в задании 1.Числа (произвольные значения) разместить в ячейках в ОЗУ.

Задание 3.

Составить программу для пересылки массива данных размерностью n из одной области ОЗУ в другую.

Задание 4.

Составить программу для пересылки массива данных размерностью n из одной области ОЗУ в другую. После пересылки массив должен расположиться в обратном порядке.

Задание 5.

Составить программу умножения однобайтных двоичных чисел.

Задание 6.

Составить программу деления однобайтных двоичных чисел.

Задание 7.

Составить программу вычисления следующего выражения:

N = (a+b) – (cd)

Числа однобайтные. При составлении программы использовать команду обращения к подпрограммам, а в качестве подпрограммы – программу из задания 6.

Содержание отчета

Отчет должен содержать:

1. Задание по каждой задаче

2. Функциональные схемы алгоритмов программы

3. Программа в кодах команд с указанием размещения команд и данных в ячейках ОЗУ и соответствующих регистрах.

4. Комментарии к каждой команде.

Библиография

1. Калабеков В.А. Микропроцессоры и их применение в системах передачи и обработки сигналов. – М.: Радио и связь, 1988. - с. 74-107.

2. Каган Б.М. Сташин В.В. Основы проектирования микропроцессорных устройств автоматики. – М.: Энергоатомиздат. 1987.- с. 15-46.

3. Балашов Е.П., Григорьев В.А. Петров Г.А. Микро и мини ЭВМ. – Л.: Энергоатомиздат, 1984. – с.43-62.