Глава 12 УСТРОЙСТВА СЕНСОРНОГО ВЫБОРА ПРОГРАММ

Общие сведения

Устройства сенсорного выбора программ (СВП) предназначены для переключения поддиапазонов и перестройки на прием одной из программ в пределах каждого поддиапазона электронных селекторов каналов.

Выбор программ с помощью СВП производится простым прикосновением к специальным датчикам или легким нажатием на них.

При этом срабатывают электронные устройства, подключающие к селектору каналов все необходимые напряжения питания, которые заранее выставляются вручную, с учетом действующих в данной местности телевизионных каналов метрового и дециметрового диапазонов.

Обычно СВП содержит шесть датчиков, расположенных на передней панели телевизора, что позволяет без перестройки принимать шесть программ телевизионного вещания. Такого количества переключений, как правило, вполне достаточно.

Каждый датчик снабжается световым индикатором для контроля выбранной программы.

Кроме электронных систем выбора программ применяются также кнопочные системы переключения заранее выставленных напряжений питания к электронным 'селекторам каналов. Такие системы называют псевдосенсорными. Они также содержат шесть кнопок и световые индикаторы.

Однако наличие в псевдосенсорных системах механических элементов снижает четкость их работы. Кроме того, такие системы не позволяют дистанционно управлять телевизором.

Поэтому предпочтение отдается электронным СВП. Прежде чем перейти к детальному рассмотрению отдельных участков СВП, необходимо изучить применяемые в них устройства цифровой техники.

Основы цифровой техники

Цифровая техника — это комплекс электронных устройств, которые способны осуществлять логические преобразования электрических сигналов, представляющих собой цифровую информацию.

Наиболее широкое применение в, цифровой технике нашла двоичная система счисления, использующая для изображения любого числа только две цифры: 0 и 1 (в отличие от десятичной системы счисления, где используется десять цифр: от 0 до 9).

Электрические сигналы, представляющие (кодирующие) цифры двоичной системы счисления, называются двоичными сигналами.

Значение сигнала, кодирующего цифру 1. называется логической единицей (обозначается 1). Значение сигнала, кодирующего цифру 0, называется логическим нулем (обозначается 0). Логической единице соответствует обычно некоторый высокий (положительный) уровень напряжения, а логическому нулю—более низкий уровень напряжения (в том числе его отсутствие или отрицательное значение). Поскольку в цифровой технике электрические сигналы могут принимать только два значения (0 или 1), то переход от одного.

Системой счисления называется метод изображения любых чисел с помощью ограниченного количества цифр.

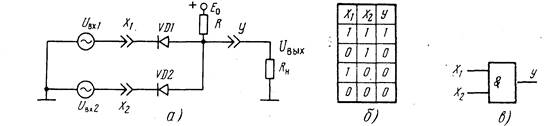

Рис. 12.1. Элемент 2 И:

а— схема элемента; б— таблица истинности; в— условное обозначение значения к другому осуществляется скачкообразно, т. е. сигналы имеют импульсную структуру.

Цифровым или логическим элементом называется электронное устройство, у которого сигнал на выходе связан с входным сигналом (или входными сигналами) по определенному логическому закону.

Основными и в то же время простейшими логическими элементами являются:

И (конъюнктор'); ИЛИ (дизъюнктор 2); НЕ (инвертор3).

Другие, более сложные, логические элементы образуются путем различного сочетания этих трех основных элементов.

•На выходе элемента И вырабатывается сигнал логической единицы тогда и только тогда, когда сигнал единицы подан одновременно на все его входы. Если имеется 0 хотя бы на одном входе, то на выходе будет 0.

На рис. 12.1, а показана схема элемента 2И (число 2 указывает на наличие двух входов элемента, обозначенных XI и Х2). Для этой схемы должны соблюдаться следующие условия:

^•»^пр; ^об»^1>^пр; rh>r\.

*

где г, — внутренние сопротивления источников входных сигналов;

^пр и Гоб— прямые и обратные сопротивления диодов VD1 и VD2;

/?н — сопротивление внешней нагрузки., ^ Если оба диода заперты, то напряжение на нагрузке соответст-

«

F

вует логической единице: [7вых= R^wE.

R\ -Г Ли

Для того чтобы диоды были заперты, входные напряжения C/nxi и С/ох2 должны быть положительным и и иметь значения, не меньшие Е. т. е. также представлять логические единицы. Если хотя бы один из диодов, например VD1, откроется (вследствие понижения напряжения на соответствующем входе XI). то напряжение на выходе У ^Увы.х резко уменьшится и примет значение логического нуля. Низкий уровень напряжения на входе XI в этом случае также соответствует логическому нулю

1 Конъюнкция— это операция логического произведения (операция «И»). 2 Дизъюнкция—это операция логического сложения (операция «ИЛИ»).

f\ _

Инверсия (НЕ)—это операция логического отрицания, т.е. изменения значения данной величины на противоположное ей.

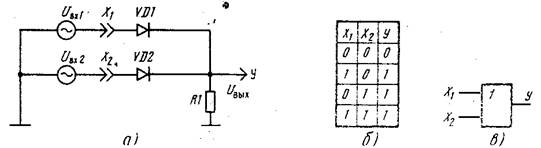

Рис. 12.2. Элемент ИЛИ:

а—схема элемента; б—таблица истинности; а—условное обозначение

Логические преобразования, осуществляемые элементом 2И, представлены таблицей истинности на рис. 12.1, б. Из таблицы видно, что значение сигнала на выходе является произведением сигналов на входах {\/=X\•X•2}. Операция И на графическом изображении элемента (рис. 12.1, а) обозначается символом &.

На выходе элемента ИЛИ будет:

- сигнал логической единицы, когда такой сигнал поступает хотя бы на один из входов:

- сигнал логического нуля, когда все входные сигналы имеют значение нуля.

На рис. 12.2, а показана схема элемента ИЛИ. Для этой схемы должно соблюдаться единственное условие: /об^/?! ^>/"пр-

Если на оба входа, Xt и Х2, поступают сигналы логических нулей (Увх1^0; Увх2^0), то и на выходе У будет нуль. Если же хотя бы на один из входов поступает сигнал логической единицы (сигнал положительной полярности), то на выходе будет единица. Если на оба входа поступают сигналы логических единиц, то на выходе тем более будет единица.

Таблица истинности элемента ИЛИ представлена на рис. 12.2, б. Из таблицы видно, что значение сигнала на выходе является суммой сигналов на входах (У==Х1+Х2). Операция ИЛИ на графическом изображении элемента (рис. 12.2.6) обозначается символом 1.

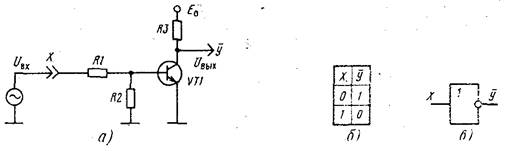

На выходе элемента НЕ осуществляется инвертирование сигнала (изменение его логического содержания на противоположное). Это значит, что при входном сигнале логического нуля на выходе будет единицами наоборот.

На рис. 12.3, а показана схема элемента НЕ на транзисторе. Пока на вход Х поступает сигнал логического нуля (Увх<0), транзистор VT1 закрыт и сигнал на выходе У соответствует логической единице (Увых^^о). Если же сигнал на входе примет значение логической единицы (Увх>0), то транзистор откроется и уровень напряжения на выходе резко понизится, т. е- примет значение логического нуля.

Таблица истинности элемента НЕ представлена на рис, 12.3, б. Графическое изображение элемента (рис. 12.3, в) снабжается символом 1, операция инверсии обозначается символом О. а инверсный выход — чертой над буквой У.

Рис. 12.3. Элемент НЕ:

а—схема элемента; б —таблица истинности; а—условное обозначение t

В цифровой технике наиболее широкое применение получили сочетания логических элементов И и НЕ и построенные из таких ячеек различные триггеры.

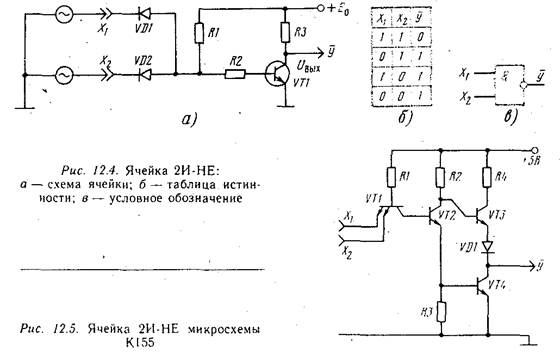

Логическая ячейка 2И—НЕ

На рис. 12.4 показаны схема ячейки 2И—НЕ, ее таблица истинности и графическое изображение. Логика ячейки 2И—НЕ инверсна логике элемента 2И, т. е. на выходе У будет сигнал логического нуля тогда и только тогда, когда на оба входа, XI и Х2, одновременно поданы сигналы логической единицы; если имеется 0 хотя бы на одном входе, то на выходе будет 1.

На рис. 12.5 показана упрощенная схема ячейки 2И—НЕ логических микросхем серии К155. У этих микросхем логическому нулю соответствует напряжение сигнала менее 0,4 В, а логической еди-

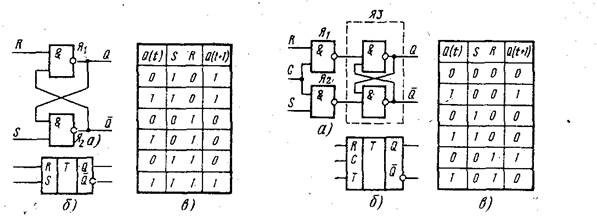

Рис. 12.6. Асинхронный RS-триггер: Рис. 12.7. Синхронный RS-триггер:

а— структурная схема; б—условное а —структурная схема; б—условное обозначение обозначение; в —таблица переходов в — таблица переходов

нижнем входе ячейки Я 1—нуль. Если на входы S и R подать комбинацию 1—0, то на обоих входах ячейки Яз будут единицы, что для схемы 2И—НЕ соответствует нулю на выходе Q. а на обоих входах ячейки Я> будут нули, что соответствует единице на выходе Q. Таким образом, триггер установился в состояние 1 (в данном случае не изменит своего состояния).

В такое же состояние установится триггер после подачи на входы S и R комбинации 1—0, если до этого триггер находился в состоянии 0. В этом случае на одном входе R ячейки Я будет 0, а на другом—1-й, следовательно, на выходе Q установится 1, которая поступит на верхний по схеме вход ячейки Яз. Теперь на обоих входах ячейки Я2 окажутся сигналы 1, а значит, на выходе j Q установится 0. Аналогично легко можно проанализировать работу триггера при подаче на входы S и R комбинаций 0—1 и 1—1. Результаты такого анализа сведены в таблицу переходов, приведенную на рис. 12.6, в. В этой таблице символом Q(7) обозначено состояние до, а символом Q [t--\- 1) после подачи сигналов на входы S и R. В таблице отсутствует комбинация 0—0 на входах S и R, так как при этом на обоих выходах Q и Q устанавливается 1, что противоречит принципу работы триггера. Следовательно, подача одновременно на входы S и R нулевых уровней сигналов недопустима.

Синхронный RS-триггер

Если асинхронный триггер дополнить схемой управления, состоящей из двух ячеек 2И — НЕ, то получится синхронный В триггер, структурная схема которого показана на рис. 12.7, а. У этого триггepa S и R, по-прежнему установочные входы, а вход С называется тактовым (или счетным). Импульсные сигналы, подаваемые на вход С, называются синхронизирующими. Пока сигнал на входе С отсутствует (т.е. имеет значение 0). допустимы любые комбинации сигналов на входах S и R —они не смогут воздействовать на триггер, так как на нижнем по схеме входе ячейки Я1 и верхнем входе ячейки Я2 будут нули, а поэтому на выходах ячеек 2И—НЕ будут единицы, независимо от уровней сигналов на их вторых входах (R и S). Подача же комбинации 1—1 на входы триггерной ячейки Яз не изменит ее состояния (см. таблицу переходов на рис. 12.6. в).

С момента поступления синхронизирующего сигнала (т. е. единичного уровня) на вход С уровни сигналов на входах S и R могут воздействовать на триггер. Поэтому во время действия синхронизирующего сигнала изменение уровней на входах S и R недопустимо.

На рис. 12.7, в показана таблица переходов синхронного RS-триггера для моментов подачи синхронизирующих сигналов (на входе С—уровень 1). Из таблицы видно, что при комбинации 0—0 на входах S и R подача синхронизирующего сигнала не изменяет состояния триггера; при комбинации 1—0 подача синхронизирующего сигнала переводит триггер в состояние 0; при комбинации 0—1 подача каждого синхронизирующего сигнала изменяет состояние триггера на обратное. Последний режим работы триггера называется счетным. Подача на входы S и R комбинации 1—1 недопустима, так как в этом случае поступление синхронизирующего сигнала вызовет появление на выходах ячеек Я1 и Яг комбинации О—О, недопустимой для триггерной ячейки Яз.

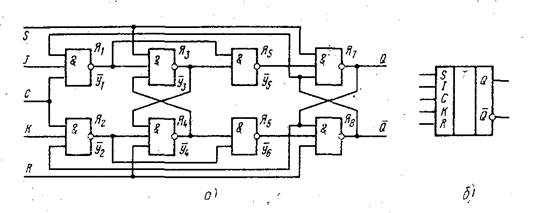

Сложные триггеры

На базе RS-триггеров строятся триггеры с более сложной логической структурой. На рис. 12.8 показаны структурная схема и графическое изображение JK-триггера, состоящего из двух RS-триггеров и имеющего кроме тактового входа С, установочных входов S и R также два информационных (логических) входа, J и К (таких объединенных логикой И входов может быть несколько). На установочные входы постоянно подаются единичные уровни. Если же необходимо установить триггер в состояние 0 или 1, то следует подать 0 в первом случае на вход R, во втором — на вход S. Обе триггерные ступени (Яз, Я4 и Я;, Яв) при этом одновременно принимают одинаковое состояние. Указанная операция, естественно, должна, выполняться при отсутствии синхронизирующего сигнала на тактовом входе С. После выполнения операции необходимо на входах S и R восстановить единичные уровни. Сигналы, поданные на логические входы J и К, управляют триггером только в моменты действия на входе С синхронизирующих сигналов. Если эти сигналы отсутствуют, т. е. на входе С—0, то на выходах ячеек 3И—НЕ, Я1 и Я2, независимо от уровней сигналов на их других входах, будет комбинация 1—1, которая не оказывает влияния на состояние первой, а следовательно, и второй триггерных ступеней. Сигналы на логических входах J и К следующим образом воздействуют на состояние JK-триггера: комбинация О—О не изменяет состояния триггера; комбинация I—0 переводит триггер в состояние 1; комбинация 0—1 переводит триггер в состояние 0; комбинация 1—1 с приходом каждого синхронизирующего сигнала (импульса) изменяет состояние триггера на обратное, т. е. триггер работает в счетном режиме.

Рис. 12.8. JK-триггер:

а — структурная схема, б — условное обозначение

Следует заметить, что любое состояние триггера устанавливается не в момент начала, а после прекращения действия синхронизирующего импульса: изменение уровня этого импульса с 0 на 1 приводит к срабатыванию первой триггерной ступени (Яз, Я4), а затем, когда значение импульса изменяется с 1 на 0, состояние первой ступени копирует вторая (выходная) триггерная ступень.

На рис. 12.9 приведена временная диаграмма работы JK-триггера в счетном режиме (на входах S, R, J, К — единичные уровни) при нулевом начальном состоянии (на выходе Q—0).

Кроме JK-триггеров наиболее часто применяются еще так называемые D-триггеры и Т-триггеры, графические изображения которых приведены на рис. 12.10.

D'-триггер имеет один логический вход D, состояние которого с каждым синхронизирующим импульсом передается на выход, т. е. сигнал на прямом выходе Q представляет собой задержанный на время действия синхронизирующего импульса (на один такт) входной сигнал. Для перевода D-триггера в счетный режим достаточно соединить его инверсный выход Q с логическим входом D (на рис. 12.10 показано штриховой линией).

Т-триггер также имеет один логический вход Т. Если на этот вход подана 1, то триггер работает в счетном режиме г ш подан 0, то синхронизирующие импульсы не изменяют состояния триггера.

Из трех рассмотренных триггеров со сложной логической структурой. JK-триггер является универсальным, так как, выполнив показанные на рис. 12.11 соединения, из него легко можно получить и D-триггер, и Т-триггер.

Следует заметить, что в JK-. D-, Т-триггерах установочные входы S и R могут отсутствовать.

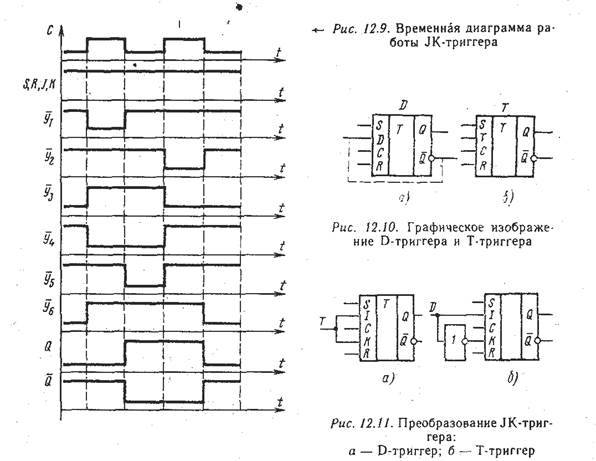

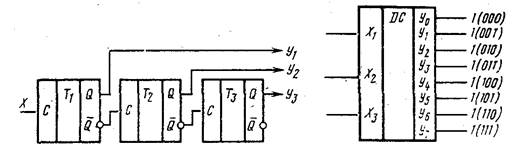

Суммирующий счетчик импульсов и дешифратор

На рис. 12.12 показан так называемый трехразрядный суммирующий счетчик импульсов, построенный на трех соединенных последовательно и работающих в счетных режимах триггерах, Т1, T2, Т3. Пусть, исходное состояние всех триггеров 0, т. е. на их прямых выходах Q нули, а на инверсных Q единицы. Этому состоянию счетчика соответствует двоичный код 000 на выходах Уз, У2, у1 (состояние счетчика принято записывать, начиная с состояния последнего триггера). При поступлении на вход Х первого импульса состояние триггера Ti изменится с 0 на 1, и на его инверсном выходе появится 0, который не изменит состояния триггера Тг, а следовательно, и Тз. На выходах счетчика установится двоичный код 001. При поступлении на вход Х второго импульса состояние триггера Т1 изменится с 1 на 0, появившаяся на его инверсном выходе 1 изменит состояние триггера Т2 с 0 на 1, а состояние триггера Т3 не изменится, так как на инверсном выходе триггера T2 будет 0. В результате на выходах счетчика установится двоичный код 010.

Рис. 12.12. Трехразрядный суммирующий Счетчик импульсов

Рис. 12.13. Графическое

изображение дешифратора

Легко убедиться, что третьему импульсу будет соответствовать двоичный код 011, четвертому—100 пятому—101. шестому— 110, седьмому— 111, и только при поступлении на вход Х восьмого импульса счетчик возвратится в исходное состояние 000.

Если счетчик дополнить дешифратором — электронным устройством, у которого каждая двоичная кодовая комбинация на входах вызывает появление сигнала только на одном из выходов,— то можно осуществлять логическое управление подключенными к выводам этого дешифратора электронными устройствами. Для работы с трехразрядным счетчиком требуется дешифратор, имеющий три входа и восемь выходов. Графическое изображение такого дешифратора показано на рис. 12.13. Против каждого выхода проставлен уровень 1, который появляется только при двоичном кодовом сочетании на входах Х3, Х2, X1, указанном в скобках; при других кодовых сочетаниях на этом выходе будет 0.

Сочетание трехразрядного счетчика с дешифратором применяется, например, в блоках сенсорного выбора программ (СВП-4) телевизионных приемников. Счетчик построен на микросхемах К 155 ТВ-1 (JK-триггер) и К 155 'ТМ2 (два D-триггера), а в качестве дешифратора использована микросхема К 155 ИД-1.