Отрицательные числа в прямом, обратном и дополнительном кодах имеют разное изображение.

Значащие разряды αn –1÷ αm отрицательного числа N кодируют:

• в прямом коде – модуль количественного эквивалента | N |;

• в обратном коде – дополнение модуля количественного эквивалента до веса знакового разряда, уменьшенного на вес младшего разряда, т.е. величину (qn – qm)–| N |;

• в дополнительном коде – дополнение модуля количественного эквивалента до веса знакового разряда qn, т.е. величину qn –| N |.

Например, число –137 в десятичной q = 10 и в двоичной q = 2 системах счислениях в разных кодах записывают так:

1|137пр 1|862обр 1|863доп

1|10001001пр 1|01110110обр 1|01110111доп

9. Конвейер команд.

Конве́йер — способ организации вычислений, используемый в современных процессорах и контроллерах с целью повышения их производительности (увеличения числа инструкций, выполняемых в единицу времени — эксплуатация параллелизма на уровне инструкций), технология, используемая при разработке компьютеров и других цифровых электронных устройств.

Идея заключается в параллельном выполнении нескольких инструкций процессора. Сложные инструкции процессора представляются в виде последовательности более простых стадий. Вместо выполнения инструкций последовательно (ожидания завершения конца одной инструкции и перехода к следующей), следующая инструкция может выполняться через несколько стадий выполнения после первой инструкции. Это позволяет управляющим цепям процессора получать инструкции со скоростью самой медленной стадии обработки, однако при этом намного быстрее, чем при выполнении эксклюзивной полной обработки каждой инструкции от начала до конца.

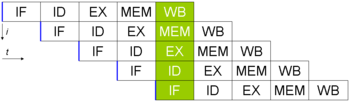

На иллюстрации справа показан простой пятиуровневый конвейер в RISC-процессорах. Здесь:

- IF (англ. Instruction Fetch) — получение инструкции,

- ID (англ. Instruction Decode) — раскодирование инструкции,

- EX (англ. Execute) — выполнение,

- MEM (англ. Memory access) — доступ к памяти,

- WB (англ. Register write back) — запись в регистр.

Вертикальная ось — последовательные независимые инструкции, горизонтальная — время. Зелёная колонка описывает состояние процессора в один момент времени, в ней самая ранняя, верхняя инструкция уже находится в состоянии записи в регистр, а самая последняя, нижняя инструкция — только в процессе чтения.

10. Организация памяти в ЭВМ. Иерархия по критерию быстродействия. Характеристика видов памяти (регистры, КЭШ, ОП, НЖМД). Адресация. Бит, байт.

Память – один из блоков ЭВМ, состоящий из запоминающих устройств (ЗУ) и предназначенный для запоминания, хранения и выдачи информации (алгоритма обработки данных и самих данных).

Основными характеристиками отдельных ЗУ являются емкость памяти, быстродействие и стоимость хранения единицы информации (бита).

Быстродействие (задержка) памяти определяется временем доступа и длительностью цикла памяти. Время доступа представляет собой промежуток времени между выдачей запроса на чтение и моментом поступления запрошенного слова из памяти. Длительность цикла памяти определяется минимальным временем между двумя последовательными обращениями к памяти.

Требования к увеличению емкости и быстродействия памяти, а также к снижению ее стоимости являются противоречивыми.Чем больше быстродействие, тем технически труднее достигается и дороже обходится увеличение емкости памяти.

Как и большинство устройств ЭВМ, память имеет иерархическую структуру. Обобщённая модель такой структуры, отражающая многообразие ЗУ и их взаимодействие, представлена на рис. 36. Все запоминающие устройства обладают различным быстродействием и емкостью. Чем выше уровень иерархии, тем выше быстродействие соответствующей памяти, но меньше её емкость.

К самому высокому уровню - сверхоперативному - относятся регистры управляющих и операционных блоков процессора, сверхоперативная память, управляющая память, буферная память (кэш-память).

На втором оперативном уровне находится оперативная память (ОП), служащая для хранения активных программ и данных, то есть тех программ и данных, с которыми работает ЭВМ.

На следующем более низком внешнем уровне размещается внешняя память.

https://ru.wikipedia.org/wiki/%D0%A0%D0%B5%D0%B3%D0%B8%D1%81%D1%82%D1%80_%D0%BF%D1%80%D0%BE%D1%86%D0%B5%D1%81%D1%81%D0%BE%D1%80%D0%B0

https://ru.wikipedia.org/wiki/%D0%9A%D1%8D%D1%88_%D0%BF%D1%80%D0%BE%D1%86%D0%B5%D1%81%D1%81%D0%BE%D1%80%D0%B0

https://ru.wikipedia.org/wiki/%D0%9E%D0%BF%D0%B5%D1%80%D0%B0%D1%82%D0%B8%D0%B2%D0%BD%D0%B0%D1%8F_%D0%BF%D0%B0%D0%BC%D1%8F%D1%82%D1%8C

11. Представление команды в ЭВМ. Формат (структура) машинной команды. Система команд ЭВМ, типы команд, режимы адресации.

Обработка информации в ЭВМ осуществляется путём программного управления.

Программа представляет собой алгоритм обработки информации, записанной в виде последовательности команд, которые должны быть выполнены машиной для получения результата.

Команда ЭВМ представляет собой код, определяющий операцию вычислительной машины и данные, участвующие в операции. В явной и неявной форме команда содержит также информацию об адресе, по которому помещается результат операции, и об адресе следующей команды.

По характеру выполняемых операций можно выделить следующие группы команд:

¨ команды арифметических операций для чисел с фиксированной или плавающей запятой;

¨ команды десятичной арифметики;

¨ команды передачи данных (MOV AX, 0FFFh);

¨ команды операций ввода/вывода (IN, OUT);

¨ команды логических операций (AND, OR, NOT);

¨ команды передачи управления (управление циклом – LOOP, условные переходы – JAE, JB);

¨ команды задания режима работы машины и др.

Форматы команд ЭВМ

В команде, как правило, содержатся не сами операнды, а информация объект адресах ячеек памяти или регистрах, в которых они находятся. Код команды можно представить состоящим из нескольких полей, каждое из которых имеет свое функциональное назначение.

В общем случае команда состоит из:

¨ операционной части (содержит код операции);

¨ адресной части (содержит адресную информацию о местонахождении обрабатываемых данных и месте хранения результатов).

В свою очередь, эти части, что особенно характерно для адресной части, могут состоять из нескольких полей.

Структура команды определяется составом, назначением и расположением полей в коде.

Форматом команды называется заранее оговоренная структура полей ее кода с разметкой номеров разрядов (бит), определяющих границы отдельных полей команды, или с указанием числа разрядов (бит) в определенных полях, позволяющая ЭВМ распознавать составные части кода.

Пример формата команды процессора i486.

mod r/m - спецификатор режима адресации;

r/m - регистр памяти;

SS - масштабный множитель для режима масштабирования индексной адресации;

КОП - код операции;

index - определяет индексный регистр;

base - определяет базовый регистр.

Важной и сложной проблемой при проектировании ЭВМ является выбор структуры и форматов команды, т.е. ее длины, назначения и размерности отдельных ее полей. Естественно стремление разместить в команде в возможно более полной форме информацию о предписываемой командой операции. Однако в условиях, когда в современных ЭВМ значительно возросло число выполняемых различных операций и соответственно команд (в компьютерах с CISC-архитектурой более 200 команд) и значительно увеличилась емкость адресуемой основной памяти (32, 64 Мб), это приводит к недопустимо большой длине формата команды.

Вместе с тем, для упрощения аппаратуры и повышения быстродействия ЭВМ длина формата команды должна быть по возможности короче, укладываться в машинное слово или полуслово. Решение проблемы выбора формата команды значительно усложняется в микропроцессорах, работающих с коротким словом.

Проследим изменения классических структур команд.

Чтобы команда содержала в явном виде всю необходимую информацию о задаваемой операции, она должна, как это показано на рис. 3.1 (б), содержать следующую информацию: А1, А2 - адреса операндов, А3 - адрес результата, А4 - адрес следующей команды (принудительная адресация команд).

Рис. 3.1. Структуры команд: а) обобщенная, б) четырехадресная, в) трехадресная, г) двухадресная, д) одноадресная, е)безадресная

Рис. 3.1. Структуры команд: а) обобщенная, б) четырехадресная, в) трехадресная, г) двухадресная, д) одноадресная, е)безадресная

Такая структура приводит к большей длине команды и неприемлема для прямой адресации операндов основной памяти. В компьютерах с RISC-архитектурой четырехадресные команды используются для адресации операндов, хранящихся в регистровой памяти процессора.

Можно установить, как это принято для большинства машин, что после выполнения данной команды, расположенной по адресу К (и занимающей L ячеек), выполняется команда из (K+L)-ой ячейки. Такой порядок выборки команды называется естественным. Он нарушается только специальными командами (передачи управления). В таком случае отпадает необходимость указывать в команде в явном виде адрес следующей команды.

В трехадресной команде (рис. 3.1, в) первый и второй адреса указывают ячейки памяти, в которых расположены операнды, а третий определяет ячейку, в которую помещается результат операции.

Можно условиться, что результат операции всегда помещается на место одного из операндов, например первого. Получим двухадресную команду (рис. 3.1, г), т.е. для результата используется подразумеваемый адрес.

В одноадресной команде (рис. 3.1, д) подразумеваемые адреса имеют уже и результат операции и один из операндов. Один из операндов указывается адресом в команде, в качестве второго используется содержимое регистра процессора, называемого в этом случае регистром результата или аккумулятором. Результат операции записывается в тот же регистр.

Наконец, в некоторых случаях возможно использование безадресных команд (рис. 3.1, е), когда подразумеваются адреса обоих операндов и результата операции, например, при работе со стековой памятью.

С точки зрения программиста, наиболее естественны и удобны трехадресные команды. Обычно в ЭВМ используется несколько структур и форматов команд разной длины. Приведенные на рис. 3.1. структуры команд достаточно схематичны. В действительности адресные поля команд большей частью содержат не сами адреса, а только информацию, позволяющую определить действительные (исполнительные) адреса операндов в соответствии с используемыми в командах способами адресации.

Способы адресации

Существует два различных принципа поиска операндов в памяти: ассоциативный и адресный.

Ассоциативный поиск операнда (поиск по содержанию ячейки) предполагает просмотр содержимого всех ячеек памяти для выявления кодов, содержащих заданный командой ассоциативный признак. Эти коды и выбираются из памяти в качестве искомых операндов.

Адресный поиск предполагает, что искомый операнд извлекается из ячейки, номер которой формируется на основе информации в адресном поле команды. Ниже мы будем рассматривать только реализацию адресного принципа поиска операнда.

Следует различать понятия исполнительного адреса и адресного кода.

Адресный код – это информация об адресе операнда, содержащегося в команде.

Исполнительный адрес – это номер ячейки памяти, к которой фактически производится обращение.

В современных ЭВМ адресный код, как правило, не совпадает с исполнительным адресом. Таким образом, способ адресации можно определить как способ формирования исполнительного адреса операнда Аи по адресному коду команды Ак.

В системах команд современных ЭВМ часто предусматривается возможность использования нескольких способов адресации операндов для одной и той же операции. Для указания способа адресации в некоторых системах команд выделяется специальное поле в команде - «метод» (указатель адресации). В этом случае любая операция может выполняться с любым способом адресации, что значительно упрощает программирование.

Адресуемые в командах операнды хранятся в основной памяти (ОП) и регистровой памяти (РП), рисунок 3.2.

|

По наличию адресной информации в команде различают явную и неявную адресацию.

При явной адресации операнда в команде есть поле адреса этого операнда, в котором задается адресный код Ак. Большинство методов адресации являются явными.

При неявной адресации адресное поле в команде отсутствует, адрес операнда подразумевается кодом операции.

Метод неявной адресации операндов используется во всех процессорах. Основное его назначение - уменьшение длины команды за счет исключения части адресов. При этом методе код операции точно задает адрес операнда. Например, из команды исключается адрес приемника результата. При этом подразумевается, что результат в этой команде помещается на место второго операнда.

12. Логические операции процессора.

Аппаратура современных ЭВМ, если не учитывать оперативную память, конструируется из некоторых относительно простых элементов, называемых в русскоязычной литературе вентилями (по-английски – circuits). Каждый вентиль является достаточно простой (электронной) схемой и реализует одну из логических операций, у него есть один или два входа (аргументы операции) и один выход (результат). На входах и выходе могут быть электрические сигналы двух видов: низкое напряжение (трактуется как ноль или логическое значение false) и высокое (ему соответствует единица или логическое значение true). Обычно напряжение менее 1 вольта трактуется как логический ноль, а напряжение более 2 вольт – как логическая единица. Основные вентили у нас будут следующие:

1. Отрицание, этот вентиль имеет один вход и один выход, он реализует операцию отрицания not (НЕ). Другими словами, если на вход такого вентиля подаётся импульс высокого напряжения (значение true), то на выходе получится низкое напряжение (значение false) и наоборот.

2. Дизъюнкция или логическое сложение, этот вентиль реализует операцию or (ИЛИ).

3. Конъюнкция или логическое умножение, этот вентиль реализует операцию and (И).

Вентиль – это устройство, которое выдает результат логической (булевой) операции над битами.

Любую логическую функцию можно преобразовать к эквивалентному виду, в котором используются только три перечисленные выше логические операции. Говорят, что функция имеет нормальную форму, если в ней отсутствуют знаки эквивалентности, импликации, двойного отрицания, при этом знаки отрицания находятся только при переменных.