Аппаратные средства вычислительной техники

Тема 2. Центральные устройства и узлы ЭВМ

ЛР 4

Исследование структуры микропроцессора

Задание: Научиться разбирать и собирать системный блок, находить устройства и функциональные узлы ПЭВМ Усвоить структурную схему микропроцессора и алгоритм взаимодействия МП с функциональными узлами ПЭВМ.

1. Устройства и функциональные узлы ПЭВМ. ЭВМ представляет собой совокупность устройств, выполненных на больших интегральных схемах, каждая из которых имеет свое функциональное назначение. Комплект интегральных схем, из которых состоит ЭВМ, называется микропроцессорным комплектом. В состав микропроцессорных комплектов входят: системный таймер, микропроцессор (МП), сопроцессоры, контроллер прерываний, контроллер прямого доступа к памяти, контроллеры устройств ввода-вывода.

Все устройства ЭВМ делятся на центральные и периферийные. Центральные устройства - полностью электронные, периферийные устройства могут быть либо электронными, либо электромеханическими с электронным управлением.

В центральных устройствах основным узлом, связывающим микропроцессорный комплект в единое целое, является системная магистраль. Она состоит из четырех узлов, называемых шинами: шина данных (ШД), шина адреса (ША), шина управления (ШУ) и шина питания (ШП). В состав системной магистрали входят регистры-защелки, в которых запоминается передаваемая информация, шинные формирователи, шинные арбитры, определяющие очередность доступа к системной магистрали, и др.

Логика работы системной магистрали, количество разрядов (линий) в шинах данных, адреса и управления, порядок разрешения конфликтных ситуаций, возникающих при одновременном обращении различных устройств ЭВМ к системной магистрали, образуют интерфейс системной шины.

В состав центральных устройств ЭВМ входят: центральный процессор, основная память и ряд дополнительных узлов, выполняющих служебные функции: контроллер прерываний, таймер и контроллер прямого доступа к памяти (ПДП).

Периферийные устройства делятся на два вида: внешние ЗУ (НМД, НГМД, НМЛ) и устройства ввода-вывода (УВВ): клавиатура, дисплей, принтер, мышь, адаптер каналов связи (КС) и др.

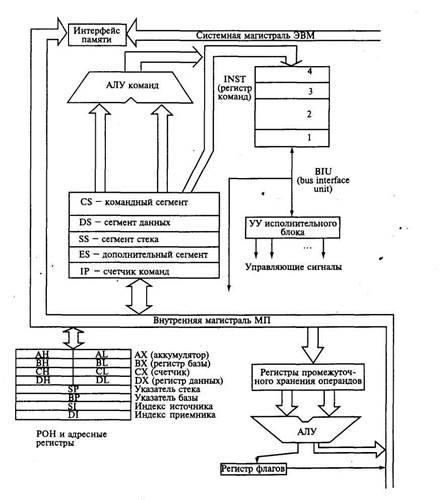

Структурная схема микропроцессора

Поскольку огромный объем программного обеспечения разработан для системы команд базового микропроцессора фирмы Iп (i8086), все последующие разработки этой фирмы, и фирм, выпускающих клоны, обеспечивают совместимость с базовой моделью.

Структурная схема базовой модели МП фирмы Intel приведена на рис.

Условно микропроцессор можно разделить на две части:

- исполнительный блок (Ехесution Unit)

- устройство сопряжения с системной магистралью (Bas Interface Unit)

В исполнительном блоке находится

- арифметический блок

- регистры общего назначения (РОН).

Арифметический блок включает

- арифметико-логическое устройство,

- вспомогательные регистры для хранения операндов

- регистры флагов.

Восемь регистров исполнительного блока МП (АХ, ВХ, СХ, DХ, SР, ВР, SI, DI), имеющих длину, равную машинному слову, делятся на две группы.

Первую группу составляют регистры общего назначения - АХ, ВХ, СХ, DХ, каждый из которых представляет собой регистровую пару, составленную из двух регистров длиной 0,5 машинного слова:

· Аккумулятор, или регистр АХ состоит из регистров АН и АL.

· Регистр базы (Вase Register) ВХ состоит из регистров ВН и ВL.

· Счетчик (Соunt Register) СХ включает регистры СН и СL.

· Регистр данных (Date Register) DХ содержит регистры DH, DL.

Каждый из коротких регистров может использоваться самостоятельно или в составе регистровой пары. Условные названия (аккумулятор, регистр базы, счетчик, регистр данных) не ограничивают применения этих регистров - эти названия говорят о наиболее частом использовании их или об особенности использования того или иного регистра в той или иной команде.

Вторую группу составляют адресные регистры: SP, BP, SI, DI (в старших моделях количество адресных регистров увеличено) Эти регисты активно используются по функциональному назначению и в других целях их применять не рекомендуется. В качестве адресного регистра часто используется РОН ВХ. Программно допускается использование регистров ВР, DI, SI в качестве регистров для хранения операндов, но отдельные байты в этих регистрах недоступны.

Основное их назначение - хранить числовые значения, реализуемые при формировании адресов операндов.

Устройство сопряжения с системной магистралью содержит

- управляющие регистры,

- конвейер команд,

- АЛУ команд,

- устройство управления исполнительным блоком МП

- интерфейс памяти (соединяющий внутреннюю магистраль МП с системной магистралью ПЭВМ).

Управляющие регистры BIU:

CS(указатель командного сегмента),

DS(указатель сегмента данных),

SS(указатель сегмента стека),

ES (указатель дополнительного сегмента) и др. — служат для определения физических адресов ОП - операндов и команд. Регистр IP(Instruction Pointer) является указателем адреса команды, которая будет выбираться в конвейер команд в качестве очередной команды (в отечественной литературе такое устройство называется счетчик команд). Конвейер команд МП хранит несколько команд, что позволяет при выполнении линейных программ совместить подготовку очередной команды с выполнением текущей.

К управляющим регистрам МП относится и регистр флагов, каждый разряд которого имеет строго определенное назначение. Обычно разряды регистра флагов устанавливаются аппаратно при выполнении очередной операции в зависимости от получаемого в АЛУ результата. При этом фиксируются такие свойства получаемого результата как

· нулевой результат,

· отрицательное число,

· переполнение разрядной сетки АЛУ и т.д.

Но некоторые разряды регистра флагов могут устанавливаться по специальным командам. Некоторые разряды имеют чисто служебное назначение (например, хранят разряд, «выпавший» из АЛУ во время сдвига) или являются резервными (т.е.не используются).

Все флаги младшего байта регистра устанавливаются арифметическими или логическими операциями. Все флаги старших байтов, за исключением флага переполнения, устанавливаются программным путем. для этого в МП имеются команды установки флагов (STD, STI, STC), сброса (CLC, CLD, CLI), инвертирования (СМС).