Цель работы: Изучение вопросов, касающихся синтеза и принципа действия триггеров различных типов: асинхронных, синхронных, «мастер-помощник», с установочными входами. Изучение основных схем включения триггеров.

Контрольные вопросы

1. Что такое триггер? Какие входы и выходы имеет триггер?

Триггером называется устройство, имеющее два устойчивых состояния («0» или «1») и способное под действием входного сигнала скачком переходить из одного устойчивого состояния в другое.

Триггер – это простейший автомат с памятью и способностью хранить 1 бит информации («0» или «1»).

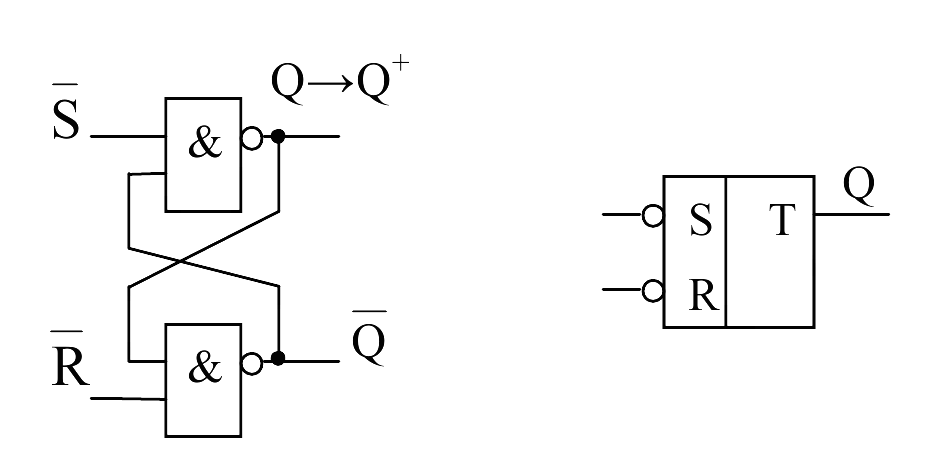

Триггеры имеют два выхода: прямой (Q) и инверсный ( ), рисунки 4.1 – 4.3. Если триггер находится в состоянии «1», то на выходе Q будет сигнал «1», а на выходе

), рисунки 4.1 – 4.3. Если триггер находится в состоянии «1», то на выходе Q будет сигнал «1», а на выходе  будет сигнал «0». Если триггер находится в состоянии «0», то его выход Q равен «0», а выход

будет сигнал «0». Если триггер находится в состоянии «0», то его выход Q равен «0», а выход  равен «1».

равен «1».

| Рисунок 4.1 – Асинхронный триггер | Рисунок 4.2 – Синхронный триггер со статическим управлением | Рисунок 4.3 – Синхронный триггер с динамическим управлением |

2. Какие бывают триггеры по способу записи?

По способу записи информации триггеры делятся на асинхронные и синхронные.

У асинхронных триггеров запись информации происходит под действием информационных сигналов. Такие триггеры имеют только информационные входы. Условно-графическое обозначение (УГО) такого триггера представлено на рисунке 4.1.

У синхронных триггеров запись информации происходит под действием разрешающих сигналов синхронизации.

Синхронные триггеры бывают со статическим, динамическим управлением записью и двухступенчатые.

Синхронные триггеры со статическим управлением записью принимают информационные сигналы все время, пока действует импульс синхронизации, рисунок 4.2. Следовательно, переключение триггера за время действия импульса синхронизации может быть многократным. У таких триггеров вход С – статический.

|

|

3. Какие параметры триггера Вы знаете?

Для всех триггеров характерны следующие параметры:

Краз – коэффициент разветвления. Показывает нагрузочную способность триггера, т.е. обозначает количество элементов, которые параллельно присоединены к выходу триггера и на которые подается выходной сигнал триггера.

Коб – коэффициент объединения по входу. Обозначает максимальное число входных сигналов, которые можно подать на вход триггера.

tи – наименьшая длительность входного сигнала (импульса), при котором еще происходит надежное переключение триггера.

tзд – время задержки между моментом подачи входного сигнала и появлением выходного сигнала.

tр – время разрешения, которое характеризует наименьший интервал между моментами подачи двух входных сигналов с длительностью tи, вызывающих переключение триггера

4. Нарисуйте УГО и таблицу истинности  - триггера. Какая комбинация сигналов является запрещенной?

- триггера. Какая комбинация сигналов является запрещенной?

Асинхронный  -триггер

-триггер

УГО асинхронного  триггера представлена на рисунке 4.4.

триггера представлена на рисунке 4.4.

| ||

Рисунок 4.4 –  -триггер -триггер

|

Запрещенной комбинацией будет являться комбинация входных сигналов  =

=  = 0.

= 0.

Работу асинхронного  -триггера можно описать таблицей истинности, таблица 4.1.

-триггера можно описать таблицей истинности, таблица 4.1.

Таблица 4.1 – Таблица истинности асинхронного RS-триггера

|

| Qt | Qt+1 | Примечание |

| Хранение «0» (сигналы на входах неактивны) | ||||

| Установка в состояние «0» (триггер находился в состоянии «0», устанавливается в состояние «0» по активному входу R = 1) | ||||

| Установка в состояние «1» (триггер находился в состоянии «0», устанавливается в состояние «1» по активному входу S = 1) | ||||

| - | Запрещенная комбинация | |||

| Хранение «1» (сигналы на входах неактивны) | ||||

| Установка в состояние «0» (триггер находился в состоянии «1», устанавливается в состояние «0» по активному входу R = 1) | ||||

| Установка в состояние «1» (триггер находился в состоянии «1», устанавливается в состояние «1» по активному входу S = 1) | ||||

| - | Запрещенная комбинация |

|

|

5. Нарисуйте УГО и таблицу истинности  - триггера.

- триггера.

УГО асинхронного  K-триггера, представлены на рисунке 4.5.

K-триггера, представлены на рисунке 4.5.

JK-триггер не имеет запрещенных комбинаций входных сигналов.

Если на входы J и K одновременно действуют активные сигналы «1», то триггер изменяет свое состояние на противоположное.

Такой режим работы называют счетным режимом.

Рисунок 4.5 – УГО асинхронного  K триггер K триггер

| ||

Вход J триггера (аналогично входу S) является входом установки триггера в единичное состояние по прямому выходу Q. Вход K триггера (аналогично входу R) является входом установки триггера в нулевое состояние по прямому выходу Q.

Работу асинхронного  K-триггера можно описать таблицей истинности, таблица 4.2.

K-триггера можно описать таблицей истинности, таблица 4.2.

Таблица 4.2 – Таблица истинности асинхронного  K-триггера

K-триггера

|

|

| K | Qt | Qt+1 | Примечание |

| Хранение «0» (сигналы на входах неактивны) | ||||

| Установка в состояние «0» (триггер находился в состоянии «0», устанавливается в состояние «0» по активному входу К = 1) | ||||

| Установка в состояние «1» (триггер находился в состоянии «0», устанавливается в состояние «1» по активному входу J = 1) | ||||

| Счетный режим, триггер переходит из состояния «0» в состояние «1» | ||||

| Хранение «1» (сигналы на входах неактивны) | ||||

| Установка в состояние «0» (триггер находился в состоянии «1», устанавливается в состояние «0» по активному входу К = 1) | ||||

| Установка в состояние «1» (триггер находился в состоянии «1», устанавливается в состояние «1» по активному входу J = 1) | ||||

| Счетный режим, триггер переходит из состояния «1» в «0» |

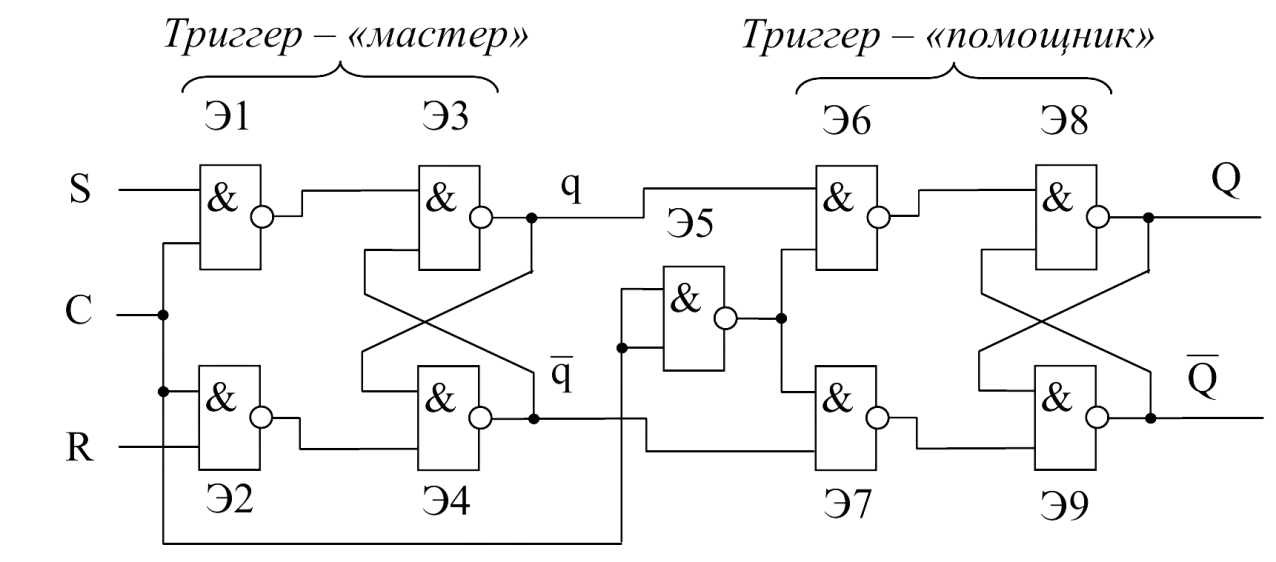

6. Какой триггер называется «мастер-помощник»? Нарисуйте его УГО.

Синхронный двухступенчатый RS-триггер (master-slave, что переводится «мастер-помощник») состоит из двух синхронных RS-триггеров и инвертора (рис. 4.6). Входы C обоих триггеров соединены между собой через инвертор Э5. Если каждый из триггеров имеет установку положительным перепадом, то входная RS-комбинация будет записана в первую ступень в момент прихода положительного перепада тактового импульса C, т.е. если C =1, то первый триггер функционирует согласно сигналам на его входах S и R. Второй триггер функционировать не может, так как у него C = 0. Когда придет отрицательный перепад тактового импульса C, на выходе инвертора Э5 он появится как положительный. Тогда первый триггер не функционирует, а для второго триггера C= 1, и данные от выходов первого триггера перепишутся в триггер второй ступени. Сигнал на выходе появится с задержкой, равной длительности тактового импульса.

а

б

Рис. 4.6 Синхронный двухступенчатый RS-триггер с инвертором- а)

и его УГО-б)

7. Какой триггер называется синхронным?

У синхронных триггеров запись информации происходит под действием разрешающих сигналов синхронизации.

Синхронные триггеры бывают со статическим, динамическим управлением записью и двухступенчатые.

Синхронные триггеры со статическим управлением записью принимают информационные сигналы все время, пока действует импульс синхронизации, рисунок 4.2. Следовательно, переключение триггера за время действия импульса синхронизации может быть многократным. У таких триггеров вход С – статический.

Синхронные триггеры с динамическим управлением записью принимают только те информационные сигналы, которые были на информационных входах к моменту прихода синхроимпульса.

8. Нарисуйте схему синхронного  - триггера на элементах ИЛИ-НЕ. Объясните его работу с помощью диаграммы.

- триггера на элементах ИЛИ-НЕ. Объясните его работу с помощью диаграммы.

Помимо борьбы с помехами режим синхронизации RS-триггеров широко используется при построении тактируемых цифровых устройств. Для обеспечения синхронизируемого режима работы обычные асинхронные RS-триггеры должны быть дополнены схемами синхронизации. На рис.4.7 показана реализация синхронных RS-триггеров соответственно в базисе логических элементов ИЛИ—НЕ. Схемы синхронизации построены на логических элементах DD1, DD2 и формируют сигналы R*, S*, управляющие состоянием асинхронных RS-триггеров на логических элементах DD3, DD4. Информация, поступающая на входы S и R, как видно из временных диаграмм, воспринимается только на интервале действия разрешающих синхроимпульсов С длительностью tс. В остальное время триггер находится в режиме хранения ранее записанной информации.

a б

Рис. 4.7— Синхронный RS-триггер на элементах ИЛИ—НЕ: а)функциональная схема; б) временные диаграммы работы

Все изменения информационных сигналов R и S в интервале tс передаются на вход асинхронного триггера на логических элементах DD3, DD4 и вызывают переключение его состояний (прозрачный режим асинхронной записи), что характерно для всех схем синхронизируемых уровнем. Запрещенной, аналогично асинхронным триггерам, является комбинация входных сигналов  =

=  =

=  =0, обусловливающая установку на прямом и инверсном выходах уровней Q=

=0, обусловливающая установку на прямом и инверсном выходах уровней Q=  =0 в триггере (рис 4.7,а),

=0 в триггере (рис 4.7,а),

9. Нарисуйте схему синхронного JK-триггера и его таблицу истинности.

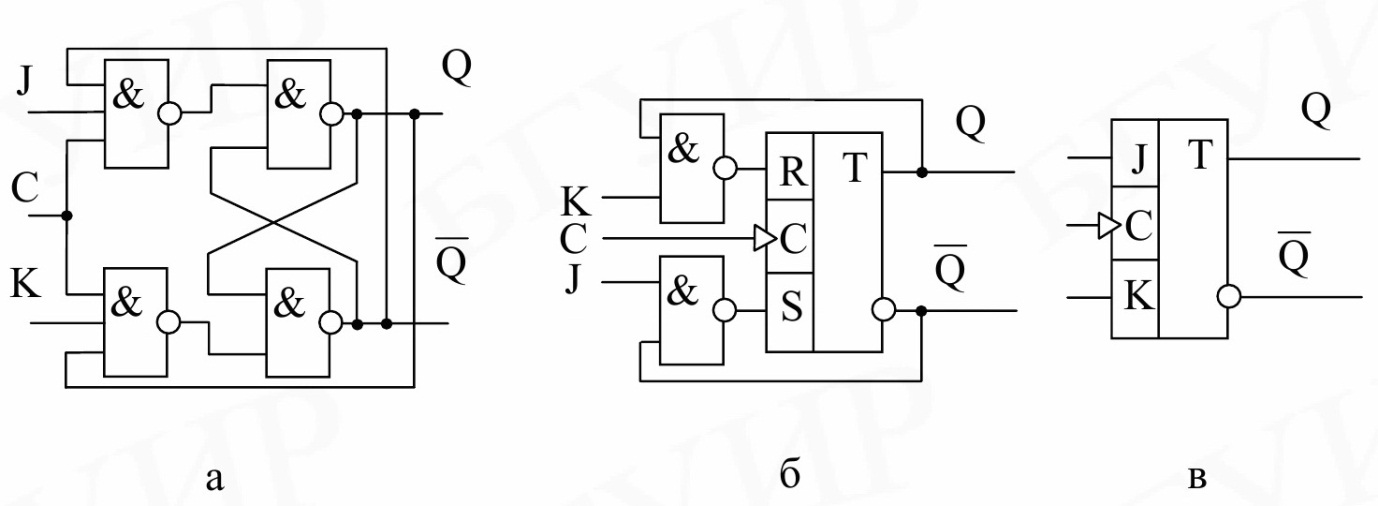

JK -триггер отличается от RS -триггера прежде всего тем, что в нем устранена неопределенность, которая возникает в RS -триггере при определенной комбинации входных сигналов.

Комбинированный JK -триггер отличается от универсального наличием дополнительных асинхронных входов S и R для предварительной установки триггера в определенное состояние (логической 1 или 0).

Риc. 4.8  Преобразование синхронного RS-триггера в JK-триггер

Преобразование синхронного RS-триггера в JK-триггер

Простейший JK -триггер можно получить из синхронного RS -триггера(рис. 4.8, а, б, в), если ввести дополнительные обратные связи с выходов триггера на входы, которые позволяют устранить неопределенность в таблице состояний. JK -триггер имеет следующую таблицу состояний (табл. 4.3).

Таблица 4.3  Состояния асинхронных JK-триггеров

Состояния асинхронных JK-триггеров

| Входы | Выходы | ||

| J | К | Qn+l |

|

| Qn |

| ||

| Qn |

При входных сигналах J = K = 0 состояние триггера не изменяется, так как напряжение низкого уровня на одном входе элемента И-НЕ отменяет прохождение сигналов от других его входов и удерживает выходной сигнал на высоком уровне. Если на входы J и K подать взаимно противоположные уровни, то при подаче перепада напряжения на вход C выходы JK -триггера устанавливаются в такие же состояния. При подаче на входы J и K одновременно напряжений высокого уровня триггер переключается в состояние, противоположное предыдущему, если на вход синхронизации C подать перепад напряжения.

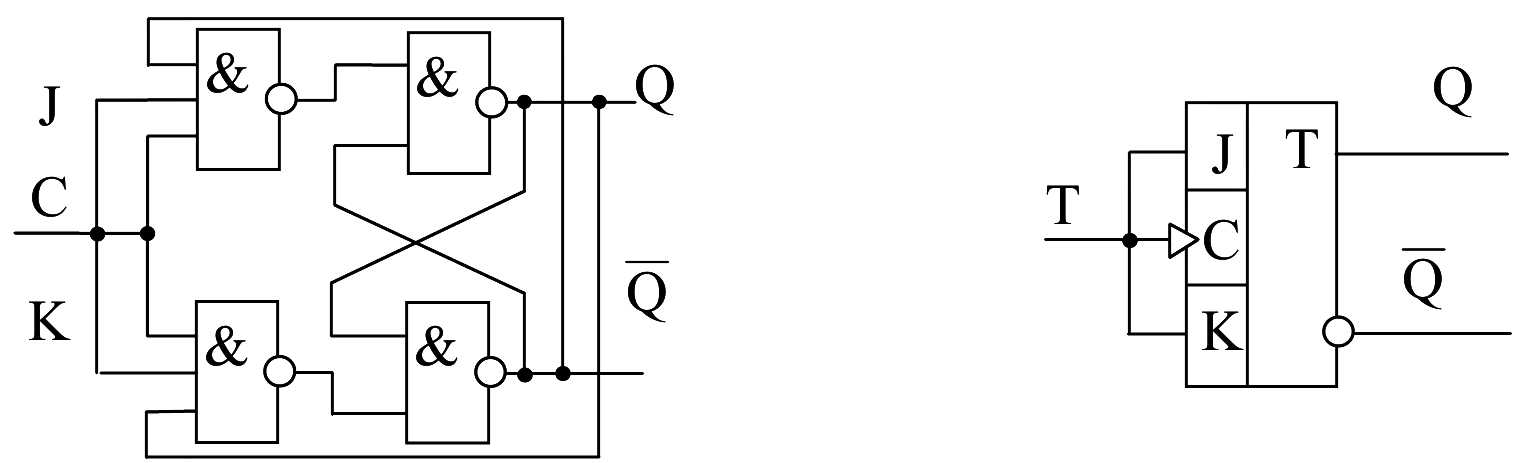

10.Нарисуйте схемы преобразования JK-триггера в триггер Т и триггер D.

Универсальность JK -триггера состоит в том, что он может выполнять функции RS-, Т- и D- триггеров.

Рис. 4.9  Преобразование JK-триггера в T-триггер

Преобразование JK-триггера в T-триггер

Из JK-триггера можно получить D-триггер, если вход K соединить со входом J через дополнительный инвертор

Рис. 4.10  Преобразование JK-триггера в D-триггер

Преобразование JK-триггера в D-триггер

Индивидуальное задание

В соответствии с вариантом, индивидуальных занятий, представленных в таблице 4.4 выполнить следующие действия:

Таблица 4.4 – Варианты индивидуального задания

| № варианта | Триггер | Базовый ЛЭ | Бистабильная ячейка |

| ИЛИ-НЕ | RS |

1. Составить таблицу переходов указанного триггера.

Таблица 4.5 – Таблица истинности  -триггера

-триггера

|

| Qt | Qt+1 |

2. Используя таблицу переходов, составить карту Карно и синтезировать логическое выражение, описывающее работу данного триггера.

Таблица 4.6

| ||

| 1 | 1 | |

| 1 | 0 | |

| 0 | 0 | |

| 0 | 1 |

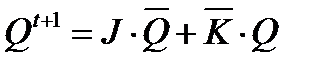

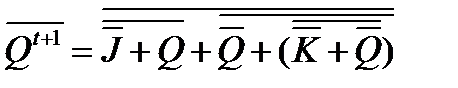

На основании данных табл. 4.5 составим карту Карно (табл. 4.6) и запишем логическое уравнение для J  -триггера:

-триггера:

3. Привести полученное выражение к базовому ЛЭ, указанному для данного варианта, с помощью алгебры логики, представив всю последовательность преобразований.

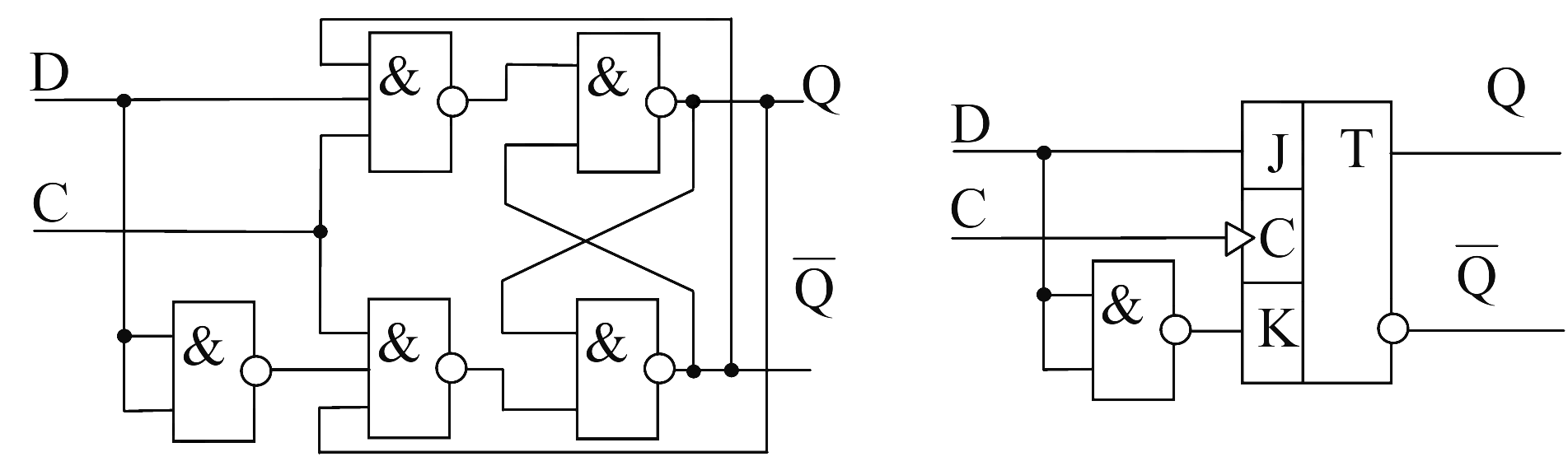

4. Нарисовать принципиальную схему триггера на базовых ЛЭ в соответствии с ЕСКД.

Рис. 4.10  Принципиальную схему триггера

Принципиальную схему триггера  в базисе 2ИЛИ-НЕ

в базисе 2ИЛИ-НЕ

5. Используя таблицу переходов триггера, проверить правильность синтезированной схемы. Для этого подать значения переменных на входы схемы и получить соответствующие значения сигнала на выходах триггера. Процедуру проверки представить в отчете.

Проверим правильность синтезированной схемы подавая следующие значения переменных на входы схемы (таблица 4.7).

Таблица 4.7 – Таблица истинности синхронного  -триггера

-триггера

| J |

| Qt | Qt+1 |

Рис. 4.11  Проверка правильности синтезированной схемы триггера

Проверка правильности синтезированной схемы триггера  в базисе 2ИЛИ-НЕ

в базисе 2ИЛИ-НЕ

6. Нарисовать схему триггера на основе бистабильной ячейки RS.

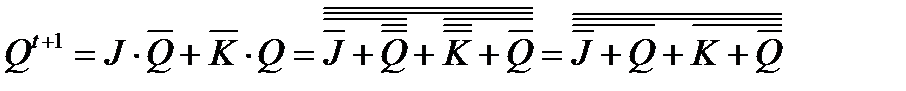

Преобразуем выражение  с целью реализации

с целью реализации  триггера на элементах ИЛИ-НЕ, введя дополнительный консенсусный член

триггера на элементах ИЛИ-НЕ, введя дополнительный консенсусный член  , численно равный нулю, тогда

, численно равный нулю, тогда

Поставим отрицание с двух сторон выражения:

Бистабильная ячейка, триггер - электронная схема, находящаяся в одном из двух устойчивых состояний (логическая 1 или логический 0), пока через один из своих входов не получит импульс, при помощи которого она переключается в другое состояние.

Рис. 4.11  Бистабильной ячейки

Бистабильной ячейки  .

.

Рис. 4.12−  триггер на основе бистабильной ячейки

триггер на основе бистабильной ячейки  .

.

7. Нарисовать временную диаграмму работы данного триггера, предусмотрев на ней максимально возможное количество комбинаций из таблицы переходов.

Рис. 4.13− Временные диаграммы работы триггера  .

.