Дешифраторы

Называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. Число входов и выходов в так называемом полном дешифраторе связано соотношением m= 2n, где n- число входов, а m— число выходов. Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет полным, а если бы выходов было только 10, то он являлся бы неполным.

Обратимся для примера к дешифратору К555ИД6 серии К555

Дешифратор имеет 4 прямых входа, обозначенных через А1, …, А8. Аббревиатура A обозначает «адрес» (от англ.address). Указанные входы называют адресными. Цифры определяют значения активного уровня (единицы) в соответствующем разряде двоичного числа. Дешифратор имеет 10 инверсных выходов Y0, …, Y9. Цифры определяют десятичное число, соответствующее заданному двоичному числу на входах. Очевидно, что этот дешифратор неполный.

Значение активного уровня (нуля) имеет тот выход, номер которого равен десятичному числу, определяемому двоичным числом на входе. Например, если на всех входах — логические нули, то на выходе Y0 — логический ноль, а на остальных выходах — логическая единица. Если на входе А2 — логическая единица, а на остальных входах — логический ноль, то на выходе Y2 — логический ноль, а на остальных выходах — логическая единица. Если на входе — двоичное число, превышающее 9 (например, на всех входах единицы, что соответствует двоичному числу 1111 и десятичному числу 15), то на всех выходах — логическая единица.

Дешифратор — одно из широко используемых логических устройств. Его применяют для построения различных комбинационных устройств.

Существует несколько разновидностей дешифраторов:

— прямоугольные;

— матричные;

— пирамидальные.

Матричные являются типовыми, наиболее простыми разновидностями дешифраторов, на их основе строятся различные более сложные схемы. В прямоугольных реализуется ступенчатая дешифрация. Входной сигнал условно разбивается на группы, каждая из которых обрабатывается отдельными матричными дешифраторами. На последующих ступенях дешифрации (второй, третьей и т.п.) формируется произведение полученных сигналов. Главным преимуществом пирамидальных дешифраторов считается простота наращивания числа входов, а недостатком – аппаратная неизбыточность.

4) Мультиплексором — называют комбинационное устройство, обеспечивающее передачу в желаемом порядке цифровой информации, поступающей по нескольким входам на один выход. Мультиплексоры обозначают через MUX (от англ. multiplexor), а также через MS (от англ. multiplex or selector).

Мультиплексор - это устройство, которое осуществляет выборку одного из нескольких входов и подключает его к своему единственному выходу, в зависимости от состояния двоичного кода. Другими словами, мультиплексор - переключатель сигналов, управляемый двоичным кодом и имеющий несколько входов и один выход. К выходу подключается тот вход, чей номер соответствует управляющему двоичному коду.

Ну и частное определение: мультиплексор - это устройство, преобразующее параллельный код в последовательный.

Схематически мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства. Кроме информационных входов в мультиплексоре имеются адресные входы и, как правило, разрешающие (стробирующие). Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если между числом информационных входов n и числом адресных входов m действует соотношение n = 2m, то такой мультиплексор называют полным. Если n< 2m, то мультиплексор называют неполным.

Разрешающие входы используют для расширения функциональных возможностей мультиплексора. Они используются для наращивания разрядности мультиплексора, синхронизации его работы с работой других узлов. Сигналы на разрешающих входах могут разрешать, а могут и запрещать подключение определенного входа к выходу, т. е. могут блокировать действие всего устройства.

Коммутаторы – это промышленные устройства, которые могут располагаться отдельно либо быть составной частью какой-нибудь электронной системы. Принцип работы коммутатора заключается в выборе нужной электрической цепи и подключения ее к входной цепи.

Принцип действия коммутатора такой же, что и у электронных, электромеханических, а также электронно-лучевых приборов. Назначение коммутатора состоит в том, чтобы управлять токами катушки зажигания, опираясь на сигналы синхронизационного датчика.

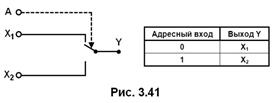

Рассмотрим функционирование двухвходового мультиплексора (2 →1), который условно изображен в виде коммутатора, а состояние его входов Х1Х2 и выхода Y приведено в таблице

Исходя из таблицы, можно записать следующее уравнение:

Y = X1A + X2A

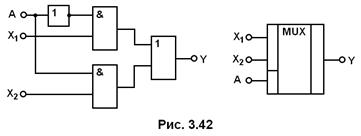

На рис. 3.42 показаны реализация такого устройства и его условное графическое обозначение.

Основой данной схемы являются две схемы совпадения на элементах И, которые при логическом уровне «1» на одном из своих входов повторяют на выходе то, что есть на другом входе.

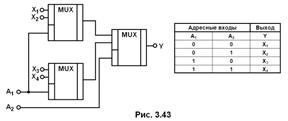

Если необходимо расширить число входов, то используют каскадное включение мультиплексоров. В качестве примера рассмотрим мультиплексор с четырьмя входами (4 → 1), построенный на основе мультиплексоров (2 → 1).

Схема и таблица состояний такого мультиплексора приведены на рис.3.43.

Мультиплексоры являются универсальными логическими устройствами, на основе которых создают различные комбинационные и последовательностные схемы. Мультиплексоры могут использоваться в делителях частоты, триггерных устройствах, сдвигающих устройствах и др. Мультиплексоры часто используют для преобразования параллельного двоичного кода в последовательный. Для такого преобразования достаточно подать на информационные входы мультиплексора параллельный двоичный код, а сигналы на адресные входы подавать в такой последовательности, чтобы к выходу поочередно подключались входы, начиная с первого и кончая последним.

Аналоговые и цифровые мультиплексоры значительно различаются по принципу работы. Первые электрически соединяют выбранный вход с выходом (при этом сопротивление между ними невелико — порядка единиц/десятков ом). Вторые же не образуют прямого электрического соединения между выбранным входом и выходом, а лишь «копируют» на выход логический уровень ('0' или '1') с выбранного входа. Аналоговые мультиплексоры иногда называют ключами или коммутаторами.

5) Демультиплексором называют устройство, в котором сигналы с одного информационного входа, поступают в желаемой последовательности по нескольким выходам в зависимости от кода на адресных шинах. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. Демультиплексоры обозначают через DMX или DMS.

Демультиплексор - устройство, обратное мультиплексору. Т. е., у демультиплексора один вход и много выходов. Двоичный код определяет, какой выход будет подключен ко входу.

демультиплексор - это устройство, которое осуществляет выборку одного из нескольких своих выходов и подключает его к своему входу или, ещё, это переключатель сигналов, управляемый двоичным кодом и имеющий один вход и несколько выходов.

Ко входу подключается тот выход, чей номер соответствует состоянию двоичного кода. демультиплексор - это устройство, которое преобразует последовательный код в параллельный.

Если соотношение между числом выходов n и числом адресных входов m определяется равенством n= 2m, то такой демультиплексор называется полным, при n< 2m демультиплексор является неполным.

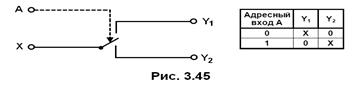

Рассмотрим функционирование демультиплексора с двумя выходами, который условно изображен в виде коммутатора, а состояние его входов и выходов приведено в таблице (рис. 3.45).

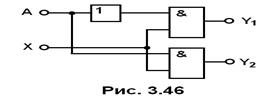

Из этой таблицы следует: Y1=X·А Y2 = X·А т. е. реализовать такое устройство можно так, как показано на рис. 3.46.

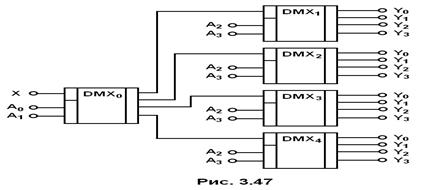

Для наращивания числа выходов демультиплексора используют каскадное включение демультиплексоров. В качестве примера (рис. 3.47) рассмотрим построение демультиплексоров с 16 выходами (1 → 16) на основе демультиплексоров с 4 выходами (1 → 4).

При наличии на адресных шинах А0 и А1 нулей информационный вход X подключен к верхнему выходу DМХ0 и в зависимости от состояния адресных шин А2 и А3 он может быть подключен к одному из выходов DMX1. Так, при А2 = А3 = 0 вход X подключен к Y0. При А0 = 1 и А1 = 0 вход X подключен к DMX2, в зависимости от состояния А2 и А3 вход соединяется с одним из выходов Y4 − Y7 и т.д.

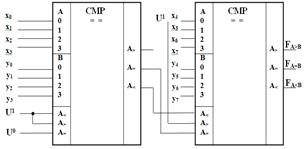

6) Цифровые компараторы выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных чисел A и B с одинаковым количеством разрядов либо вид неравенства A> B или A < B. Цифровые компараторы имеют три выхода.

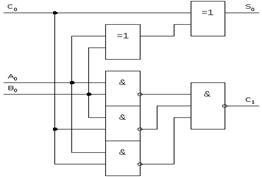

Схема одноразрядного компаратора представляет собой структуру логического элемента «исключающее ИЛИ-НЕ» (рис. 3.51).

Из анализа схемы следует, что если A= B, то F = 1, в противном случае, т. е. при А ≠ В, F = 0. Если А > В, т. е. А = 1, В = 0, то С = 1, а если А < В, т. е. А = 0, В = 1, то D = l.

Если попарно равны между собой все разряды двух n-разрядных двоичных чисел, то равны и эти два числа А и В. Применяя цифровой компаратор для каждого разряда, например, четырехзначных чисел, и определяя значения F1, F2, F3, F4 логических переменных на выходах компараторов, факт равенства А = В установим в случае, когда F = F1 · F2 · F3 · F4 = 1. Если же F = 0, то А ≠ В.

Неравенство А > В обеспечивается (для четырехразрядного числа) в четырех случаях: или А4 > В4, или А4 = В4 и А3 > В3, или А4 = В4, А3 = В3 и А2 > В2, или А4 = В4, А3 = В3, А2 = В2 и A1 > В1 (где А4 и В4 — старшие разряды чисел А и В). Очевидно, что если поменять местами А1 и B1, то будет выполняться неравенство А < В.

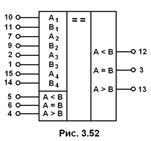

Цифровые компараторы выпускают, как правило, в виде самостоятельных микросхем. Так, микросхема К564ИП2 (рис. 3.52) является четырехразрядным компаратором, в котором каждый из одноразрядных компараторов аналогичен рассмотренной ранее схеме. Данная микросхема имеет расширяющие входы А < В, А = В, А > В, что позволяет наращивать разрядность обоих чисел. Для этого компараторы соединяют каскадно или параллельно (пирамидально).

Рассмотрим каскадное соединение компараторов К564ИП2 для сравнения двух восьмиразрядных чисел (рис. 3.53). При этом соединении выходы А = В и А < В предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы А < В, А = В, А > В микросхемы младших разрядов подают соответственно потенциалы U0 и U1 (U0 соответствует логическому 0, a U1 — «1»). В последующих микросхемах на входах А > В поддерживают потенциал логической единицы U1.

Рассмотрим каскадное соединение компараторов К564ИП2 для сравнения двух восьмиразрядных чисел (рис. 3.53). При этом соединении выходы А = В и А < В предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы А < В, А = В, А > В микросхемы младших разрядов подают соответственно потенциалы U0 и U1 (U0 соответствует логическому 0, a U1 — «1»). В последующих микросхемах на входах А > В поддерживают потенциал логической единицы U1.

Компара́тор аналоговых сигналов (от лат. comparare — сравнивать) — сравнивающее устройство[1]) — электронная схема, принимающая на свои входы два аналоговых сигнала и выдающая сигнал высокого уровня, если сигнал на неинвертирующем входе («+») больше, чем на инвертирующем (инверсном) входе («−»), и сигнал низкого уровня, если сигнал на неинвертирующем входе меньше, чем на инверсном входе. Значение выходного сигнала компаратора при равенстве входных напряжений, в общем случае не определено. Обычно в логических схемах сигналу высокого уровня приписывается значение логической 1, а низкому — логического 0.

Через компараторы осуществляется связь между непрерывными сигналами, например, напряжения и логическими переменными цифровых устройств.

Применяются в различных электронных устройствах, АЦП и ЦАП, устройствах сигнализации, допускового контроля и др.

Одно из напряжений (сигналов), подаваемое на один из входов компаратора обычно называют опорным или пороговым напряжением. Пороговое напряжение делит весь диапазон входных напряжений, подаваемых на другой вход компаратора на два поддиапазона. Состояние выхода компаратора, высокое или низкое, указывает, в каком из двух поддиапазонов находится входное напряжение. Компаратор с одним входным пороговым напряжением принято называть однопороговым компаратором, существуют компараторы с двумя или несколькими пороговыми напряжениями, которые, соответственно делят диапазон входного напряжения на число поддиапазонов на 1 большее числа порогов.

7) Сумматором называется узел ЭВМ, предназначенный для арифметического сложения кодов. Сумматоры в зависимости от используемых логических схем различаются на комбинационные и накапливающие. Комбинационный сумматор представляет собой комбинационную схему, которая формирует суммы слагаемых, подаваемых одновременно на входы схемы, и не имеет в своем составе элементов памяти. Накапливающие сумматоры имеют память, в которой накапливают результаты суммирования.

По числу входов различают полусумматоры, одно и многоразрядные (параллельные) сумматоры. В зависимости от того, как организованы межразрядные переносы, сумматоры делятся на сумматоры с последовательным, параллельным и групповыми переносами

В зависимости от того, как обрабатываются (суммируются) разряды n-разрядных чисел, различают многоразрядные сумматоры последовательного и параллельного действия.

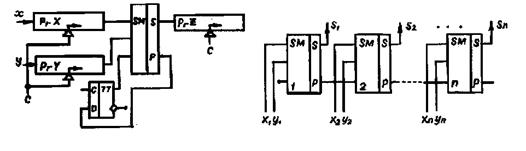

В последовательных сумматорах поразрядная обработка слагаемых производится последовательно. При этом разряды суммы запоминаются в регистре суммы, а перенос запоминается на один такт в дополнительном триггере. Перенос поступает на вход сумматора вместе со слагаемыми очередного разряда. Процесс продолжается до тех пор, пока полностью не сформируется результат. Структура многоразрядного сумматора последовательного действия показана на рис. 7.6. Сдвигающие регистры РгХ и PrY служат для хранения и сдвига операндов вправо. PrZ - для приема разрядов суммы с выхода одноразрядного сумматора. Поразрядное суммирование производится в сумматоре. Перенос из предыдущего разряда запоминается в D-триггере.

В многоразрядных сумматорах параллельного действия разряды слагаемых обрабатываются параллельно. Количество сумматоров в них соответствует разрядности обрабатываемых чисел. По способу реализации цепей переноса сумматоры параллельного действия могут иметь следующую организацию : сумматоры с последовательным, одновременным и групповым переносом.

В сумматорах с последовательным переносом перенос распространяется последовательно (рис. 7.7) Максимальное время распространения переноса составляет: tåmax=t1n, где t1- время распространения переноса в одном разряде; n - число разрядов сумматора.

В сумматорах параллельного действия с одновременным переносом сигнал переноса вырабатывается одновременно во всех разрядах. Рассмотрим синтез схем одновременного формирования переносов в 4-х разрядных сумматорах.

Полуссуматор

Сумматор

8) Процедура умножения двоичных кодов чисел достаточно часто встречается при цифровой обработке сигналов. Если рассматривать целые числа, то умножение можно представить как многократное сложение. К примеру, чтобы умножить 3 на 5, требуется тройку пять раз сложить с самой собой. Данным способом умножение можно выполнять, используя, в частности, накапливающие сумматоры. Однако время выполнения этой процедуры будет достаточно велико и, кроме того, оно окажется зависимым от величины множителя.

Другие подходы к реализации процедуры перемножения чисел требуют многократного последовательного выполнения операций сложения и сдвига. Их количество, а следовательно, скорость выполнения умножения, также зависят от разрядности множителя.

Разработка специальных алгоритмов умножения позволила создать так называемые параллельные или матричные умножители. Одна из их разновидностей называется множительным, а другая - множительно-суммирующим блоком. Последние обеспечивают возможность наращивания разрядности обрабатываемых операндов.

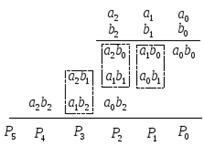

Р  аботу матричного множительного блока можно пояснить на примере перемножения двух трехразрядных чисел, представленных в двоичном коде. На первом этапе разряды множимого умножаются на младший разряд множителя, затем на старший и т.д. Полученные наборы частичных произведений суммируются со сдвигом на один разряд вправо.

аботу матричного множительного блока можно пояснить на примере перемножения двух трехразрядных чисел, представленных в двоичном коде. На первом этапе разряды множимого умножаются на младший разряд множителя, затем на старший и т.д. Полученные наборы частичных произведений суммируются со сдвигом на один разряд вправо.

Так как таблица умножения в двоичной системе счисления идентична таблице, описывающей операцию конъюнкции двух логических переменных, то получение компонент частичных произведений можно реализовать на элементах 2И. Для данного примера их понадобится 9.

Далее произведения разрядов необходимо просуммировать по столбцам с учетом переносов и в итоге получится результат, равный произведению чисел. Его разрядность будет равна сумме разрядностей сомножителей.

9) Вычитанию в разряде двоек соответствует строка 3, в разряде четверок - строка 6, в разряде восьмерок - строка 3, в разряде с весом 16 - строка 2 и в разряде с весом 32 - строка 6 таблицы истинности. Условное графическое обозначение полного вычитателя показано на рис. 15.2.

Рис. 15.2. Полный вычитатель. а - условное графическое обозначение, б - принципиальная схема

Рассмотрим схему 3-разрядного параллельного вычитателя, который построен на трех полных сумматорах и трех инверторах (рис. 15.15).

Рис. 15.15. Структурная схема вычитателя с использованием полных сумматоров

Инверторы обеспечивают преобразования двоичного числа  в форму дополнения до 1. Сумматоры складывают двоичные числа

в форму дополнения до 1. Сумматоры складывают двоичные числа  и

и  . Циклический перенос осуществляется с выхода

. Циклический перенос осуществляется с выхода  сумматора старшего разряда на вход

сумматора старшего разряда на вход  сумматора единиц. Разность двоичных чисел отображается на выходном индикаторе.

сумматора единиц. Разность двоичных чисел отображается на выходном индикаторе.

Для упрощения схемной реализации вычислительных машин было бы удобно иметь вместо отдельных вычитателя и сумматора одно универсальное вычислительное устройство. Оказывается, что использование простого математического "трюка" позволяет приспособить сумматор для выполнения операции вычитания.

10) Многоразрядный декрементор

строится из n полувычитателей, объединяемых трактом последовательного заёма.

При этом вход заёма осуществляется на вход вычитаемого в полувычитатель.

На один из входов младшего полувычитателя декрементора подаётся логическая единица.

Инкременторы и декременторы используются, например при организации серий обращений к последовательным адресам памяти.

Для этого они вводятся в состав микропроцессоров. Они выполняют функции счётчиков, но беззапоминания результата и соответственно без потери исходного числа.Оба числа: А и А+1 существуют одновременно, одно на входе, другое на выходе схемы.

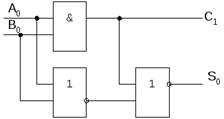

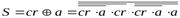

Инкрементор – схема для сложения двух чисел, а именно, переноса cr и числа a – схема полусумматор.

Функции, реализуемые полусумматором:

УГО:

Полусумматоры, соединенные последовательно по тракту переноса, образуют инкрементор, который иногда называют накапливающим сумматором.

УГО:

При подаче на вход "+1" нуля инкрементор записывает число а без изменения. Если подать единицу на вход "+1", то он прибавляет эту единицу к числу а.

Инкрементор можно построить с параллельным, с параллельно-групповым или с параллельно-последовательным переносом.

По аналогии с инкрементором строится и декрементор – узел, уменьшающий на единицу число а, если на вход "-1" подать единичный сигнал займа, тогда на выходе – число а -1.

Используются инкременторы и декременторы при организации обращения к последовательным адресам ЭВМ. Используются в роли счетчиков, но без запоминания информации. Это узел, в котором числа на входе и выходе существуют одновременно.

11) Данные узлы служат для определения четности количества единиц, либо нулей в многоразрядных двоичных словах. Если их число четное, то устройство вырабатывает на выходе определенный сигнал, например логический ноль, в противном случае – единицу.

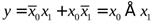

Синтез схемы контроля четности удобно начать с ее простейшего варианта для двухразрядного слова. Функция, описывающая четность количества единиц в нем, задается такой таблицей.

Так как разряды слова можно считать логическими переменными, то эта функция является одной из 16 от двух переменных, в частности – функцией логической неравнозначности. Таким образом, для контроля четности числа единиц в двухразрядном слове требуется использовать сумматор по модулю два, а алгебраически данная процедура записывается следующим образом  .

.

Для синтеза схем контроля четности в многоразрядных словах можно задать соответствующую функцию в табличной форме, затем определить ее аналитический вид и разработать схему на стандартных логических элементах. Однако такой способ является достаточно трудоемким, так как с увеличением разрядности слова на единицу, число строк таблицы удваивается. Поэтому в данной ситуации удобнее использовать нестандартный подход.

Пусть имеется n-разрядное двоичное слово  . Разобьем его на две части

. Разобьем его на две части  и предположим, что имеются устройства

и предположим, что имеются устройства  позволяющие формировать признаки четности количества единиц в них. Очевидно, что четность или нечетность числа единиц в частях слова, определенным образом зависит от ситуации с данным показателем для всего слова

позволяющие формировать признаки четности количества единиц в них. Очевидно, что четность или нечетность числа единиц в частях слова, определенным образом зависит от ситуации с данным показателем для всего слова

Это можно отразить следующим образом.

Если слово имеет четное число единиц, то при любом его разбиении в частях слова окажется по четному, либо по нечетному их количеству. При нечетном числе единиц во всем слове, в одной из его частей всегда окажется четное их количество, а в другой нечетное.

В скобках в таблице приведены значения сигналов, формируемых устройствами  и тех, которые должны появиться на выходе схемы контроля четности числа едини ц во всем слове. Видно, что эта таблица описывает функцию логической неравнозначности над переменными, формируемыми вспомогательными устройствами. Таким образом, структура схемы контроля четности должна иметь следующий вид.

и тех, которые должны появиться на выходе схемы контроля четности числа едини ц во всем слове. Видно, что эта таблица описывает функцию логической неравнозначности над переменными, формируемыми вспомогательными устройствами. Таким образом, структура схемы контроля четности должна иметь следующий вид.

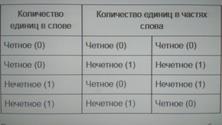

Разбивая части слова на более мелкие компоненты и проводя аналогичные рассуждения, можно придти к выводу, что в итоге потребуется первоначальный контроль четности количества единиц лишь в двух соседних разрядах слова и дополнительная обработка полученных результатов схемами логической неравнозначности. Отсюда следует, что один из вариантов принципиальной схемы устройства контроля четности будет выглядеть следующим образом.

При синтезе такого устройства стандартным способом оно получилось бы достаточно громоздким, так как функция, описывающая его работу относится к классу неминимизируемых в базисе И-НЕ, ИЛИ-НЕ.

Промышленностью выпускаются схемы контроля четности в интегральном исполнении, в частности микросхема К155ИП2. Она обрабатывает восьмибитовые слова и имеет входы расширения, позволяющие наращивать разрядность. Аналогичные функции выполняет микросхема К1533ИП5, работающая с девятиразрядными числами.

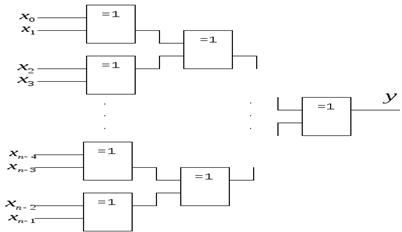

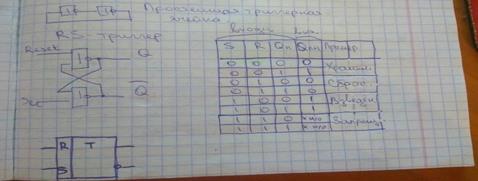

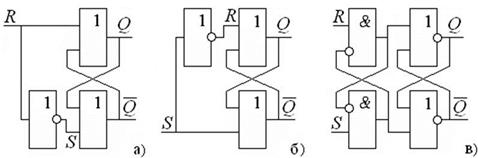

12) Основу триггеров составляют простейшие запоминающие ячейки, представляющие собой симметричную структуру из двух логических элементов ИЛИ-НЕ либо И-НЕ, охваченных перекрёстной обратной связью:

Ячейки могут находиться в двух устойчивых состояниях: 1 и 0. Состоянию 1 соответствует единичный сигнал на выходе Q, состоянию 0 соответствует единичный сигнал на выходе Q1.

Вход, по которому ячейка устанавливается в состояние 1, обозначается буквой S, а в состоянии 0 – буквой R.

Когда на обоих информационных кодах существуют логические нули (S=R=0), сигналы на выходе могут иметь одно из двух сочетаний: Q=1, Q1=0 либо Q=0, Q1=1, так как каждый логический элемент ИЛИ-НЕ инвертирует входные сигналы, а переключающим сигналом служит единица. Допустим, что Q=1. Этот сигнал, действуя на входе нижнего элемента создаёт на его выходе Q1=0. В свою очередь, на входах верхнего элемента два нулевых сигнала – со входа R и с выхода Q1, обеспечивает Q=1. Состояние это устойчивое.

Если на один из входов подать единичный сигнал, сохраняя нулевой на другом, триггер примет состояние, которое однозначно определяется входной информацией. При входных сигналах S=1, R=0 триггер принимает единичное состояние Q=1, Q1=0, а при S=0, R=1 – нулевое: Q=0, Q1=1. При появлении управляющего сигнала на одном из входов происходит либо опрокидывание триггера, либо подтверждение существующего состояния, если оно совпадает с требуемым.

Если одновременно подать переключающие сигналы на оба входа (S=R=1), на обоих выходах появятся логические нули (Q=Q1=0) и устройство утратит свойства триггера. Поэтому комбинацию S=R=1 называют неопределённой (н/о).

Переход от неопределённой комбинации к нейтральной (S=R=0) называют запрещенной комбинацией, так как состояние выходов при этом восстанавливается, но с равной вероятностью оно может стать единичным, так и нулевым, т.е. ведёт к непредсказуемому поведению триггера.

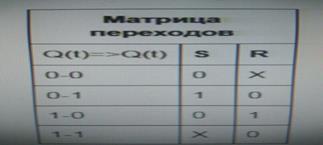

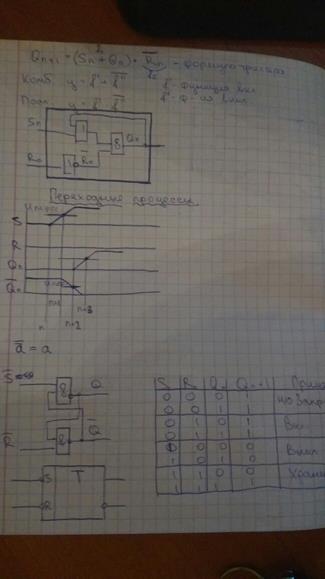

RS-триггер

RS-триггер [10][11], или SR-триггер (от англ. Set/Reset — установить/сбросить) — асинхронный триггер, который сохраняет своё предыдущее состояние при неактивном состоянии обоих входов и изменяет своё состояние при подаче на один из его входов активного уровня. При подаче на оба входа активного уровня состояние триггера вообще говоря неопределённо, но в конкретных реализациях на логических элементах оба выхода принимают состояния либо логического нуля, либо логической 1. В зависимости от конкретной реализации активным входным уровнем может быть как логическая 1, так и логический 0. Так, в RS-триггере выполненном на 2 элементах 2И-НЕ активным входным уровнем является логический 0.

JK – триггер – это схема с двумя устойчивыми выходными состояниями и двумя входами J и К (Рисунок 51.а). Подобно RS – триггеру, в JK – триггере входы J и K это входы установки выхода Q триггера в состояние 1 или 0. Однако, в отличие от RS – триггера, в JK – триггере наличие J=K=1 приводит к переходу выхода Q триггера в противоположное состояние. Условие функционирования JK – триггера описывается функцией:

Триггер JK –типа называют универсальным потому, что на его основе с помощью несложных коммутационных преобразований можно получить RS и Т – триггеры, а если между входами J и K включить инвертор, то получится схема D – триггера.

Недостатком этой схемы является зависимость работы схемы от длительности тактового импульса. Импульс должен быть коротким и должен закончиться до завершения процесса переключения триггера. Для ослабления требования к длительности тактового импульса в цепи обратных связей можно включить элементы задержки, как показано на рисунке 51,а пунктиром. Однако этот путь не всегда является целесообразным.

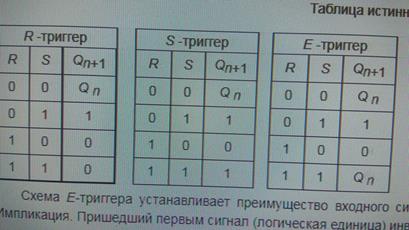

а)R-триггер б)S-триггер в)E-Триггер

Схема Е-Триггера устанавливает преимущество входного сигнала R или S,который появился на входе первым с помощью логической операции Импликация. Пришедший первым сигнал(1)инвертируется и устанавливает запрет на второй вход.

Е-Триггер исключает зажигание сигналов светофора одного цвета для различных направлений движения

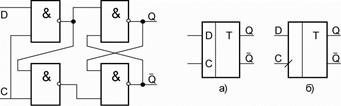

D-Триггер

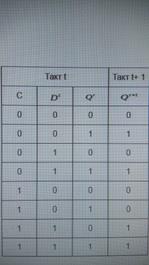

D– триггеры имеет один информационный вход (D- вход) для установки в “1” или “0” и вход синхронизации С (происходит от слова delay - задержка)

D– триггер задерживает на один такт информацию, существовавшую на входеD.

Закон функционирования D– триггера:

Структурная схема D– триггера и условные значения

а) – со статическим управлением

б) – с динамическим управлением

Таблица истинности.

Динамический триггер представляет собой систему, одно из состояний которой (единичное) характеризуется наличием на выходе непрерывной последовательности импульсов определённой частоты, а другое — отсутствием выходных импульсов (нулевое). Смена состояний производится внешними импульсами (рис. 3). Динамические триггеры в настоящее время используются редко.

К статическим триггерам относят устройства, каждое состояние которых характеризуется неизменными уровнями выходного напряжения (выходными потенциалами): высоким — близким к напряжению питания и низким — около нуля. Статические триггеры по способу представления выходной информации часто называют потенциальными.

Статические (потенциальные) триггеры, в свою очередь, подразделяются на две неравные по практическому значению группы — симметричные и несимметричные триггеры. Оба класса реализуются на двухкаскадном усилителе с положительной обратной связью, а названием своим они обязаны способам организации внутренних электрических связей между элементами схемы.

Симметричные триггеры отличает симметрия схемы и по структуре, и по параметрам элементов обоих плеч. Для несимметричных триггеров характерна неидентичность параметров элементов отдельных каскадов, а также и связей между ними.

На практике наибольшее распространение получила схема синхронного D-триггера со статическим управлением записью. D- триггер имеет один логический вход D (Delay — задержка), состояние которого с каждым СИ передается на выход, т.е. выходные сигналы представляют собой задержанные входные сигналы. Схему D-триггера можно получить из RS-триггера,если на вход R подать инвертированный сигнал входа S. Однако целесообразно использовать для инвертирования уже имеющиеся элементы

Синхронный D-триггер со статическим управлением записью(пунктиром показан вход V для DV-триггера):

а) логическая схема; б) условное графическое обозначение D-триггера и его таблица переходов; в) условное графическое обозначение DV-триггера и его таблица переходов

Если триггер переключается по фронту импульса синхронизации (переключение от логического 0 к логической 1), то это прямой динамический вход, а если по срезу импульса синхронизации (переключение от логической 1 к логическому 0) – инверсный динамический вход. На рис. 5.12 показаны условные графические обозначения триггеров с прямым и инверсным динамическим входом.

|

|

Рис. 5.12. Условные графические обозначения триггеров:

а - с прямым; б - с инверсным динамическим входом

Различие типа динамического входа иллюстрируют временные диаграммы работы триггеров, представленные на рис 5.13.

|

|

Рис. 5.13. Временные диаграммы работы триггеров:

а - с прямым; б - с инверсным динамическим входом

Временные диаграммы аналогичны временным диаграммам Т-триггера, но следует ещё раз отметить, что триггер с динамическим управлением переключается только при изменении сигнала на входе С и не чувствителен к изменению сигналов на информационных входах во время действия сигнала синхронизации С = 0 и С = 1.

Все D-триггеры на микросхемах серий ТТЛ и КМОП имеют вход С с динамическим управлением. На рис. 5.14. представлены условные графические обозначения D-триггеров.

|

|

Рис. 5.14. Условные графические обозначения D-триггеров

Кроме динамического входа С триггеры имеют статические входы данных D и асинхронные входы установки S и R. У микросхемы ТТЛ К155ТМ2 асинхронные входы установки инверсные, а у микросхемы КМОП К561ТМ2 – прямые. Как уже было отмечено в п. 5.3, D-триггеры широко представлены во всех сериях микросхем ТТЛ и КМОП. На основе D-триггеров строятся схемы счётчиков и регистров.

В одноступенчатом триггере имеется одна ступень запоминания информации, при этом, в состоянии записи триггер "прозрачен", т.е ложным срабатываниям устройств стоящих после триггера. В двухступенчатом триггере две ступени. Вначале информация записывается в первую ступень, все изменения на входе триггера во вторую ступень до сигнала перезаписи не попадают. все изменения на входе триггера повторяются на выходе триггера, что может привести к, затем, после перехода D-триггера первой ступени в режим хранения, информация переписывается во вторую ступень и появляется на выходе, что позволяет избежать состояния "прозрачности". Двухступенчатый триггер обозначают ТТ.(Информация на входе D по времени действия должна перекрывать тактовый сигнал С.Таким образом триггер считается прозрачным)

15) Из таблицы видно, что Т-триггер выполняет операцию сложения, это и обусловило название такого триггера счетным, его информационный (Т) вход– счетным входом. Уровень сигнала на входе такого триггера появляется в два раза чаще, чем на его выхо