| Тип ОУ | Вход | K 0, тыс. | U см, мВ | D U см/D Т,мкВ/ºС | I вх, нА D I вх | F 1, МГц | dU вых/ dt, В/мкс | K сф, дБ | D U вых,В | R вых, Ом I вых, мА | I пот, мА | U п.ном Диапазон |

| 140УД1Б | БП | 1¸12 | 0,8 | +6,7/ –5,0 | 2,5 | 12,6 | ||||||

| 140УД5Б | БП | 2,5 | +6,4/ –4,0 | 6¸13 | ||||||||

| 140УД7Б | БП | 0,8 вк | 0,3 | 20/кз | 3,5 | 5¸20 | ||||||

140УД708 140УД708

| БП | 0,8 вк | 0,3 | 10,5 | 20/кз | 3,5 | 5¸17 | |||||

| 140УД8А | ПТ | 0,2 0,15 | 1 вк | – | 5¸18 | |||||||

| 140УД24 | МОП | 0.005 | 0.05 | 0,01 0,005 | 2,5 | 4,7 | – – | 3,5 | 2,5¸8 | |||

| 544УД1А | ПТ | 0,05 0,02 | 1 вк | – | 3,5 | 7¸17 | ||||||

| 544УД2Б | ПТ | 0,5 0,5 | 5¸17 | |||||||||

| 551УД1А | БП | 1.5 | 0,8 | 0,01 | – | 5¸17 | ||||||

| К553УД2 | БП | 7.5 | 0,5 | – | 5¸20 |

Примечание. вк – внутренняя коррекция; кз – защита от короткого замыкания на выходе.

ЛАБОРАТОРНАЯ РАБОТА № 4

Цифровые схемы

Лабораторная работа посвящена изучению цифровых схем, знакомству с их устройством, основными параметрами, областью применения. В задачу студента входит изучение работы логических вентилей И, ИЛИ, И-НЕ, ИЛИ-НЕ, триггеров, макетирование и наладка нескольких цифровых схем – двоичного счетчика числа импульсов, сдвигового регистра, подавителя дребезга контактов, а также проведение необходимых измерений.

Введение

Одной из основных функций, выполняемых электронными схемами, является обработка или преобразование информации, заданной в виде электрического сигнала – напряжения или тока. Электрические сигналы могут представлять информацию в непрерывной (аналоговой) или дискретной (цифровой) форме.В настоящее время подавляющее большинство электронных схем представлено в виде интегральных микросхем, которые подразделяются на два основных вида – аналоговые и цифровые. В этой работе рассматриваются цифровые микросхемы малой и средней степени интеграции. Цифровые электронные устройства работают в соответствии с логическими правилами, теоретической основой которых служит алгебра логики, или булева алгебра. В булевой алгебре все переменные и результаты операций над ними принимают только два значения «1» или «0». Для конечного числа логических переменных число логических функций конечно. От N независимых переменных можно составить  различных функций. Наиболее важные логические функции – И, ИЛИ, НЕ. Система простых логических функций, на основе которой, используя лишь операцию суперпозиции, можно получить любую логическую функцию, называется функционально полной. Функционально полными являются, например, системы (И – НЕ), (ИЛИ – НЕ).

различных функций. Наиболее важные логические функции – И, ИЛИ, НЕ. Система простых логических функций, на основе которой, используя лишь операцию суперпозиции, можно получить любую логическую функцию, называется функционально полной. Функционально полными являются, например, системы (И – НЕ), (ИЛИ – НЕ).

Если в цифровом устройстве состояние выходов является определенной функцией текущих входных переменных, то такое устройство может быть реализовано на одних только вентилях (комбинационная логика). Существует другой класс задач (последовательная логика), которые не могут быть решены с помощью комбинационных схем. Например, для подсчета числа импульсов, преобразования двоичного последовательного кода в параллельный требуется специальный элемент, обладающий «памятью». Такими цифровыми элементами являются различные виды триггеров.

Логические вентили

Логическими вентилями называются функциональные устройства, реализующие логические операции над входными переменными.

Таблица 4.1

Таблица истинности И

| X 1 | X 2 | Y |

Таблица 4.2

Таблица истинности функции ИЛИ

| X 1 | X 2 | Y |

Таблица 4.3

Таблица истинности функции НЕ

| X | Y |

Таблица 4.4

Вентиль И-НЕ

| X 1 | X 2 | Y |

Таблица 4.5

Вентиль ИЛИ-НЕ

| X 1 | X 2 | Y |

Вентиль И реализует операцию логического умножения (конъюнкция). Логический сигнал на выходе Y =«1» возникает только при наличии сигналов X 1 = X 2 =... = Xn = «1» одновременно на всех входах. Функцию логического умножения можно записать в виде формулы Y = X 1 & X 2 ... Xn или Y = X 1 × X 2 ... Xn,

а также представить в виде так называемой таблицы истинности (табл. 4.1).

Вентиль ИЛИ выполняет функцию логического сложения (дизъюнкция). Для этой схемы Y = «1» при наличии логической «1» хотя бы на одном из входов: Y = X 1 v X 2 v...v Xn или Y = X 1 +

+ X 2 +... + Xn. Таблица истинности функции ИЛИ для двух сигналов – это табл. 4.2.

Вентиль НЕ (инвертор) реализует функцию логического отрицания и представляет собой одновходовую схему, на выходе которой сигнал Y = «1» возникает при X = «0» на входе. Логическое отрицание обозначают сплошной линией над переменной:  . Таблица истинности функции НЕ – это табл. 4.3.

. Таблица истинности функции НЕ – это табл. 4.3.

Вентили И-НЕ (штрих Шеффера) с таблицей истинности (табл. 4.4), ИЛИ-НЕ (стрелка Пирса) с таблицей истинности (табл. 4.5) совмещают сразу две функции. Эти вентили оказываются более удобными в практических схемах. Кроме того, и в ТТЛ- и в КМОП-технологии их внутреннее устройство проще, и, как следствие, временные задержки примерно в два раза меньше, чем у вентилей И, ИЛИ. Вентили И-НЕ, ИЛИ-НЕ каждый в отдельности образуют функционально полную систему, т.е. на основе любого из них можно построить любую комбинационную схему, а с учетом того, что на вентилях реализуются различные триггеры, то и любое цифровое устройство, например компьютер. Графические изображения логических вентилей приведены на рис. 4.1.

Рис. 4.1. Условные обозначения логических вентилей

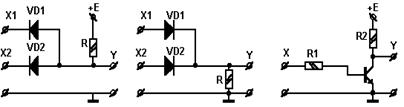

Простейшая реализация схемы 2 И приведена на рис. 4.2, а. Напряжение на выходе U вых = + E, что соответствует логической «1», будет только в том случае, когда на обоих входах будет потенциал + E. Если хотя бы один вход подсоединен к логическому нулю, на выходе будет напряжение, близкое к нулю (падение напряжения на открытом диоде).

Реализация схемы 2 ИЛИ приведена на рис. 4.2, б. Напряжение на выходе будет близко к + E (логическая «1»), если хотя бы на один из входов подать потенциал + E.

а б в

Рис. 4.2. Логические вентили И, ИЛИ, НЕ

Логическая схема НЕ наиболее просто выполняется с помощью транзисторного ключа (рис. 4.2, в) (транзистор включен по схеме с общим эмиттером). Если вход подсоединен к «0», транзистор заперт, на выходе потенциал + E = «1». Если на входе «1», то транзистор открыт до насыщения и U вых » 0, т. е. является логическим нулем. Такие простейшие логические схемы обладают большим количеством недостатков и на практике не применяются. Промышленностью выпускается множество семейств (серий и типов) цифровых интегральных схем. Однако самое широкое применение находят серии ТТЛШ – транзисторно-транзисторная логика с диодами Шоттки и КМОП – на комплементарных МОП-транзисторах. Схема базового ТТЛ-вентиля И-НЕ показана на рис. 4.3. Она содержит три основных каскада: входной, реализующий функцию И на многоэмиттерном транзисторе VT1, который управляет транзистором VT2. Если VT2 открыт, то VT4 закрыт, а VT5 открыт, и на выходе Y будет напряжение логического нуля (»0 В). Наоборот, если VT2 закрыт, то VT4 открыт, VT5 закрыт, на выходе Y будет напряжение логической единицы. Корректирующая цепь R3, R4, VT3 улучшает форму передаточной характеристики.

Передаточная характеристика вентиля НЕ ТТЛ-логики (зависимость выходного напряжения от входного) при разных температурах приведена на рис. 4.4. Как видно из него, инвертор представляет собой усилитель с двумя уровнями ограничения и квазилинейной областью с большим коэффициентом усиления.

| Рис. 4.3. Базовый логический вентиль И-НЕ серии 155 | Рис. 4.4. Передаточная характеристика инвертора ТТЛ |

Входная характеристика ТТЛ-вентиля (зависимость входного тока от входного напряжения) представлена на рис. 4.5. Входной ток логического «0» по модулю намного больше входного тока логической «1», что учитывается схемотехническим решением выходного каскада вентиля. В состоянии «логический 0» на выходе вентиль может отдать ток, намного больший, чем в состоянии «логическая 1», так как в первом случае выход замыкается на «землю» открытым транзистором VT5 (см. рис. 4.3), а во втором – подсоединяется к потенциалу питания V cc через резистор R5. Из сказанного следует, в частности, что выход ТТЛ соединять с напряжением питания V cc нельзя! Простая оценка: базовый ток транзистора VT5 в состоянии «логический 0» I б » 4 мА; при b » 125 ток коллектора I к = b· I б » 0,5 А, мощность на транзисторе VT5 P VT5 I к· V cc » 2,5 Вт. Так как размеры транзистора VT5 на кристалле очень малы, то это приводит практически к мгновенному выходу из строя микросхемы. Вентиль из серии ТТЛ, изображенный на рис. 4.3, носит название насыщенного, так как транзисторы в проводящем состоянии находятся в области насыщения. Это приводит к накоплению носителей в базах транзисторов, следовательно, к снижению быстродействия. Применение транзисторов и диодов с барьером Шоттки, имеющих малое падение напряжения в проводящем состоянии, позволяет избежать насыщения транзисторов и увеличить быстродействие. Эти схемы обозначаются ТТЛШ. К ним относятся МС серий 555, 1531, 1533 и др. В настоящее время они вытесняют схемы ТТЛ. Схемы ТТЛ и ТТЛШ в большинстве случаев взаимозаменяемы (кроме ограничений по быстродействию и потребляемой мощности).

Рис. 4.5. Входной ток ТТЛ-схем

Напряжение питания ТТЛ-схем – +5 В, напряжение низкого уровня (логический ноль) – 0 ¸ 0,4 В, напряжение высокого уровня (логическая единица) – 2,4 ¸ 5 В. Параметры применяемых в данной работе схем ТТЛ (и замещающих их ТТЛШ) даны в приложении. Схемы ТТЛ (ТТЛШ) в любом состоянии потребляют значительный ток, от единиц до десятков миллиампер. Особенностью микросхем КМОП является исключительно малая мощность, потребляемая в статическом режиме, на несколько порядков меньше схем ТТЛ. Однако быстродействие схем КМОП в несколько раз меньше, чем у схем ТТЛ. Например, статическая средняя мощность потребления одного элемента ТТЛ серии 155 составляет несколько десятков милливатт, а у вентиля КМОП серий 176 и 561 – примерно в тысячу раз меньше. Среднее время задержки распространения сигнала вентилем ТТЛ серии 155 составляет около 20 нс (20·10–9 с), для вентилей КМОП серии 176 – примерно 200 нс, КМОП серии 561 и 1561 дают задержку 100¸120 нс.

Причину малого потребления тока КМОП-схемами легко показать на примере вентиля И-НЕ (рис. 4.6). Транзисторы VT1 и VT2 включены последовательно, а VT3, VT4 – параллельно. Если хотя бы на один из входов, например, на Х1, подан логический «0», то VT1 заперт, а VT3 открыт, и, независимо от состояния на входе X2, на выходе будет логическая «1», т.е. потенциал, близкий к V cc . Только в случае, когда на оба входа подана «1», транзисторы VT1 и VT2 открываются, а VT3 и VT4 закрываются, и на выходе получаем 0 В, т.е. логический «0». Нетрудно видеть, что в любом состоянии сквозного тока через вентиль нет, за исключением ничтожного тока утечки (10–15 ¸ 10–15 А). Сказанное справедливо для квазистатического режима, когда частота переключений мала. В динамическом режиме, при большой частоте микросхемы КМОП-логики потребляют ток порядка нескольких миллиампер. Большая часть этого тока затрачивается на перезаряд внутренних емкостей транзисторов и емкости нагрузки. Кроме того, когда во время переключения один транзистор открывается быстрее, чем другой закрывается, через них протекает импульс сквозного тока порядка 10 мА. В отличие от ТТЛ-схем напряжение питания КМОП-логики можно менять в широких пределах (обычно 3¸15 В), хотя при малых напряжениях питания быстродействие и нагрузочная способность ухудшаются.

Причину малого потребления тока КМОП-схемами легко показать на примере вентиля И-НЕ (рис. 4.6). Транзисторы VT1 и VT2 включены последовательно, а VT3, VT4 – параллельно. Если хотя бы на один из входов, например, на Х1, подан логический «0», то VT1 заперт, а VT3 открыт, и, независимо от состояния на входе X2, на выходе будет логическая «1», т.е. потенциал, близкий к V cc . Только в случае, когда на оба входа подана «1», транзисторы VT1 и VT2 открываются, а VT3 и VT4 закрываются, и на выходе получаем 0 В, т.е. логический «0». Нетрудно видеть, что в любом состоянии сквозного тока через вентиль нет, за исключением ничтожного тока утечки (10–15 ¸ 10–15 А). Сказанное справедливо для квазистатического режима, когда частота переключений мала. В динамическом режиме, при большой частоте микросхемы КМОП-логики потребляют ток порядка нескольких миллиампер. Большая часть этого тока затрачивается на перезаряд внутренних емкостей транзисторов и емкости нагрузки. Кроме того, когда во время переключения один транзистор открывается быстрее, чем другой закрывается, через них протекает импульс сквозного тока порядка 10 мА. В отличие от ТТЛ-схем напряжение питания КМОП-логики можно менять в широких пределах (обычно 3¸15 В), хотя при малых напряжениях питания быстродействие и нагрузочная способность ухудшаются.

Историческая справка

На первых этапах развития биполярных транзисторных микросхем предсказывали широкое распространение комплементарных биполярных логических элементов на p-n-p- и n-p-n -транзисторах. К примеру, если в ТТЛ-схемах удалось бы заменить выходной каскад на двухтактный комплементарный, принципиально понизилась бы потребляемая мощность. Однако биполярная комплементарная транзисторная логика не прижилась из-за трудности изготовления на кристалле большого количества компактных по площади и высококачественных по параметрам интегральных p-n-p -транзисторов. В аналоговой схемотехнике, где p-n-p -транзисторы просто необходимы как для упрощения схемотехники, так и для улучшения свойств усилителей (см. лабораторную работу № 3 «Операционные усилители»), проблема создания хороших p-n-p -транзисторов для технологов все еще существует. Поэтому реально биполярные микросхемы ТТЛ имеют на выходе так называемый квазикомплементарный каскад, когда на кристалле делают только n-p-n -транзисторы (см. рис. 4.3). Эта компромиссная схема вентиля ТТЛ оказалась оптимальной и применяется в течение нескольких десятилетий. Первые попытки выпускать микросхемы на полевых транзисторах одной полярности к успеху не привели. Логические вентили получались крайне медленнодействующими, поскольку внутреннее сопротивление канала у полевого транзистора на порядок больше, чем сопротивление между коллектором и эмиттером насыщенного биполярного транзистора. Однополярные микросхемы МОП не отличались ни помехоустойчивостью, ни малой потребляемой мощностью. Хорошие результаты дало только применение двуполярного инвертора, построенного на комплементарной полевой паре.

Триггеры

Как уже упоминалось выше, для построения цифровых схем последовательной логики необходим элемент, обладающий «памятью». Очевидно, он должен иметь два устойчивых состояния и переходить из одного в другое при определенном воздействии. Элемент с такими свойствами называется триггер.

Триггер можно получить, охватив два вентиля И-НЕ перекрестными обратными связями, как показано на рис. 4.7, а. Этот триггер имеет два выхода Q 1 , Q 2 и два входа – S (Set – установка) и R (Reset – сброс). Пусть в последовательные интервалы времени t1,..., t6 логические уровни на входах R и S принимают значения, как показано в табл. 4.6. В интервалах t1, t3, t5 состояние выходов повторяет состояние входов, что следует из табл. 4.3 и 4.4. Интервалы t2, t4 (R = «0», S = «0») соответствуют режиму хранения информации – триггер «помнит» предыдущее состояние. При переходе от интервала t5 к интервалу t6 триггер может установиться в любое состояние, что определяется внутренними задержками вентилей.

а б в

Рис. 4.7. RS -триггеры на логических вентилях

Таблица 4.6

Таблица истинности RS -триггера

| t | S | R | Q 1 | Q 2 |

| t1 | ||||

| t2 | ||||

| t3 | ||||

| t4 | ||||

| t5 | ||||

| t6 | Неопр. |

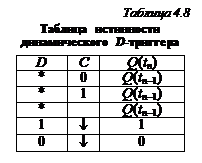

Таблица 4.7

Таблица истинности D -триггера

| D | C | Q (tn) |

| Q (tn –1) | ||

| Q (tn +1) | ||

Если принять комбинацию (R = «1», S = «1») запрещенной, то логические уровни на выходах будут всегда противоположны, т.е.  , поэтому выходы триггера обозначают Q и

, поэтому выходы триггера обозначают Q и  (прямой и инверсный), как на рис. 4.7, б. Такой элемент получил название RS -триггер. RS -триггеры применяются прежде всего в статических оперативных запоминающих устройствах (ОЗУ). На рис. 4.7, б приведена схема RS -триггера с инверсными входами, а на рис. 4.7, в – его обозначение. Если этот RS -триггер дополнить комбинационной логикой, как показано на рис. 4.8, то получим статический D -триггер с двумя входами: информационным – D (Data) и синхронизирующим – С (Clock). Как следует из таблицы истинности статического D -триггера (табл. 4.7), он повторяет на выходе Q логическое состояние входа D при C = = «1» и сохраняет («защелкивает») это значение при C = «0». На основе таких триггеров делают, как правило, параллельные регистры хранения (ТМ5, ТМ7, ИР22 серии ТТЛ).

(прямой и инверсный), как на рис. 4.7, б. Такой элемент получил название RS -триггер. RS -триггеры применяются прежде всего в статических оперативных запоминающих устройствах (ОЗУ). На рис. 4.7, б приведена схема RS -триггера с инверсными входами, а на рис. 4.7, в – его обозначение. Если этот RS -триггер дополнить комбинационной логикой, как показано на рис. 4.8, то получим статический D -триггер с двумя входами: информационным – D (Data) и синхронизирующим – С (Clock). Как следует из таблицы истинности статического D -триггера (табл. 4.7), он повторяет на выходе Q логическое состояние входа D при C = = «1» и сохраняет («защелкивает») это значение при C = «0». На основе таких триггеров делают, как правило, параллельные регистры хранения (ТМ5, ТМ7, ИР22 серии ТТЛ).

а б в

Рис. 4.8. D -триггеры на логических вентилях

Выходной RS -триггер D -триггера может иметь дополнительные логические входы R и S для очистки/установки (рис. 4.9).

Статические RS - и D -триггеры не пригодны для построения счетчиков и регистров сдвига, так как информация на выходе изменяется синхронно с входной, либо просто хранится. Триггер, в котором отсутствует сквозная передача со входа на выход,

Рис. 4.9. Схема реализации D -триггера типа

Master-Slave

а выходная информация устанавливается синхросигналом при блокировании входных сигналов, можно построить на RS -триггерах и комбинационной логике.

На рис. 4.9 приведена структура, построенная по принципу «Ведущий-Ведомый» (Master-Slave). Схема содержит два статических D -триггера и инвертор. Так как статические D -триггеры Master и Slave принимают информацию во взаимно исключающие моменты времени, такую структуру называют триггером, тактируемым фронтом (динамический триггер). Состояния динамического D -триггера приведены в табл. 4.8, где * – любое состояние, – переход «0» ® «1», ¯ – переход «1» ® «0». Другая структура динамического D -триггера, построенного на RS -триггерах, показана на рис. 4.10. Если

На рис. 4.9 приведена структура, построенная по принципу «Ведущий-Ведомый» (Master-Slave). Схема содержит два статических D -триггера и инвертор. Так как статические D -триггеры Master и Slave принимают информацию во взаимно исключающие моменты времени, такую структуру называют триггером, тактируемым фронтом (динамический триггер). Состояния динамического D -триггера приведены в табл. 4.8, где * – любое состояние, – переход «0» ® «1», ¯ – переход «1» ® «0». Другая структура динамического D -триггера, построенного на RS -триггерах, показана на рис. 4.10. Если  = «1», то при C = «0» имеем X 2 = X 3 = «1»; X 1 =

= «1», то при C = «0» имеем X 2 = X 3 = «1»; X 1 =  ; X 4 = D; выходной RS -триггер находится в режиме хранения. В зависимости от значения на входе D один из входных триггеров обязательно находится в «запрещенном» состоянии, т.е. оба выхода находятся в состоянии «1». Это состояние исчезает при переходе сигнала C «0» ® ® «1», а выходной сигнал Q устанавливается входным триггером, находящимся в «разрешенном» состоянии: при D = «0» X 3

; X 4 = D; выходной RS -триггер находится в режиме хранения. В зависимости от значения на входе D один из входных триггеров обязательно находится в «запрещенном» состоянии, т.е. оба выхода находятся в состоянии «1». Это состояние исчезает при переходе сигнала C «0» ® ® «1», а выходной сигнал Q устанавливается входным триггером, находящимся в «разрешенном» состоянии: при D = «0» X 3

сохраняется в состоянии «1», X 2 переходит в состояние «0»,

Q = «0»,  = «1»; при D = «1» X 2 и X 3 меняются ролями и переход X 3 «1» ® «0» устанавливает на выходе Q = «1»,

= «1»; при D = «1» X 2 и X 3 меняются ролями и переход X 3 «1» ® «0» устанавливает на выходе Q = «1»,  = «0». По входам

= «0». По входам  производится сброс и установка D -триггера. Описанную структуру имеет популярный D -триггер К155ТМ2 (К555ТМ2, К1533ТМ2). Состояния этого триггера приведены в табл. 4.9. Еще один вид триггера – T -триггер, часто называемый счетным, меняет свое состояние на противоположное при поступлении каждого синхронизирующего импульса. Устройство и принцип работы его описаны в литературе [1, 2].

производится сброс и установка D -триггера. Описанную структуру имеет популярный D -триггер К155ТМ2 (К555ТМ2, К1533ТМ2). Состояния этого триггера приведены в табл. 4.9. Еще один вид триггера – T -триггер, часто называемый счетным, меняет свое состояние на противоположное при поступлении каждого синхронизирующего импульса. Устройство и принцип работы его описаны в литературе [1, 2].

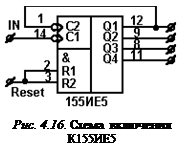

Т -триггер применяется в качестве делителя частоты на 2. Соединяя последовательно N счетных триггеров, можно получить делитель частоты 2 N, а также устройства для счета импульсов. В данной работе используется МС К155ИЕ5, позволяющая делить входную частоту на 16.

Области применения разных триггеров в цифровой схемотехнике весьма обширны. Простое и полезное применение RS -триггеры получили в схемах подавления дребезга механических коммутирующих устройств. Если подавать сигналы «0» и «1» на цифровую схему с помощью переключателя – тумблера, как показано на рис. 4.11, а, то возникнет очень неприятное явление – дребезг контактов. В течение нескольких миллисекунд после замыкания переключателя его контакты входят в соприкосновение друг с другом от десятков до сотен раз. Если к выходу такой схемы подключить какой-либо счетчик импульсов, то он не сосчитает количество переключений тумблера, а отреагирует на каждый дополнительный импульс, вызванный этим дребезгом. Схема, изображенная на рис. 4.11, б, позволяет полностью подавить дребезг.

Области применения разных триггеров в цифровой схемотехнике весьма обширны. Простое и полезное применение RS -триггеры получили в схемах подавления дребезга механических коммутирующих устройств. Если подавать сигналы «0» и «1» на цифровую схему с помощью переключателя – тумблера, как показано на рис. 4.11, а, то возникнет очень неприятное явление – дребезг контактов. В течение нескольких миллисекунд после замыкания переключателя его контакты входят в соприкосновение друг с другом от десятков до сотен раз. Если к выходу такой схемы подключить какой-либо счетчик импульсов, то он не сосчитает количество переключений тумблера, а отреагирует на каждый дополнительный импульс, вызванный этим дребезгом. Схема, изображенная на рис. 4.11, б, позволяет полностью подавить дребезг.

а б

Рис. 4.11. Подавление дребезга механических контактов с помощью RS -триггера

Основными параметрами цифровых микросхем являются быстродействие, потребляемая мощность, помехоустойчивость, коэффициент разветвления по выходу (нагрузочная способность), коэффициент объединения по входу. Конструктивно микросхемы выполняются в стандартных пластмассовых, керамических или металлостеклянных корпусах различных форм и размеров. Обозначение на корпусах отечественных микросхем состоит из нескольких элементов, включающих в себя номер серии (трех- или четырехзначное число); две буквы, обозначающие выполняемую логическую функцию; цифру, обозначающую порядковый номер разработки по функциональному признаку в данной серии. Перед первым элементом обозначения могут стоять еще различные буквы, характеризующие область применения, конструкцию или тип корпуса.

Примеры обозначения микросхем:

К155ЛА3 – четыре логических вентиля 2И-НЕ (ЛА3) серии 155; КМ155ЛА1 – два логических вентиля 4И-НЕ (ЛА1) серии 155 широкого применения в металлокерамическом корпусе; К555ТМ2 – два D -триггера (ТМ2) серии 555 (с диодами Шоттки); 155ТМ7 – четыре D -триггера с прямыми и инверсными выходами (ТМ7) серии 155 с расширенным температурным диапазоном; К155ИЕ5 – четырехразрядный двоичный счетчик (ИЕ5) серии 155; КР1533ИЕ7 – четырехразрядный реверсивный двоичный счетчик с загрузкой и сбросом (ИЕ7) серии 1533 в пластмассовом корпусе. На старых микросхемах можно встретить обозначения К1ЛБ553, что соответствует К155ЛА3; К1ТК552 соответствует К155ТМ2 и т.д.

Практические задания

Все изменения в схеме делать только при отключенном питании! Выходы ТТЛ на +5 В не замыкать!

1. Проверить по таблице истинности (табл. 4.4) работу одного из двух свободных вентилей 2И-НЕ микросхемы 155ЛА3. Цоколевка приведена на рис. 4.12 и 4.13. Номера ножек микросхем считаются от ключа против часовой стрелки.

2. Измерить входной ток логического нуля и логической единицы для одного из вентилей 2И-НЕ (155ЛА3). Проще всего это сделать, замыкая вход на нуль и на + E п подходящим резистором и измеряя падение напряжения на нем. Номинал резистора (шунта) легко выбрать, пользуясь справочными данными из приложения и условием, что падение напряжения на нем должно составлять не более 0,1÷0,2 В. Заметим, что измеренные значения могут существенно отличаться от справочных.

3. Из двух вентилей 2И-НЕ собрать схему подавителя дребезга на RS -триггере по рис. 4.11, б. Рассмотреть дребезг на входах 9 и 13 и убедиться в его отсутствии на выходах Q и  . Синхронизация осциллографа – ждущая, длительность развертки – подобрать.

. Синхронизация осциллографа – ждущая, длительность развертки – подобрать.

4. Собрать двоичный делитель на четырех D -триггерах 155ТМ2 (555ТМ2) по рис. 4.14. Для этого на входы  и

и  подать логическую единицу. Соединить выходы

подать логическую единицу. Соединить выходы  с D -входами. На вход C первого триггера подать сигнал с мультивибратора,

с D -входами. На вход C первого триггера подать сигнал с мультивибратора,

| Рис. 4.12. Пример цоколевки ИМС | Рис. 4.13. Мультивибратор на элементах И-НЕ |

собранного на двух вентилях 2И-НЕ (см. рис. 4.13). Засинхронизировать осциллограф в ждущем режиме от последнего триггера (вых. 1, см. рис. 4.14). Наблюдать сигналы на всех выходах триггеров. Собрать все выходы по И на вентиле 4И-НЕ (половинка 155ЛА1). Объяснить вид сигнала на вых. 2 и наличие узкого импульса – «иголки» при переходе 1000 ® 0111 на выходах  (старший разряд записан первым). Засинхронизировать осциллограф от сигнала «Вх.», на самой быстрой развертке измерить задержку триггера и сопоставить ее со справочными данными.

(старший разряд записан первым). Засинхронизировать осциллограф от сигнала «Вх.», на самой быстрой развертке измерить задержку триггера и сопоставить ее со справочными данными.

Рис. 4.14. Двоичный делитель на D -триггерах

5. Преобразовать делитель на 16 в делитель на 10. Для этого все входы  подключить к выходу вентиля 155ЛА1 (вых. 2). На входы вентиля подать такие сигналы с выходов триггеров, чтобы при комбинации 1010 на выходах

подключить к выходу вентиля 155ЛА1 (вых. 2). На входы вентиля подать такие сигналы с выходов триггеров, чтобы при комбинации 1010 на выходах  (двоичный код числа

(двоичный код числа

Рис. 4.15. Регистр сдвига на D -триггерах

10) вентиль отдавал на выход уровень «логический 0» (установка всех триггеров в состояние  = «0»).

= «0»).

6. Из четырех D -триггеров (два корпуса МС 155ТМ2) и двух 4И-НЕ (155ЛА1) собрать схему сдвигового регистра (рис. 4.15). На входы  и

и  подать логическую единицу. На все входы C подать сигнал с мультивибратора (см. рис. 4.13). Засинхронизовать осциллограф в ждущем режиме от выхода первого триггера. Наблюдать сигналы на всех выходах и их взаимное положение. Объяснить работу устройства. Через сколько импульсов схема приходит в исходное состояние?

подать логическую единицу. На все входы C подать сигнал с мультивибратора (см. рис. 4.13). Засинхронизовать осциллограф в ждущем режиме от выхода первого триггера. Наблюдать сигналы на всех выходах и их взаимное положение. Объяснить работу устройства. Через сколько импульсов схема приходит в исходное состояние?

Дополнительные задания

7. Подать сигнал от мультивибратора (рис. 4.16) на вход C 1 микросхемы К155ИЕ5. Микросхема включает в себя делитель на 2 (C 1® Q 1) и делитель на 8

7. Подать сигнал от мультивибратора (рис. 4.16) на вход C 1 микросхемы К155ИЕ5. Микросхема включает в себя делитель на 2 (C 1® Q 1) и делитель на 8

(C 2 ® Q 2, Q 3, Q 4). Все выходы Qi сбрасываются в «0», если на оба входа R1 и R2 подать «логическую 1», т.е. Reset = R1 и R2. Таким образом, чтобы получился делитель на 16, нужно Q 1 соединить с C 2. Исследовать сигналы с выходов Q 1, Q 2, Q 3, Q 4.

8. Без использования вентиля 155ЛА1, коммутируя только входы-выходы 155ИЕ5, получить делитель на 10 и на 12. Измерить задержки фронта на разных выходах.

Содержание отчета

1. Цель работы.

2. Рисунки принципиальных схем в системе ОrCAD.

3. Результаты измерений в виде таблиц, графиков, вычислений с необходимыми пояснениями.

4. Выводы по работе. В выводах подчеркните результаты, полученные от каждой схемы, укажите, какие элементы оказывают наибольшее влияние на работу той или иной схемы.

Контрольные вопросы

1. Какой сигнал будет на выходе вентилей ТТЛ и КМОП, если на все входы не подавать ничего, оставив их свободными?

2. Оценить потребление тока вентилем 2И-НЕ (см. рис. 4.3) в состояниях «0» и «1» на выходе.

3.Оценить ток, потребляемый вентилем КМОП (см. рис. 4.6) при V cc = 10 В; C нагр = 10 пФ; F = 1 МГц. Как этот ток зависит

от V cc?

4. Как по заданному булеву выражению составить таблицу истинности?

5. Что такое карты Карно и как они составляются?

6.Построить схему на основе булева выражения в конъюнктивной нормальной форме.

7. Что такое мультиплексор?

8. Алгоритм построения нерегулярных цифровых схем на основе логики И-НЕ.

список Литературы

1. Титце У., Шенк К. Полупроводниковая схемотехника. – М.: Мир, 1989.

2. Хоровиц П., Хилл У. Искусство схемотехники. Т. 1. – М.: Мир, 1993.

3. Гусев В.Г., Гусев Ю.М. Электроника. – М.: Высшая школа, 1991.

4. Токхейм Р. Основы цифровой электроники. – М.: Мир, 1988.

5. Алексеенко А.Г., Шагурин И.И. Микросхемотехника. – М.: Радио и связь, 1982.

Приложение

| Параметр | К155ЛА1 | К155ЛА3 | К155ТМ2 | К155ИЕ5 | К555ЛА3 |

| I пот.0, не более, мА | 4,4 | ||||

| I пот.1, не более, мА | 1,6 | ||||

| I вх.0, не более, мА | –1,6 | –1,6 | –1,6 | * | 0,4 |

| I вх.1, не более, мкА | * | ||||

| U вых. 0, не более, В | 0,4 | 0,4 | 0,4 | 0,4 | 0,5 |

| U вых. 1, не менее, В | 2,4 | 2,4 | 2,4 | 2,4 | 2,7 |

| t зад.1®0, не более, нс | |||||

| t зад.0®1, не более, нс | |||||

| Вывод питания +5 В | |||||

| Вывод общий |

Содержание

Лабораторная работа № 1. Изучение принципов работы в САПР OrCAD на примере моделирования каскада на биполярном транзисторе........................................................ 3

Лабораторная работа № 2. Генераторы напряжения...................... 12

Моделирование генератора на биполярном транзисторе.... 12

Генераторы гармонических сигналов.................................. 16

Импульсные генераторы........................................................... 20

Порядок выполнения работы.................................................. 22

Содержание отчета.................................................................... 24

Контрольные вопросы............................................................... 24

Лабораторная работа № 3. Операционные усилители................... 24

Введение.............................................................................................. 25

1. Параметры операционных усилителей............................... 27

2. Схемы включения операционных усилителей.................. 32

3. Практические задания.............................................................. 37

3.1. Измерение (U см), (f 1), (I вх), (D I вх)....................................... 37

3.2. Наблюдение температурного дрейфа и низкочастотного шума 38

3.3. Интегратор.......................................................................... 38

3.4. Компаратор с гистерезисом........................................... 39

3.5. Прецизионный выпрямитель.......................................... 40

3.6. Измерение ЭДС термопары............................................ 40

Содержание отчета....................................................................... 41

Контрольные вопросы.................................................................. 41

Список литературы....................................................................... 41

Приложение..................................................................................... 42

Лабораторная работа № 4. Цифровые схемы..................................... 43

Введение.............................................................................................. 43

Логические вентили....................................................................... 44

Историческая справка.................................................................. 50

Триггеры........................................................................................... 51

Практические задания.................................................................. 56

Дополнительные задания............................................................ 58

Содержание отчета....................................................................... 58

Контрольные вопросы.................................................................. 59

Список литературы....................................................................... 59

Приложение..................................................................................... 60

|