Факультет электроники и компьютерных технологий (ЭКТ)

Ефимов Николай Игоревич

Бакалаврская работа

по направлению 11.03.04 «Электроника и наноэлектроника»

Разработка делителя частоты с переменным коэффициентом деления 7, 14, 16, 23 на основе JK-триггера.

Студент Ефимов Н.И.

Научный руководитель,

к.т.н Ермаков И.В.

Москва 2016

СОДЕРЖАНИЕ

Введение……………………………………………………………………..........................3

Техническое задание………………………………………………………………………..4

Глава 1. Проектирование делителя частоты.......................................….….…………..….5

1.1. Логическое проектирование……………………………………………...…5

1.2. Схемотехническое проектирование……………………….….…................8

1.3. Топологическое проектирование………………………………….............18

1.4. Выводы………………………………………………………………….…..22

Глава 2. Разработка и исследование технологического маршрута..……...…………....23

2.1. Эскиз и маршрут создания транзисторов ………………..……...............23

2.2. Одномерное моделирование …………………………………..…..............32

2.3. Двухмерное моделирование ……………..……………………..................34

2.4. Выводы……………………………………………………………………...38

Глава 3. Методы защиты от тиристорного эффекта в устройстве синхронизации и коммутации.............................................................….………………….......…..…...……39

3.1. Проблема и способы защиты от тиристорного эффекта............................39

3.2. Влияние тиристорного эффекта на радиоэлектронную аппаратуру специального и космического назначения …………….…...........................…...............43

3.3. Реализация защиты от тиристорного эффекта в устройстве синхронизации и коммутации ………………...….............…………..…..........................44

3.4. Выводы……………………………………………………………................48

Заключение …………………………………………………………………………..........50

Список использованныхисточников……………………………………….....................51

ВВЕДЕНИЕ

Создание технологических систем промышленности в настоящее время невозможно без доминирующей части микроэлектроники, роль которой неуклонно повышается не только на стадии производства изделий в их конструкции, но и в технологических системах проектирования.

В данной работепредставленаразработка и исследование технологического маршрута создания n - и p -канальных МОП-транзисторов в составе КМОП-структуры.

Составлен эскиз конструкции КМОП-структуры и разработан технологический маршрут ее изготовления. Кроме того, приложены поясняющие иллюстрации с приведенными поперечными сечениями структур базовых элементов на ключевых этапах изготовления.

Для разработки интегрального прибора требуется выполнить логическое, схемотехническое и топологическое проектирование [1].

В данной работе рассмотрен делитель частоты с переменным коэффициентом деления {7, 14, 16, 23}на основе JK-триггера.

Также в работе рассмотрен вопрос поиска эффективных решений и методов защиты от тиристорного эффекта (ТЭ)в современных микроэлектронных устройствах, радиоэлектронной аппаратуре (РЭА) двойного и специального назначения, а в частности в устройстве синхронизации и коммутации.

Обеспечение стабильной и надежной работы частей аппаратуры, входящей в радиолокационный комплекс имеет высокий приоритет, так как к ней предъявляются повышенные требования к безопасному и стабильному функционированию.

При постановке и решении задач необходимо обеспечить полную защиту аппаратуры от отказов, которые вызваны ТЭ, учитывать потребность реализации устройства защиты от ТЭ с высоким быстродействием и малыми массогабаритными характеристиками, а также исключение несанкционированных отключений электропитания при отсутствии воздействующих факторов.

ТЕХНИЧЕСКОЕ ЗАДАНИЕ

По техническому заданию необходимо разработать:делитель частоты с переменным коэффициентом деления {7, 14, 16, 23} на основе JK-триггера; технологический маршрут создания n - и p -канальных МОП-транзисторов в составе КМОП-структуры.Необходимые параметры представлены в таблице 1.

Таблица 1–Параметры технического задания

| № | Параметр ТЗ | Значение |

| Логический базис | И-НЕ | |

| Технологический базис | CMOS-035um | |

| Время фронта и среза, tфр.ср, нс | ||

| Рабочая частота по входному сигналу, fраб, МГц | ||

| Нагрузочная емкость, Сн, пФ | 1,5 | |

| Напряжение питания, Vdd, В | 3,5 | |

| Технологические параметры для расчетов | ||

| Пороговое напряжение n-МДПТ, Vtn, В | 0,6 | |

| Пороговое напряжение p-МДПТ, Vtp, В | -0,6 | |

| Удельная крутизна n-МДПТ, K0n, мкА/В2 | ||

| Удельная крутизна p-МДПТ, K0p, мкА/В2 | ||

| Толщина подзатворного окисла, tox, нм | ||

| Толщина межслойного окисла, hox, мкм | ||

| Концентрация примеси в подложке | N п = 1015 см−3 | |

| Концентрация примеси в n +- и p +-Si* затворе | N з = 1020 см−3 | |

| Плотность поверхностных состояний границы Si/SiO2 | Nss=3·1010 см−2 | |

| Относительная проницаемость Si | ε = 11,9 | |

| Относительная проницаемость SiO2 | ε d = 3,4 | |

| Мин. размер λ, мкм | 0,2 | |

| Tpoly, мкм | 0,3 | |

| Xjnwell, мкм | 1,5 | |

| Тип затвора и кармана | n+, p+; Nкарм = 9·1016 | |

| Тип изоляции | LOCOS |

ГЛАВА 1. ПРОЕКТИРОВАНИЕ ДЕЛИТЕЛЯ ЧАСТОТЫ

1.1. ЛОГИЧЕСКОЕ ПРОЕКТИРОВАНИЕ

JK-триггер (J – jump, K – kill) имеет 2 входа. Его таблица истинности представлена в таблице 2.

Таблица 2 - таблица истиностиJK-триггера

| J | K | Qn | Q(n+1) |

| X | Qn | ||

| NQn |

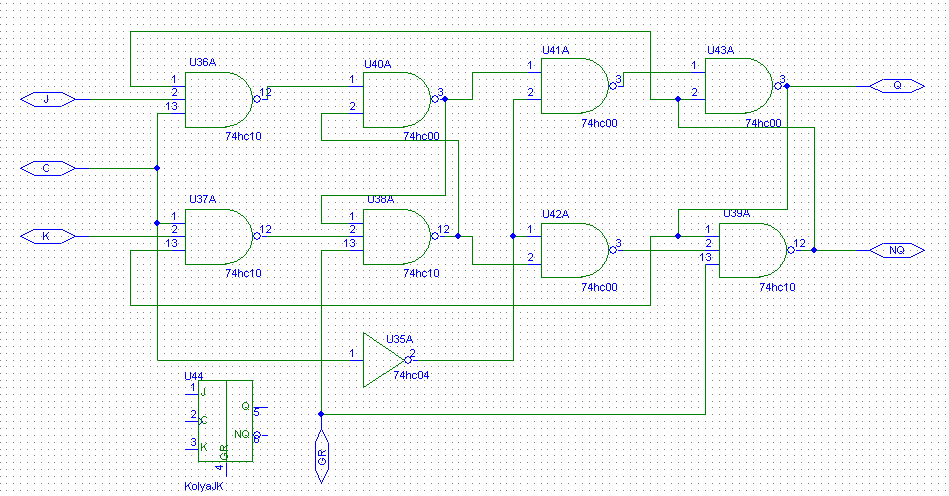

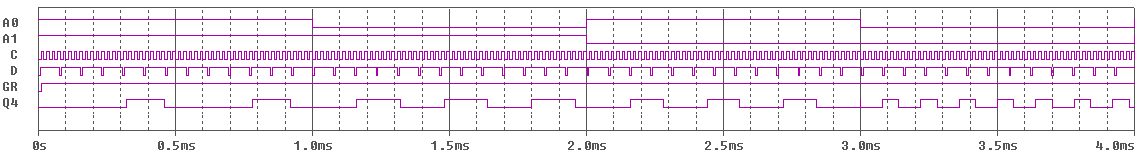

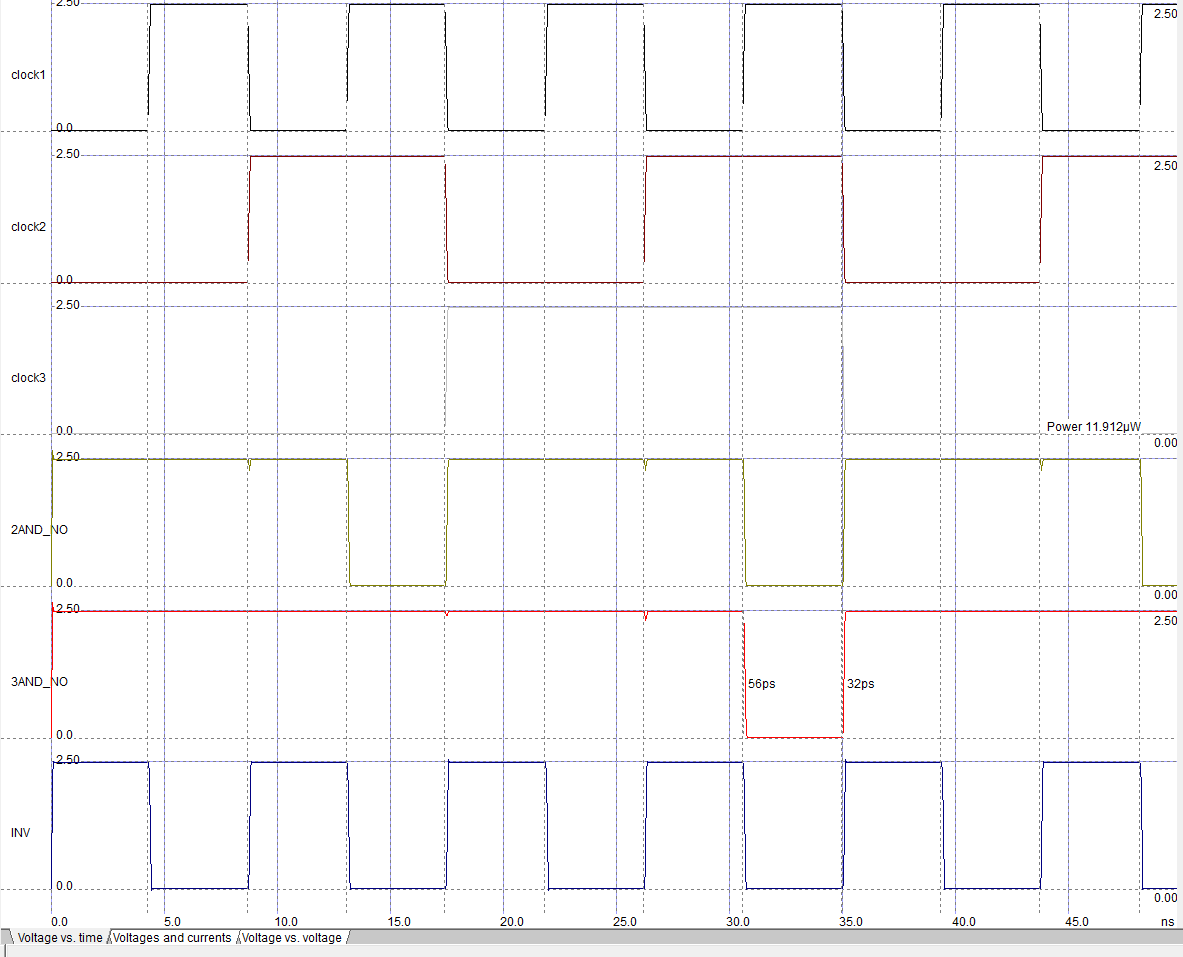

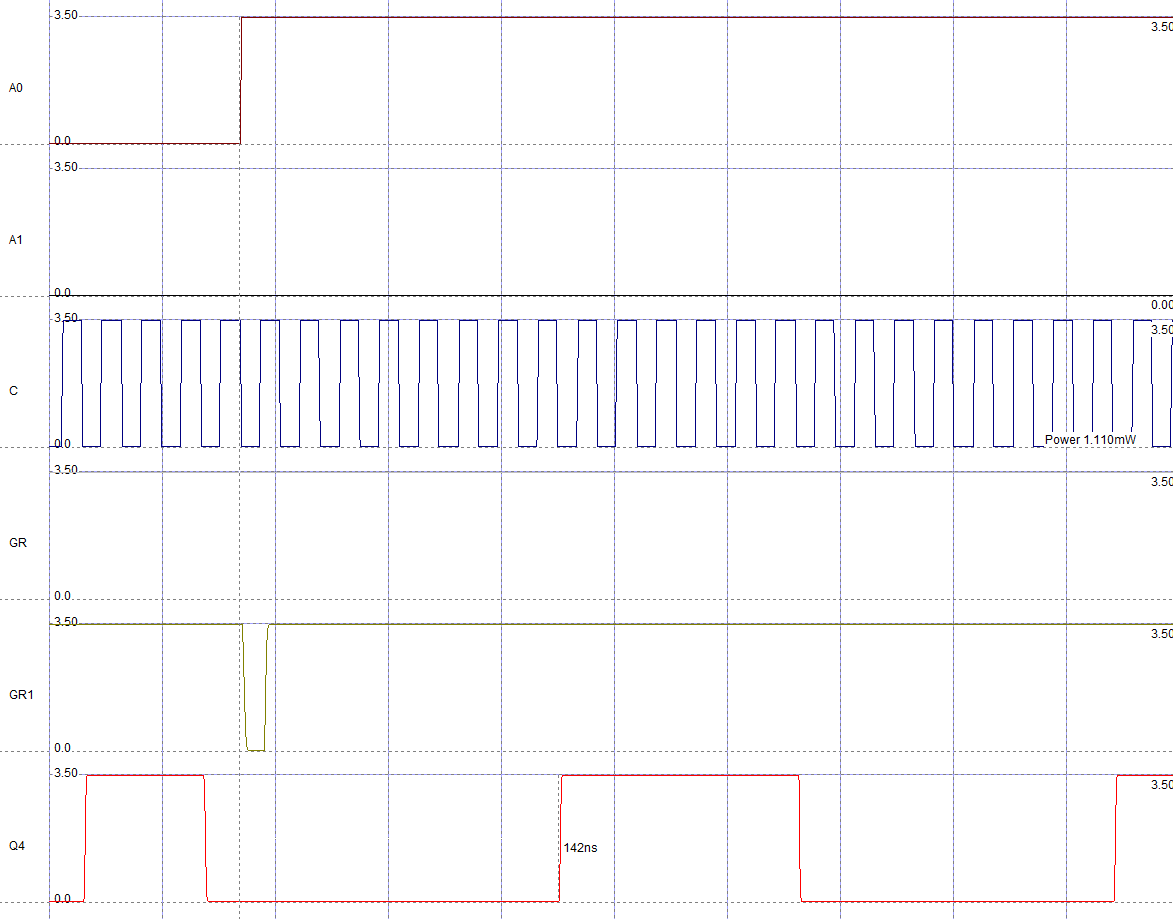

В данной работе используется динамический JK-триггер, реализованный посредством добавления тактового сигнала C – clock. А также, для того чтобы в начальный момент времени триггер принимал нулевое значение, в схему добавлен «сбрасывающий сигнал» GR – globalreset. Моделирование реализации разработанного триггера представлена на рисунке 1.1.

Рис. 1.1 - Временные диаграммы динамического JK-триггера

Рис. 1.2 - Схема динамического JK-триггера и его условное обозначение

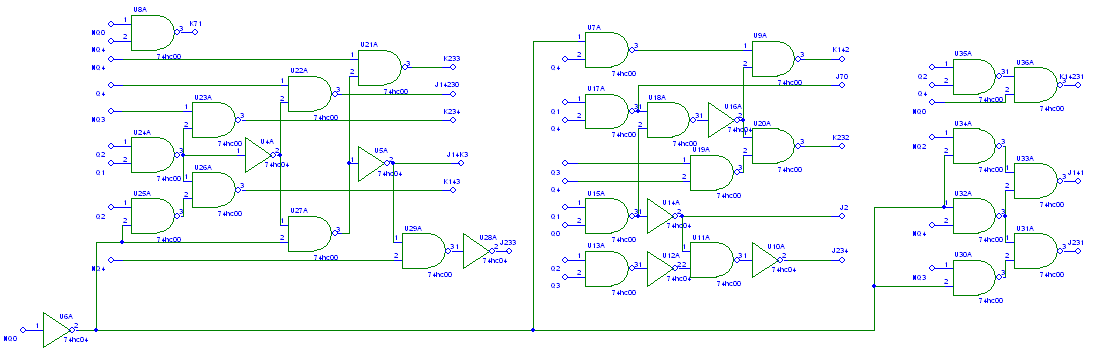

В данной работе неполный счетчик, а именно счетчик с модулем счета 7, 14, 16, 23 на основе JK-триггера. Для этого составлялись таблицы переходов, преобразовывались методом карт Карно и реализовались на элементах И-НЕ. На рисунке 1.3 приведена логическая обвязка для каждого из счетчиков.

Рис. 1.3 - Схема логической обвязки для счетчиков с модулем счета 7, 14, 16, 23 на основе JK-триггера

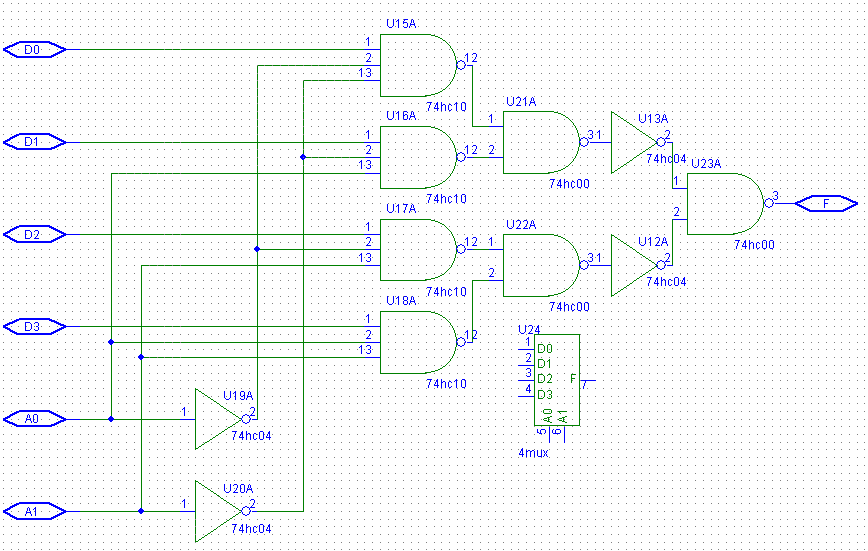

Мультиплексор – комбинационная схема, имеющая N адресных входов, 2N возможных информационных входов и один выход. В зависимости от адресного сигнала, на выход поступает один из информационных входов. (рисунок 1.4).

Рис. 1.4 - Схема мультиплексора 4 в 1 и его условное графическое обозначение

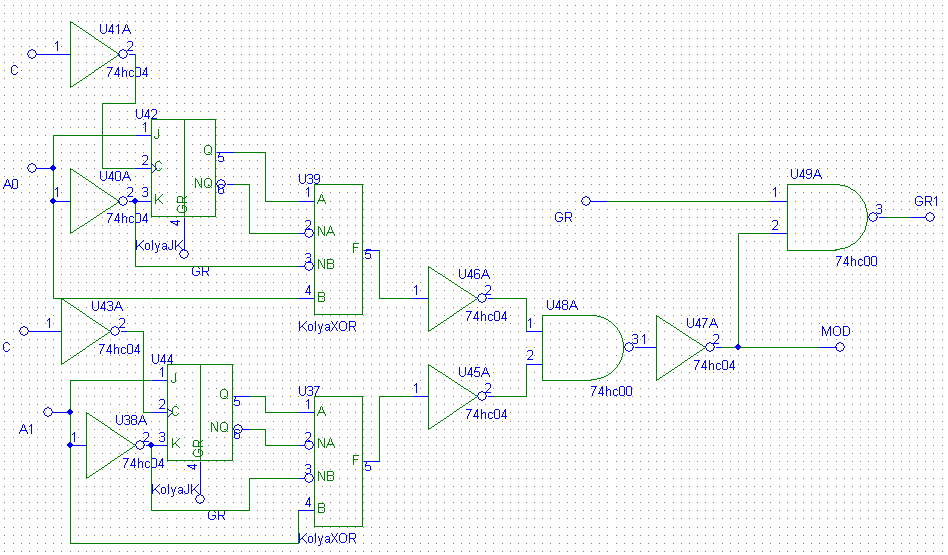

При переключении режима устройства возникает необходимость сброса регистра и счетчика в нуль для того, чтобы на выходах не возникало недопустимых состояний. Данный сброс реализуется с помощью детектора переключения режима, который реализуется на основе D-триггера с обратным фронтом, связанного дизъюнкцией с общим первоначальным сбросом. (Рисунок 1.5).

Рис. 1.5 - Схема детектора переключения режима

Делитель частоты - электронное устройство, уменьшающее в целое число раз частоту подводимых к нему периодических колебаний. Для создания схемы делителя частоты с переменным коэффициентом деления необходимо реализовать счетчик с переменным модулем счета. Выбор модуля счета определяется входными сигналами режима (A0, A1). В зависимости от режима на управляющие входы триггеров подается соответствующая функция, для этого используется мультиплексор 4 в 1. При переключении [A1, A0] происходит сброс счетчика в начальное состояние, путем использования детектора изменения режима и объединения его выхода с сигналом общего сброса.

Цель курсового проекта – делитель частоты с переменным коэффициентом деления {7, 14, 16, 23} на основе JK-триггера. Логический базис устройства – И-НЕ, соответственно, комбинационные схемы проектируются только на элементах 2И-НЕ, 3И-НЕ и НЕ библиотеки 74hc.Делитель частоты с переменным коэффициентом деления (рисунок 1.6).Результат моделирования данной схемы представлен на рисунке 1.7.

Рис. 1.6 - Общая схема устройства

Рис. 1.7 - Результат моделирования 9-канального распределителя пар импульсов

Итоговая схема устройства содержит:

· НЕ – 52 элементов;

· 2И-НЕ – 81 элемент;

· 3И-НЕ – 3 элементов;

Максимальная длина пути Nсх=15.

Максимальное разветвление Mсх=9.

1.2. СХЕМОТЕХНИЧЕСКОЕ ПРОЕКТИРОВАНИЕ

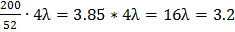

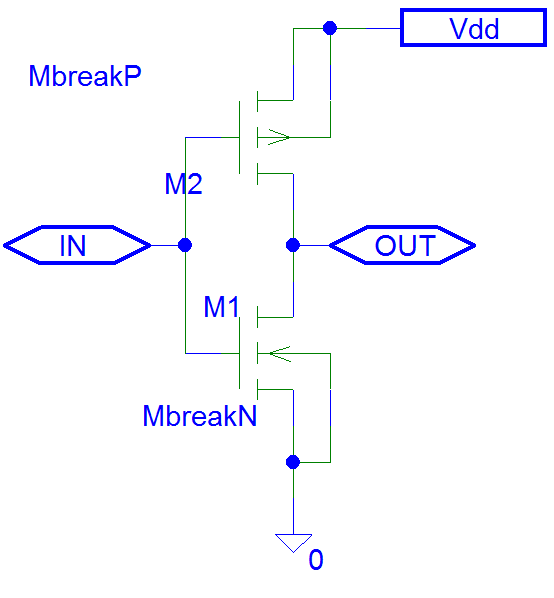

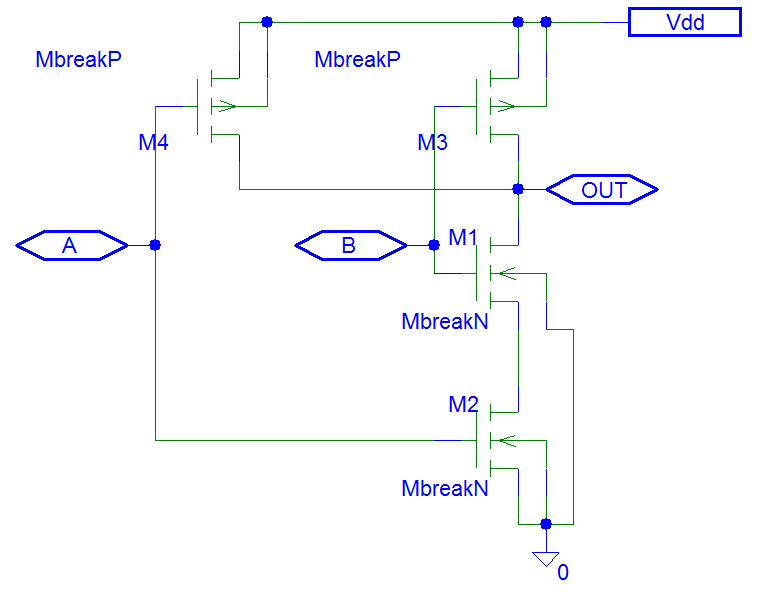

Базовые вентили

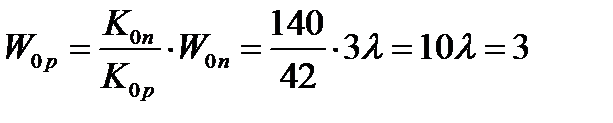

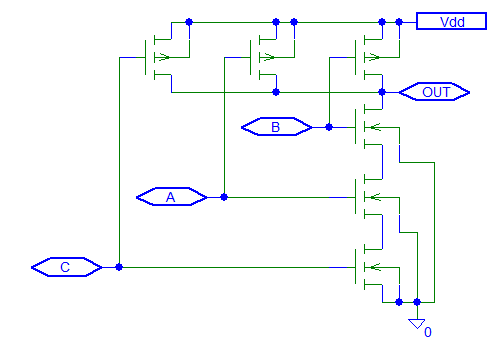

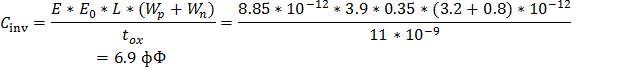

Согласно технологииCMOS-0.35 um ширины транзисторов базовых вентилей: L=0.35 мкм;  0.2 мкм

0.2 мкм

Минимальные ширины транзисторов в базовом инверторе:

W0n= 4  0.8 мкм;

0.8 мкм;

мкм

мкм

| Текст модели p-канального транзистора | Текст модели n-канального транзистора |

| .model Mbreakp PMOS LEVEL=3 VTO=-0.60 KP=52.000E-6 LD =-0.050U THETA=0.300 GAMMA=0.400 PHI=0.700 KAPPA=0.010 VMAX=100.00K CGSO= 10.0p CGDO= 10.0p TOX=7n *$ | .model Mbreakn NMOS LEVEL=3 VTO=0.60 KP=200.000E-6 LD =-0.050U THETA=0.300 GAMMA=0.400 PHI=0.700 KAPPA=0.010 VMAX=130.00K CGSO= 10.0p CGDO= 10.0p TOX=7n *$ |

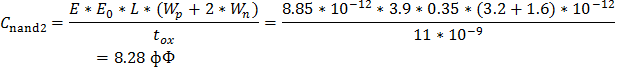

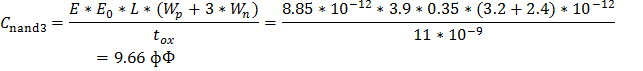

Ширины n-канальных транзисторов в базовом вентиле 2И-НЕ увеличиваются в 2 раза, т.е. Wn= 1.6 мкм, в базовом вентиле. В 3И-НЕ увеличиваются в 3 раза, т.е. Wn= 2.4 мкм

Используя полученные данные, собираются базовые вентили на транзисторах с минимальными ширинами и создаются библиотеки. Полученные схемы представлены на рисунке1.8.

а) б)

в)

Рис. 1.8 - Электрическая схема инвертора (а),элемента 2И-НЕ (б) и

элемента 3И-НЕ (в)

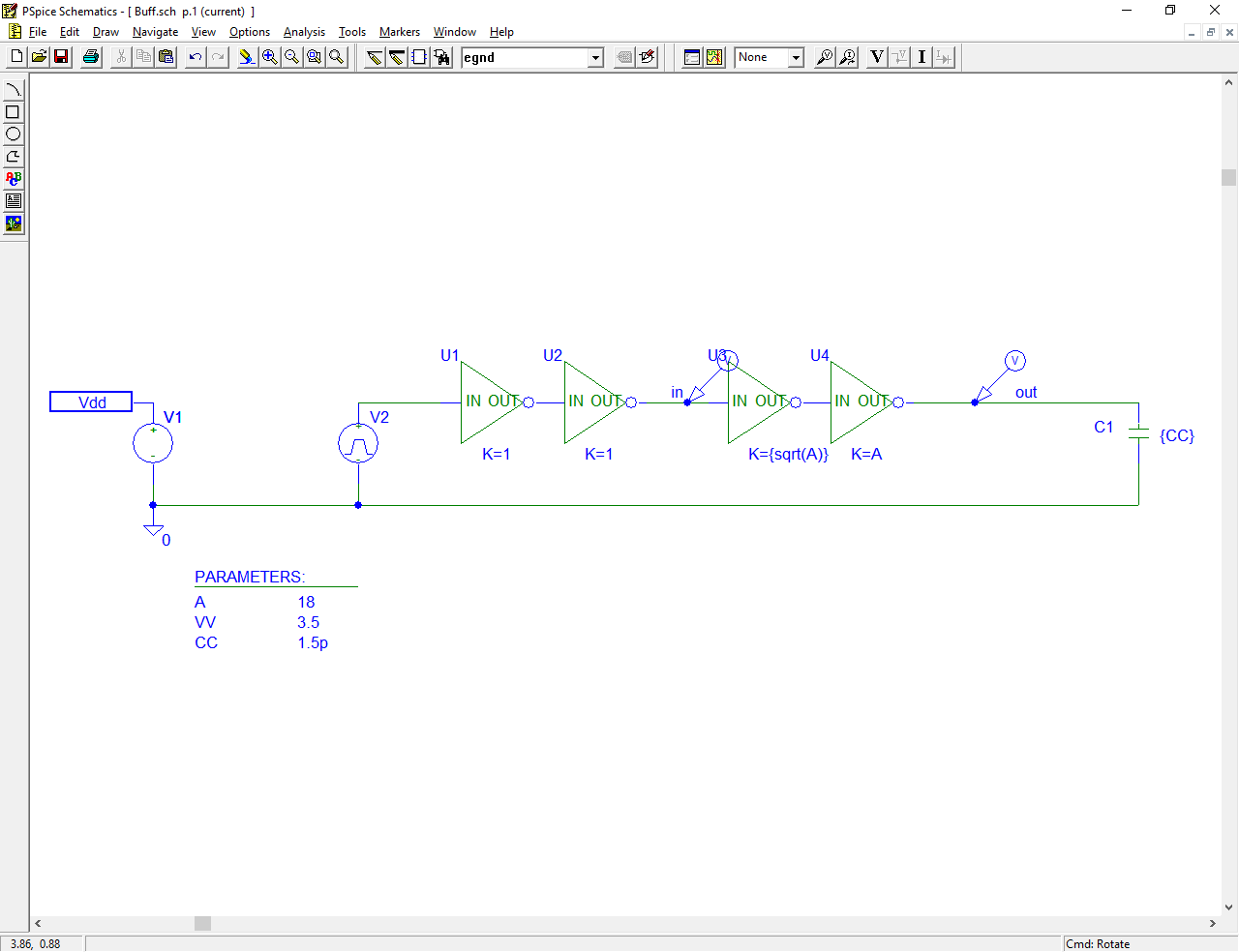

Буферный элемент

Чтобы обеспечить заданное по ТЗ быстродействие при работе схемы на большую выходную нагрузочную ёмкость, необходимо рассчитать параметры буферного элемента. Для этого собирается схема буферного элемента (рис. 1.9) и осуществляется параметрическое моделирование данной схемы (рис. 1.10).

Рис. 1.9 - Схема моделирования буферного элемента

При моделировании необходимо увеличивать размеры транзисторов в буферном элементе до тех пор, пока фронт и срез выходного сигнала не станут удовлетворять требованиям ТЗ.

По ТЗ tфр,ср = 1 нс, поэтому из рисунка 1.10 было выбрано удовлетворяющее ему значение параметра A = 18. Далее для найденного параметра A = 9 измерены динамические характеристики буферного элемента.

Рис. 1.10 - Результаты параметрического моделирования буферного элемента

Далее проводится параметрический анализ схемы моделирования буферного элемента (рис. 1.11 и 1.12), чтобы определить минимальное напряжение питания и максимальную нагрузочную ёмкость, при которых еще выполняется требование ТЗ по времени фронта и среза.

Рис. 1.11 - Результат параметрического моделирования буферного элемента по напряжению питания

Рис. 1.12 - Результат параметрического моделирования буферного элемента по нагрузочной ёмкости

Из рис. 1.11и 1.12 видно, что минимальное напряжение питания равно Vdd min= 3.3 В, а максимальная нагрузочная ёмкость равна СH max= 1.547 пФ

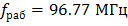

Кольцевой генератор

Для того, чтобы определить нагрузочную способность всех вентилей, можно воспользоваться методом построения кольцевого генератора. Схема моделирующая «лучший» случай, состоит из последовательно подключенных инверторов, количество которых определяется значением максимального пути. Схема моделирующая «худший» случай, состоит из нагруженных и последовательно подключенных инверторов, количество которых определяется значением максимального пути. В данном проекте максимальный путь в устройстве равен N max = 15,максимальный коэффициент разветвления по выходу – M сх = 9. Схемы моделирования кольцевых генераторовпредставлены на рис.1.13, а результат её моделирования на рис.1.14.

Видно, что M max = 5, при M сх = 5, рабочая частота составляет  , а M max >> M сх, тогда T = 1/ f раб = 1/(96.77*106)=10.7 нс

, а M max >> M сх, тогда T = 1/ f раб = 1/(96.77*106)=10.7 нс

| б) |

| а) |

Рис. 1.13 - Схема моделирования кольцевых генераторов: а) «лучший» случай;

б) «худший» случай

Рис. 1.14 - Результат моделирования кольцевых генераторов.

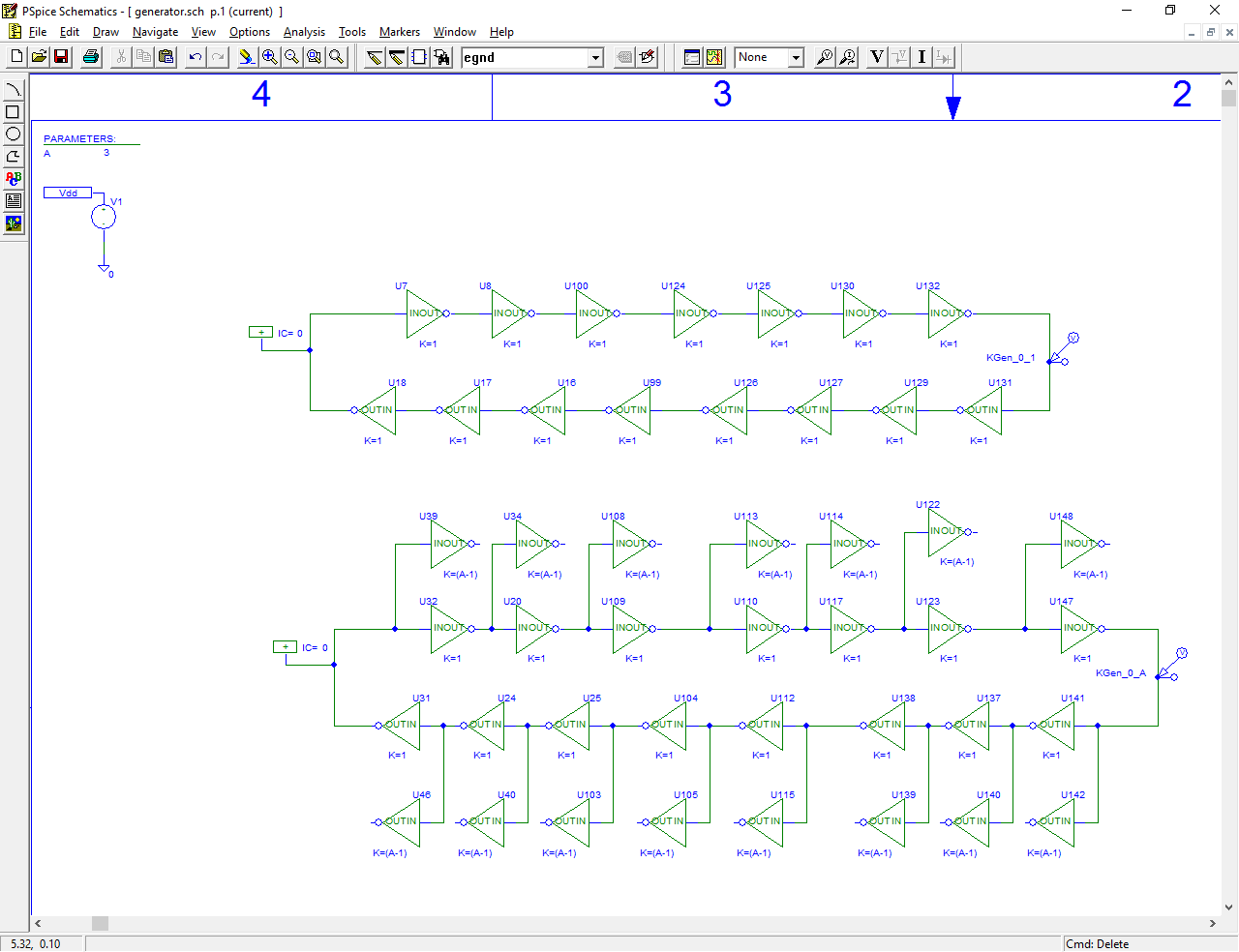

Динамические характеристики вентилей

Электрическая схема для моделирования вентилей приведена на рисунке 1.15. Вентили подключаются по схеме худшего случая по крутизне. В таблицу 3занесены динамические характеристики логических элементов, полученные в результате их моделирования.

Рис. 1.15 - Схема моделирования логических элементов

Таблица 3. Результаты измерения динамических характеристик логических элементов

| Логич. эл-ты | t фр, нс | t ср, н с | t зд01, н с | t зд10, н с | t зд ср, н с | Нагрузка |

| Инвертор | 0.499 | 0.427 | 0.311 | 0.217 | 0.264 | M =5 |

| 2И-НЕ | 0.532 | 0.341 | 0.343 | 0.163 | 0.253 | |

| 3И-НЕ | 0.551 | 0.331 | 0.371 | 0.149 | 0.260 | |

| Буфер | 0.971 | 0.850 | 0.763 | 1.022 | 0.893 | Cн=1.5p |

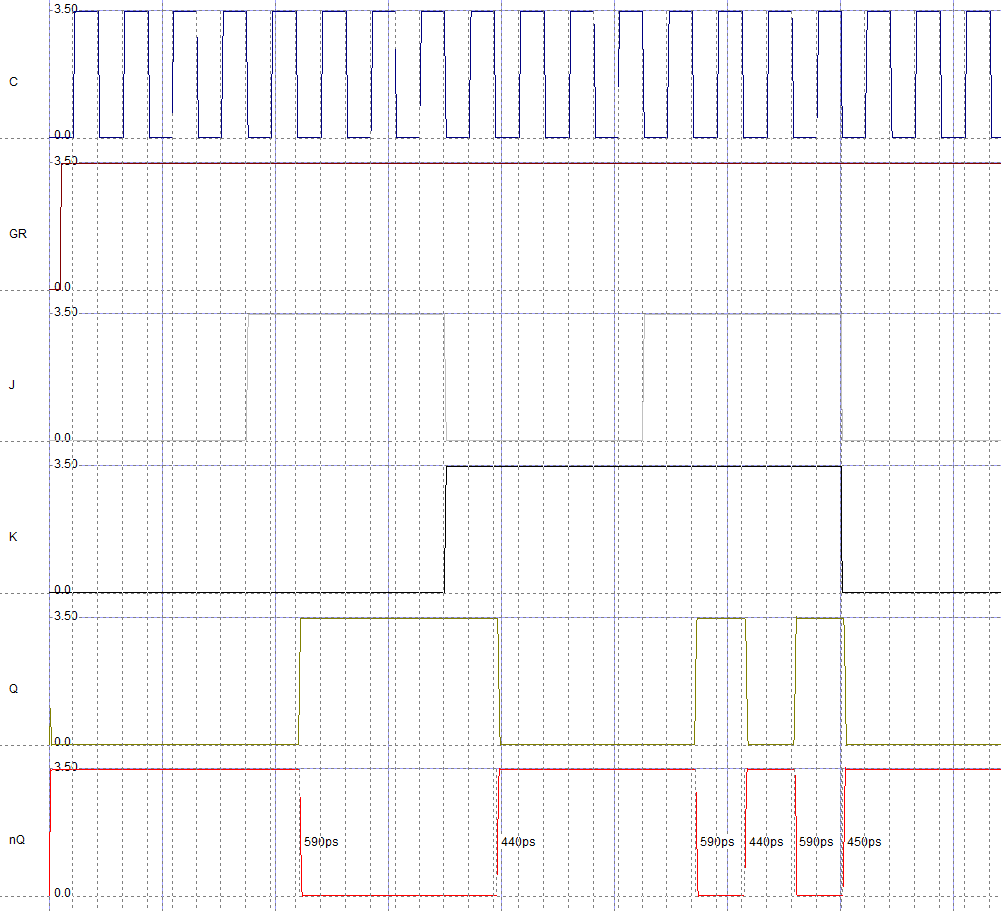

Полная схема устройства

На основе раннее созданных элементов, собирается общая схема устройства, с учетом буферных элементов и емкостей. Схема представлена на рис. 1.16, а результат моделирования на рис. 1.17.

Рис. 1.16 - Полная схема устройства с учетом буферных элементов

и нагрузочных ёмкостей

Рис. 1.17 - Результат моделирования полной схемы устройства

После схемотехнического моделирования необходимо провести расчёт средней потребляемой мощности в устройстве. Результат моделирования изображен на рисунке 1.18.

Рисунок 1.18 – Средняя мощность устройства

Из рисунка1.18видно, что в конце моделирования средняя мощность принимает значение Р ср = 1.56 мВт

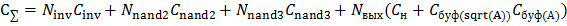

Для оценочного расчёта потребляемой мощности можно воспользоваться формулой:

,

,

где

= 52;

= 52;  = 81;

= 81;  = 54;

= 54;  = 1;

= 1;

Тогда: Р потр = 3.15 мВт

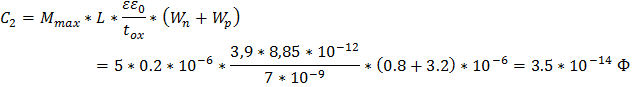

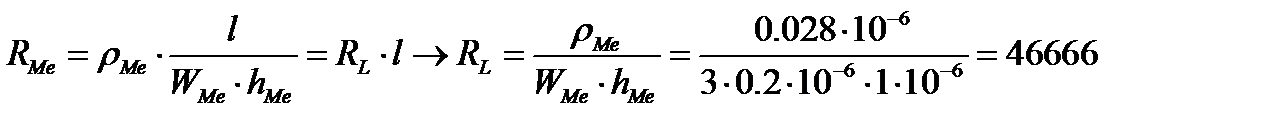

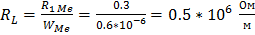

Перед проектированием топологии компонентов и всего устройства необходимо произвести расчет максимально допустимой в заданном технологическом базисе длины межсоединений.

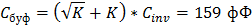

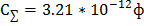

Далее необходимо найти постоянную времени в цепи из двух логических элементов по формуле:

,

,

где R 1 – выходное сопротивление логического элемента 1 и С 2 – входная емкость логического элемента 2.

С учетом задержки в межсоединении она равна:

,

,

где R Me и С Me - сопротивление и емкость дорожки соединения между двумя логическими элементами.

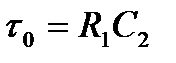

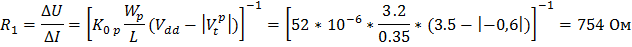

Выходное сопротивление логического элемента можно приближенно оценить по формуле

т.к. основная часть переходного процесса идет в крутой области работы МДП-транзистора [2].

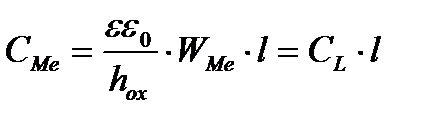

Входная емкость равна:

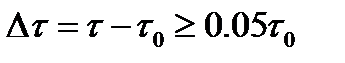

Влияние паразитных сопротивления и ёмкости дорожек металлизации существенно если  , или

, или

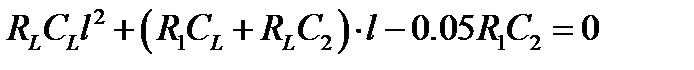

Таким образом,для нахождения максимально допустимой длины участка межсоединений, влиянием которого на задержку распространения сигнала можно пренебречь, требуется решить уравнение:

,

,

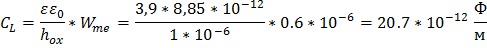

Удельная паразитная ёмкость вычисляется по формуле плоского конденсатора

,

,

Сопротивление дорожки металлизации вычисляется по формуле:

(1)

(1)

Но, т.к. квадратный участок металлизации имеет одинаковое сопротивление при любой длине его сторон, то используют величину удельного сопротивления слоя R 0, измеряемую в единицах Ом/□.

(2)

(2)

Величина  сильно отличается в уравнениях (1) и (2). Значит необходимо выбрать значение из уравнения (2). Далее нужно решить квадратное уравнение:

сильно отличается в уравнениях (1) и (2). Значит необходимо выбрать значение из уравнения (2). Далее нужно решить квадратное уравнение:

,

,

D=R12CL2+RL2C22+2,2R1CLRLC2 = (754)2*(20.7*10-12)2+(0.5*106)2*

*(3.5*10-14)2+2,2*754*20.7*10-12*0.5*106*3.5*10-14=

=11.35*10-16 (Ом2*Ф2)/м2

тогда, максимальная длина шины разводки, будет равна

- максимальнаядопустимая длина межсоединений в данном технологическом базисе.

- максимальнаядопустимая длина межсоединений в данном технологическом базисе.

Следовательно, удельная паразитная емкость cоставит:

CMe=CL*l=20.7*10-12*39*10-6=8.1*10-16 Ф

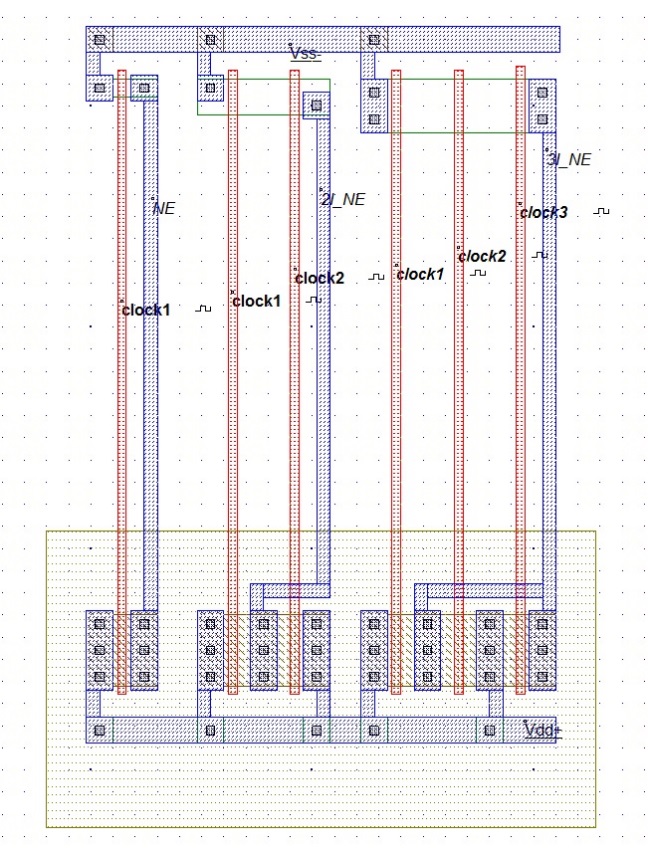

1.3. ТОПОЛОГИЧЕСКОЕ ПРОЕКТИРОВАНИЕ

Следующий этап разработки устройства – топологическое проектирование. На p-подложке требуется расположить спроектированные и промоделированные логические элементы НЕ, 2И-НЕ и 3И-НЕ (рисунок 1.19), затем последовательно сконструировать комбинационные схемы. При выполнении данного этапа следует придерживаться следующих общих требований:

· Уменьшение площади

· Выполнение правил проектирования топологии в заданном базисеCMOS-0.35um

а) б)

Рис. 1.19 - Топология (а)и результат моделирования (б)

логических элементов НЕ, 2И-НЕ и 3И-НЕ

Для обеспечения необходимого быстродействия устройства сформируем буферный элемент, согласно схемотехнической части. (Рисунок 1.20)

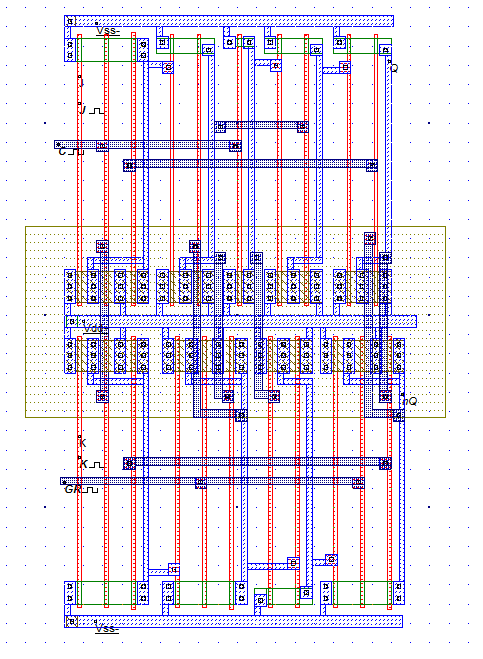

Соберем и промоделируем JK-триггер и полную схему устройства. (Рисунки 1.21-1.23)

а) б)

Рис. 1.20 - Топология (а) ирезультат моделирования (б)буферного элемента

а) б)

Рис. 1.21 - Топология (а) ирезультат моделирования (б) JK-триггера

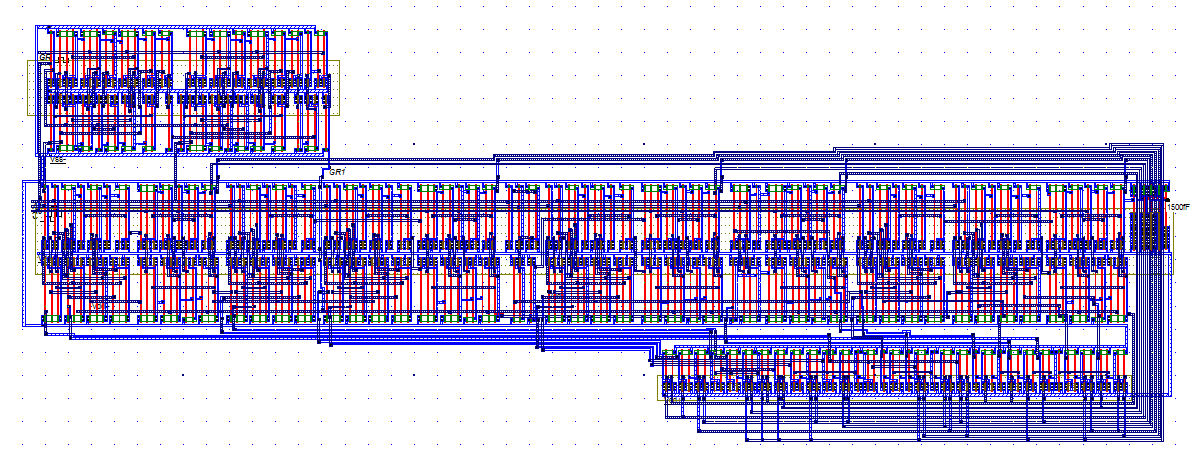

Рис. 1.22 -Топология полной схемы устройства

Рис. 1.23 - Результат моделирования полной схемы устройства

1.4. ВЫВОДЫ

В данном курсовом проекте было спроектировано устройство делитель частоты с переменным коэффициентом деления {7, 14, 16, 23} на основе JK-триггера. Логическое моделирование выполняет поставленную задачу.

Схемотехническое проектирование составлено на основе логического моделирования, и временные задержки на схеме соответствуют требованиям технического задания.

Топологическое проектирование сделано на основе схемотехнического моделирования и выполняет поставленную задачу. Максимальная длина провода составляет 1222 мкм. Влияние меж-соединений вносит существенный вклад на работу устройства, следовательно, данным влиянием пренебрегать не стоит и его следует включить в расчеты.

ГЛАВА 2. РАЗРАБОТКА И ИССЛЕДОВАНИЕ

ТЕХНОЛОГИЧЕСКОГО МАРШРУТА

2.1. ЭСКИЗ И МАРШРУТ СОЗДАНИЯ ТРАНЗИСТОРОВ

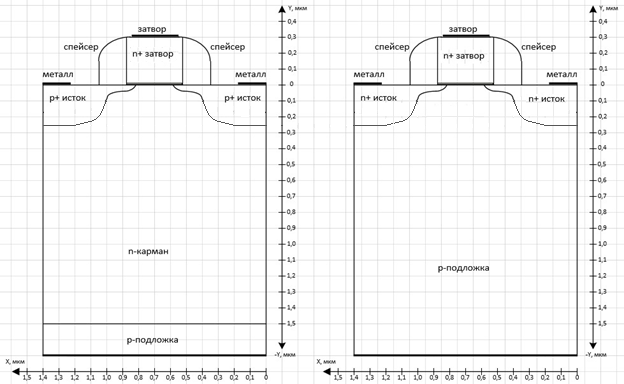

Эскиз конструкции КМОП-структуры с заданными в ТЗ типом изоляции, типом кармана и типом затвора представлен на рис. 2.1.

Рисунок 2.1 - Эскиз конструкции КМОП-структуры.

Технологический маршрут изготовления КМОП-структуры представляет собой последовательность технологических операций, необходимых для формирования интегральных n- и p-канальных транзисторов, области изоляции и металлизации.

Выбор подложки: p-тип, КДБ-12 (N = 1015 см−3), кристаллографическая ориентация поверхности (100).

| № | Технологическая операция | Режим обработки | Примечание |

| Окисление | 1000°С, 30 мин, О2 | ||

| Фотолитография “n-карман” | |||

| Имплантация | P, 80 кэВ, 5*  см-2 см-2

| ||

| Удаление фоторезиста | |||

| Отжиг | 30 мин, 1200°С, O2 | Разгонка карманов | |

| Отжиг | 90 мин, 1200°С, N2 | ||

| Удаление всего SiO2 | |||

| Окислениепод Si3N4 | 30мин, 950°С, О2 | 30-50 нм 150 нм | |

| Нанесение Si3N4 | |||

| Фотолитография “Маска под LOCOS” | |||

| ПХТ Si3N4 | |||

| Удаление фоторезиста | |||

| Фотолитография “p+-охрана” | |||

| Имплантация | B, 40 кэВ, 7.1013см-2 | ||

| Удаление фоторезиста | |||

| Отжиг p-охраны | 60 мин, 1050°С, N2 | ||

| Окисление LOCOS | 50 мин, 950°С, H2O | ||

| Удаление Si3N4 | |||

| Травление SiO2 | 200 Å | ||

| Окисление | 1000°С, О2 | ||

| Фотолитография “Подгонка порогового напряжения n-транзистора” | |||

| Имплантация | B, 30 кэВ, 1*  см-2 см-2

| ||

| Удаление фоторезиста | |||

| Фотолитография “Подгонка порогового напряжения p-транзистора” | |||

| Имплантация | P,30кэВ, 0.5*  см-2 см-2

| ||

| Удаление фоторезиста | |||

| Удаление SiO2до Si | |||

| Окисление под затвор | 30 мин, 900°С, O2 | 30-50 нм | |

| Нанесение n+-поликремния | P,1.2 мкм, 1020см-3 | ||

| Фотолитография “n+-затвор ” | |||

| ПХТ Si* на всю толщину до оксида | |||

| Удаление фоторезиста | |||

| Нанесение p+-поликремния | |||

| Фотолитография “p+-затвор ” | |||

| ПХТ Si* на всю толщину до оксида | |||

| Удаление фоторезиста | |||

| Фотолитография “n-LDD” | |||

| Имплантация | P, кэВ, см-2 | ||

| Удаление фоторезиста | |||

| Фотолитография “p-LDD” | |||

| Имплантация | B, кэВ, см-2 | ||

| Удаление фоторезиста | |||

| Создание спейсеров | |||

| Окисление | 20мин, 850°С, О2 | ||

| Фотолитография “n+-сток, исток, контакт к n-карману” | |||

| Имплантация | P, кэВ, см-2 | ||

| Удаление фоторезиста | |||

| Фотолитография “p+-сток, исток, контакт к p-подложке” | |||

| Имплантация | B, кэВ, см-2 | ||

| Удаление фоторезиста | |||

| Отжиг | 30мин, 900°С, О2 | ||

| Отжиг | 900°С, N2 | ||

| Нанесение межслойного диэлектрика | |||

| Фотолитография “Контактные окна” | |||

| ПХТ оксида | |||

| Удаление фоторезиста | |||

| Нанесение металла (Al-Si) | |||

| Фотолитография “Металлизация” | |||

| ПХТ алюминия на всю толщину | |||

| Удаление фоторезиста | |||

| Нанесение изолирующего слоя | |||

| Фотолитография “Контакт. площ.” | |||

| ПХТ оксида | |||

| Удаление фоторезиста |

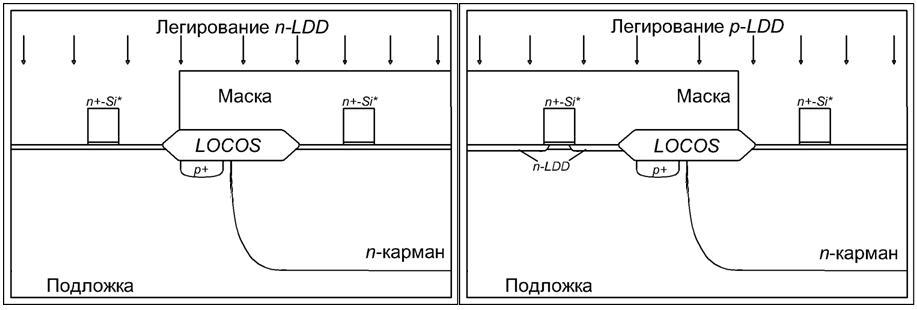

Далее на рис. 2.2-2.6 представлена эскизная маршрутная карта в виде последовательных модификаций поперечного сечения КМОП-структуры на этапах изготовления согласно приведенному в табл. 1.2 технологическому маршруту.

Рисунок 2.2 - Эскизы поперечного сечения КМОП-структуры

(операции № 1-8 и № 9-15 технологического маршрута)

Рисунок 2.3 - Эскизы поперечного сечения КМОП-структуры

(операции № 16-19 и № 20-26 технологического маршрута)

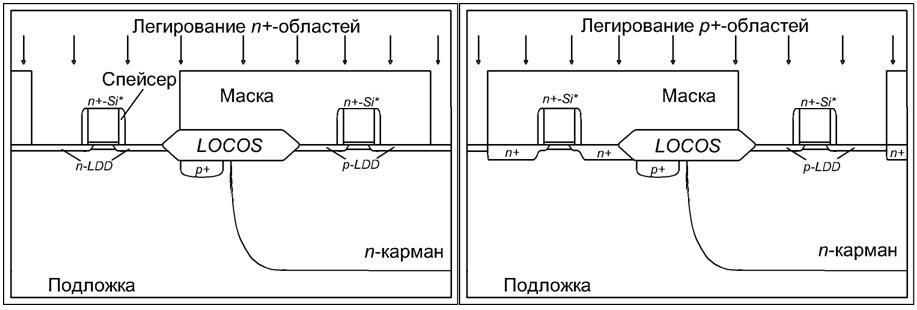

Рисунок 2.4 - Эскизы поперечного сечения КМОП-структуры

(операции № 27-39 и № 40-42 технологического маршрута)

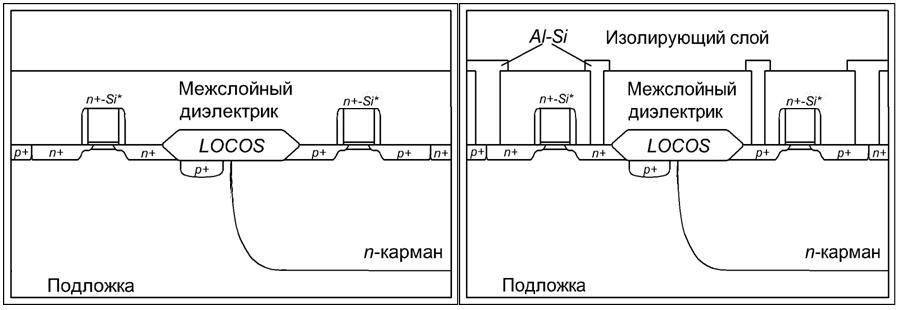

Рисунок 2.5 - Эскизы поперечного сечения КМОП-структуры

(операции № 43-47 и № 48-53 технологического маршрута)

Рисунок 2.6 - Эскизы поперечного сечения КМОП-структуры

(операции № 51-54 и № 54-64 технологического маршрута)

На рисунке 2.7 изображены масштабные эскизы p- и n-канальных транзисторов соответственно.

Рисунок 2.7 -Масштабные эскизы p- и n-канальных транзисторов.

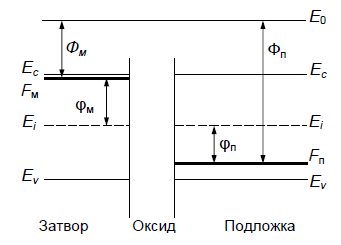

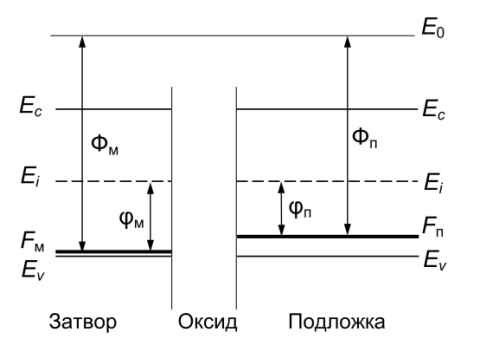

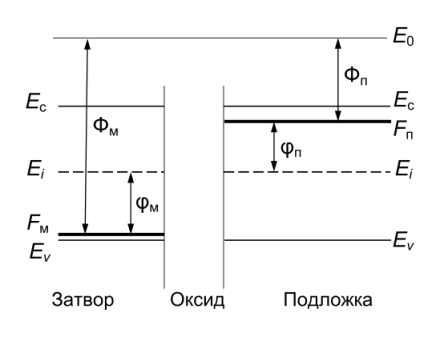

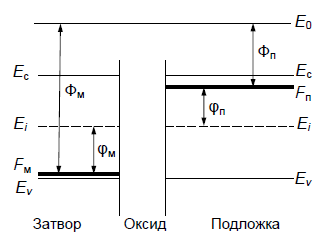

Для расчета порогового напряжения необходимо знать упрощенные зонные диаграммы МОП-структур.Варианты зонных диаграмм для n- иp-канальных транзисторов с n+и p+ затворами представлены на рисунках 2.8 – 2.9.

Рисунок 2.8 -n-МОП-структура с n+-Si* и p+-Si*-затвором.

Рисунок 2.9 -p-МОП-структура с n+-Si* и p+-Si*-затвором.

Расчеты ниже проводились с данными из ТЗ. Расчеты для n-МОП-транзистора с p+-Si*-затвором и для p-МОП-транзистора с n+-Si*-затвором не будут показаны.

Пороговое напряжение складывается из трех слагаемых – напряжений на трех слоях:

Uпор = Ugb + Ud + Ub. (3)

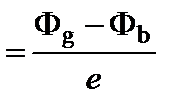

1) Первое слагаемое соотношения (3) определяет вклад материала затвора и подложки, и вычисляется как разность отрезков Фм и Фп, деленная на заряд электрона e:Ugb  ; Ugb = φg− φb.

; Ugb = φg− φb.

- для n-МОП-транзистора с n+-Si*-затвором: Ugb = –(φg+ φb)=-0..837 В;

- для n-МОП-транзистора с p+-Si*-затвором: Ugb = –(φg+ φb)=0.263 В;

- для p-МОП-транзистора с n+-Si*-затвором: Ugb = –(φg+ φb)=-0.146 В;

- для p-МОП-транзистора с p+-Si*-затвором: Ugb = φg+ φb= 0.954В;

Для сильнолегированного Si*-затвора (n+ или p+) уровень Ферми Fмпрактически совпадает с границей запрещенной зоны (Eс или Ev) и можно считать, что φg равен половине ширины запрещенной зоны: φg = 0,55 В.

Потенциал подложки φb для Si при T = 300 К зависит от концентрации примеси в подложке Nb и вычисляется как:

=0,2874 В.

=0,2874 В.

=0,404 В.

=0,404 В.

2) Второе слагаемое соотношения (3) описывает падение напряжения на оксидном слое:

=0,0213 (В) – для n-МОП-транзистора,

=0,0213 (В) – для n-МОП-транзистора,

=-0,3777 (В) – для p-МОП-транзистора,

=-0,3777 (В) – для p-МОП-транзистора,

где Qss= e · Nss,  =4,3*10-7,

=4,3*10-7,

Qsn= ± e·Nb(Nk) ·Lпор («−», «Nb» для n-канала; «+»,«Nk» для p-канала);

Qsn=-1,4005*10-8 (см-2)- для n-канала;Qsn=1,5749*10-7 (см-2) - для p-канала

=8,645*10-5(см),

=8,645*10-5(см),  =1,08*10-5 (см)

=1,08*10-5 (см)

3) Ub= ±2·φg («+» для n-канала; «−» для p-канала).

Ub=0,5748 В - для n-канала;Ub= - 0.807 В - для p-канала

Uпор = - 0,2413В – для n-МОП-транзистора с n+-затвором;

Uпор = - 0,2315В – для p-МОП-транзистора с р+-затвором

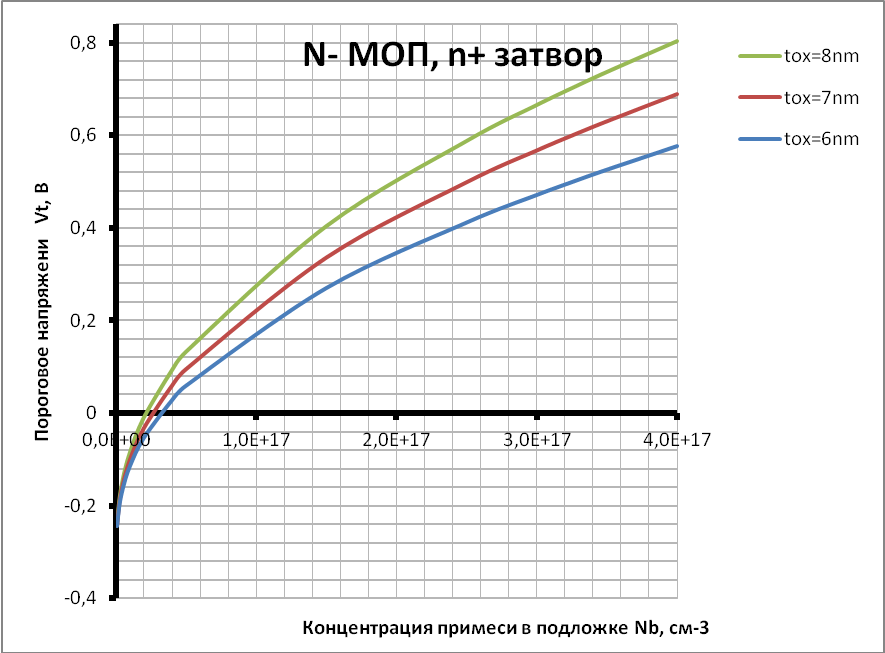

На рис. 2.10 показана зависимость Uпор (Nb, dок), рассчитанная для транзистора, изображенного на рис.3. Согласно примеру задания, для n-МОП-транзистора необходимо получить Uпор = 0,6 В. Как видно из рис.1.5.1, оптимальное значение концентрации примеси в подложке Nb = 3,25 · 1017 см−3; тип примеси – акцепторы (бор). Таким образом, необходимо провести корректировку порогового напряжения путем подлегирования поверхности подложки акцепторами (бором) до концентрации Nb = 3,25*1017 см−3 на глубину, приблизительно равную глубине залегания стока-истока Xjcи (глубина подлегирования может составлять 0,2 – 0,35 мкм).

Рис. 2.10 - Зависимость порогового напряжения n-МОП-транзистора

n+ затвором от концентрации примеси в подложке (в области канала)

и толщины подзатворного оксида.

При Dox=6 нм: N0=4.26*1017 см-3; Uпор=0.601 (В)

При Dox=7 нм: N0=3.25*1017 см-3; Uпор=0.6 (В)

При Dox=8 нм: N0=2.6*1017 см-3; Uпор=0.604 (В)

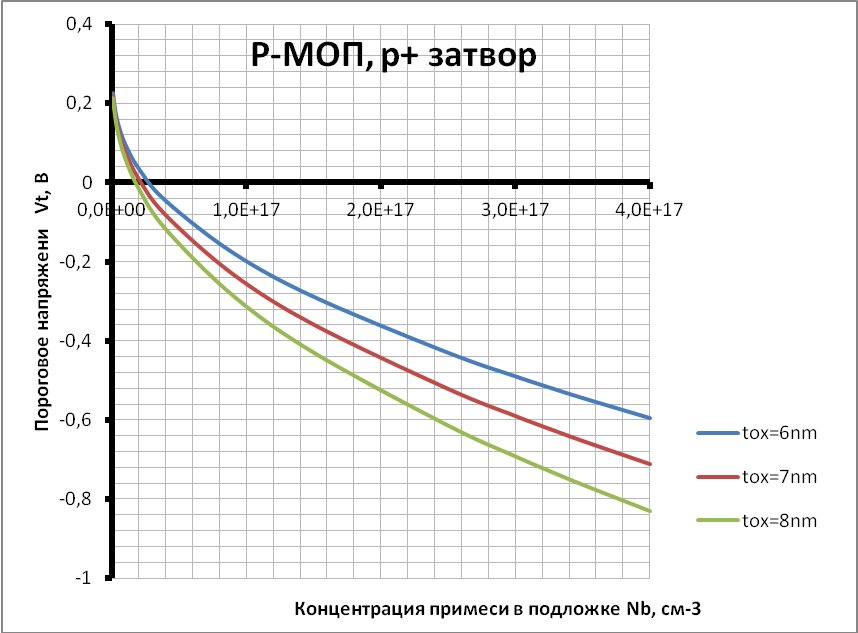

На рис. 2.11 показана зависимость Uпор (Nk, dок), рассчитанная для транзистора. Согласно примеру задания для p-МОП-транзистора необходимо получить Uпор = -0,6 В. Как видно из рисунка, оптимальное значение концентрации примеси в подложке Nk = 3,07· 1017 см−3; тип примеси – акцепторы (бор). Таким образом, необходимо провести корректировку порогового напряжения путем подлегирования поверхности подложки акцепторами (бором) до концентрации Nk = 3,07 · 1017 см−3 на глубину, приблизительно равную глубине залегания стока-истока Xjcи (глубина подлегирования может составлять 0,2 – 0,35 мкм).

Рис.2.11 - Зависимость порогового напряжения p-МОП-транзистора с

p+ затвором от концентрации примеси в подложке (в области канала)

и толщины подзатворного оксида.

При Dox=6 нм: N0=4.05 · 1017см-3; Uпор=-0.6 (В)

При Dox=7 нм: N0=3.07*1017 см-3; Uпор=-0.6 (В)

При Dox=8 нм: N0=2.42*1017 см-3; Uпор=-0.6 (В)

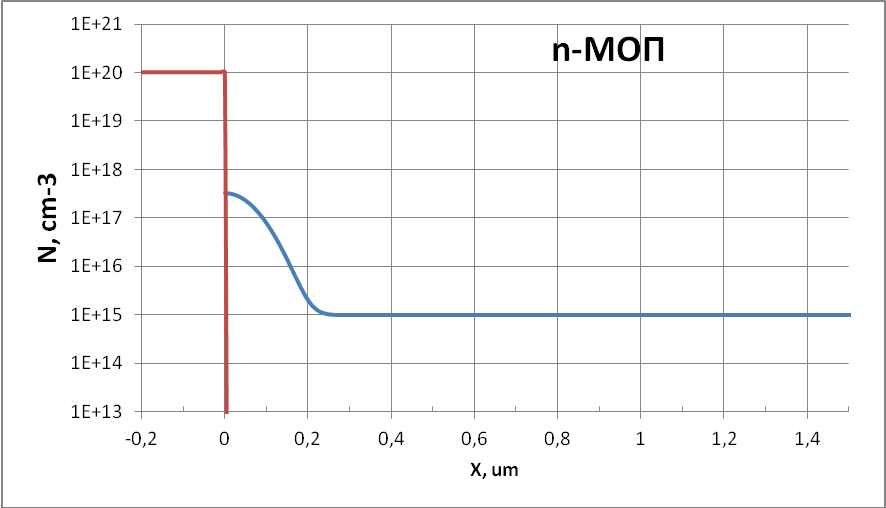

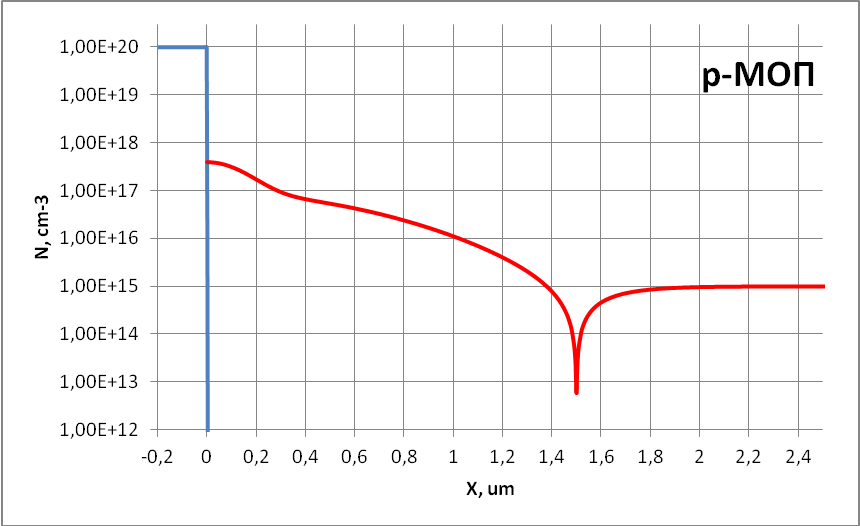

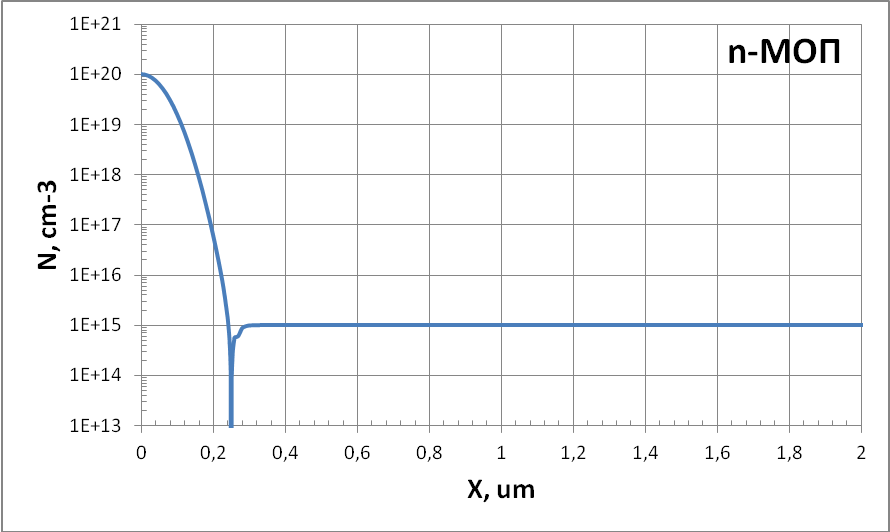

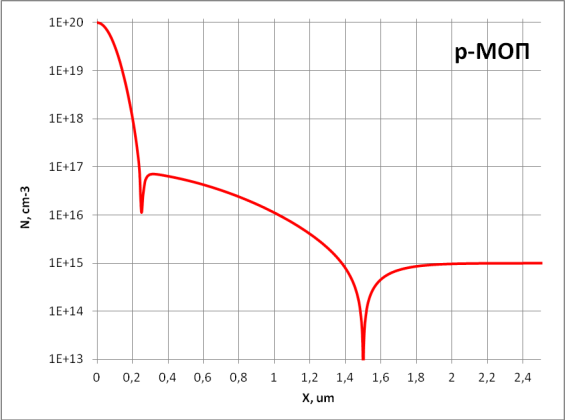

На основе проведенных предварительных расчетов, а также исходных данных разработаны эскизы распределений результирующей примеси в основных вертикальных сечениях транзисторов – сечении сток-исток (рисунок 2.12) и сечении затвор – подложка (рисунок 2.13).

Рис. 2.12 - Результирующее распределение примеси в области затвора в

n- и p- канальных транзисторах.

Рис. 2.13 - Результирующее распределение примеси в области сток-истока в

n- и p- канальных транзисторах.

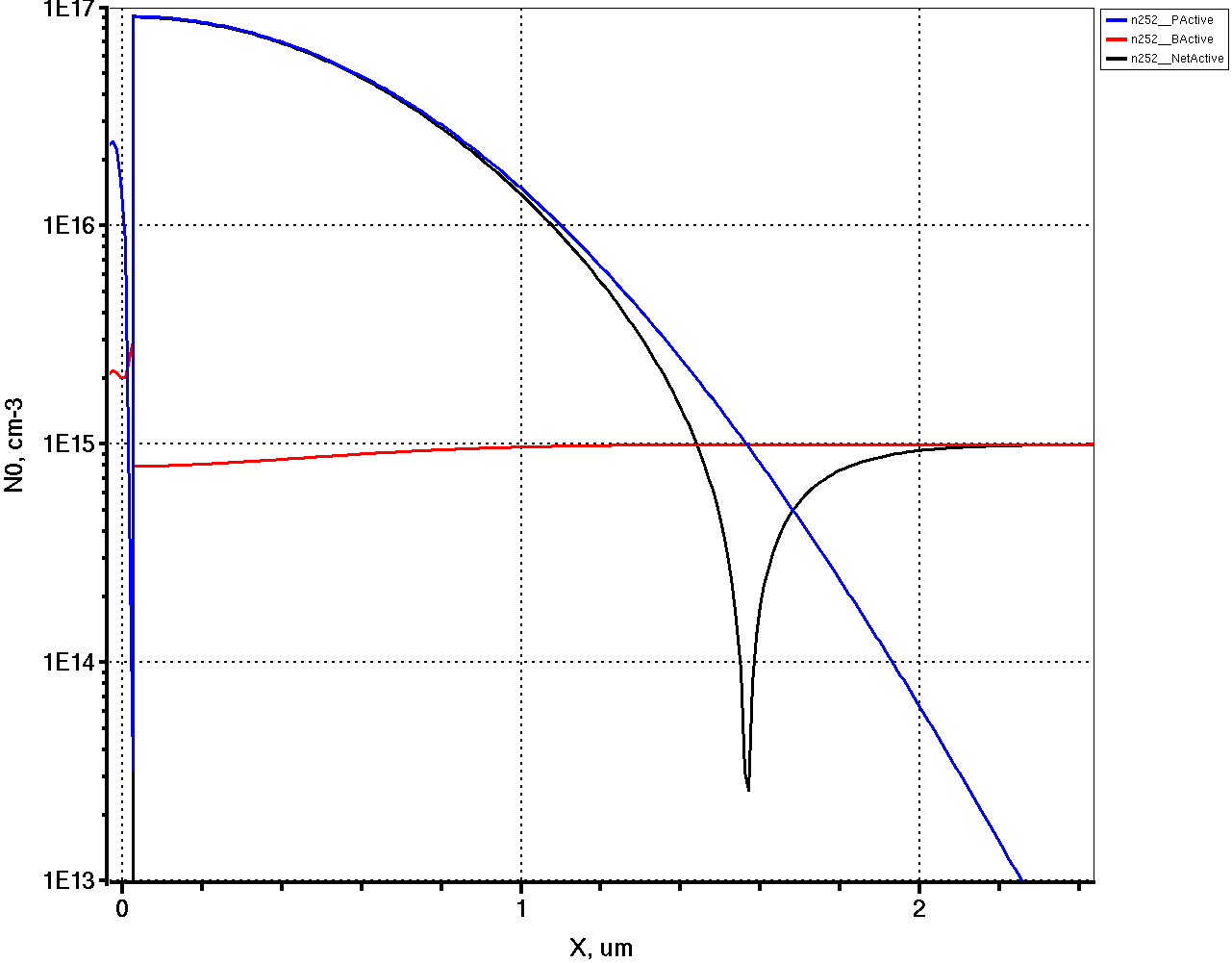

2.2.ОДНОМЕРНОЕ МОДЕЛИРОВАНИЕ

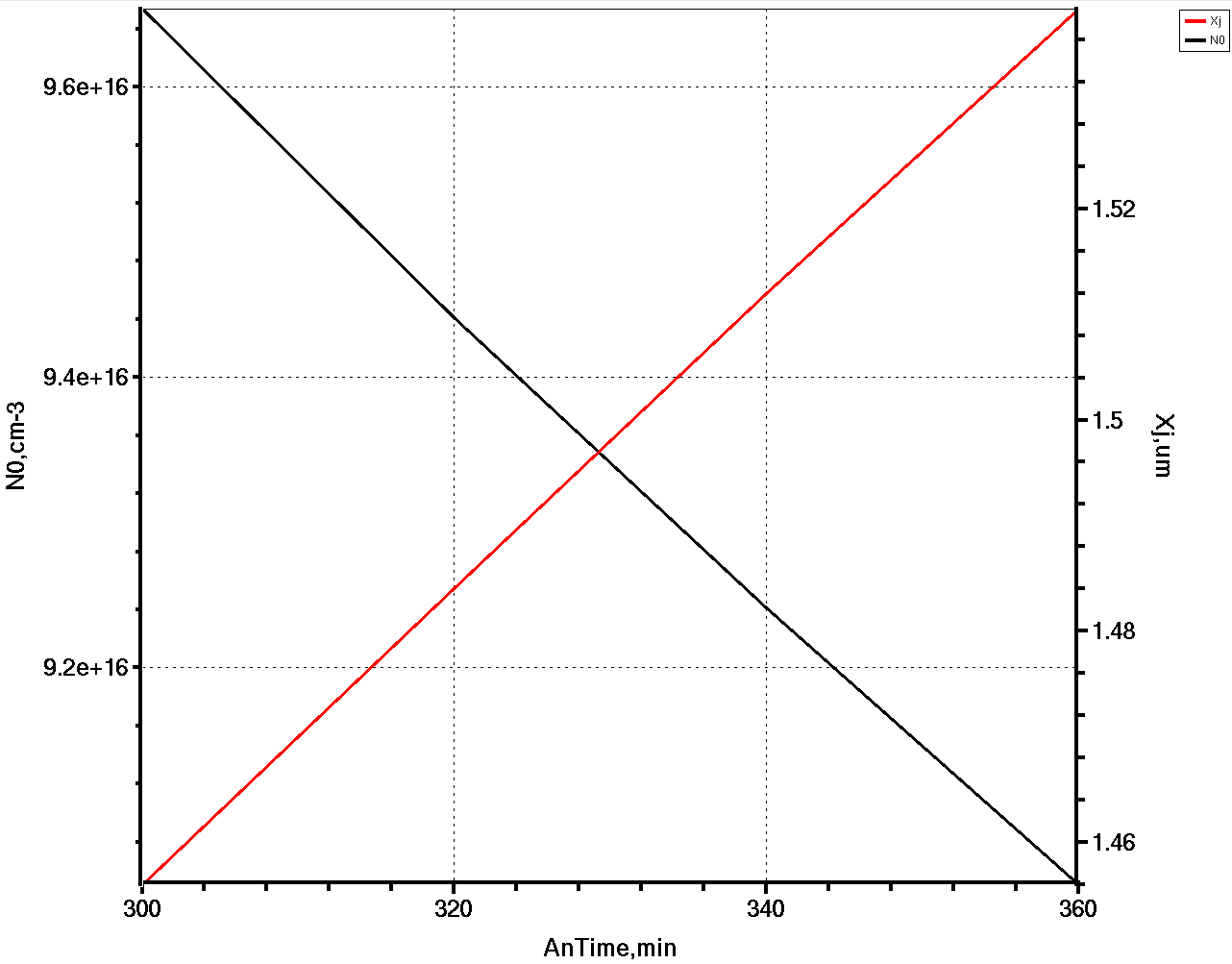

С помощью программы Tcade моделируем зависимость поверхностной концентрации примеси и глубины залегания n-кармана от времени отжига в нейтральной среде и расчетное распределение примеси в n-кармане (рис. 2.14).

а) б)

Рис. 2.14 - Зависимость поверхностной концентрации прим