Рисунок 1.1 Обобщённая структурная схема электронного усилителя

Рисунок 1.2 Принцип электронного усиления

| Eвых |

Рисунок 1.3 Схема источника напряжения управляемый напряжением

Рисунок 1.5 Схема источника тока управляемого током

Рисунок 1.4 Схема источника тока управляемого напряжением

Рисунок 1.6 Схема источника напряжения управляемый током

Рисунок 1.7 Амплитудно-частотная характеристика

Рисунок 1.8 Реальная и идеальная фазочастотная характеристика

Рисунок 1.9 Характеристики: а) - переходная; б) - динамическая; в) – амплитудная

Рисунок 1.10 Схема с фиксированным током базы

а)

Рисунок 1.11 Схема с фиксированным напряжением базы

б)

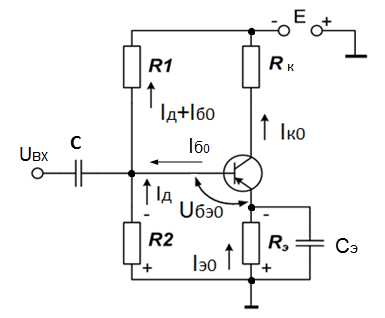

Рисунок 1.12 Схемы транзисторного каскада: а) с температурной коллекторной стабилизацией; б) с эмиттерной температурной стабилизацией

а) б)

Рисунок 1.13 Схемы обеспечения режима покоя усилительного каскада на полевых транзисторах: а, в - с управляющим p-n переходом; б – со встроенным каналом; г – с индуцированным каналом

вх вх

|

| K |

| β |

вх вх

|

вых вых

|

| 𝑼 вых |

ос ос

|

ос ос

|

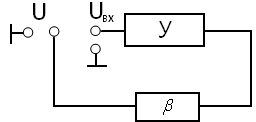

Рисунок 1.14 Структурная схема усилителя с обратной связью

а)

б)

в)

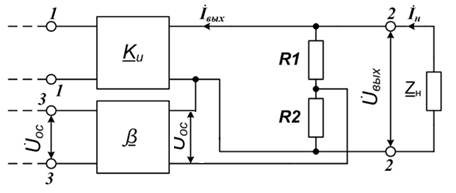

Рисунок 1.15 Способы получения сигнала обратной связи: а – по напряжению; б – по току;

в - комбинированный

а)

б)

в)

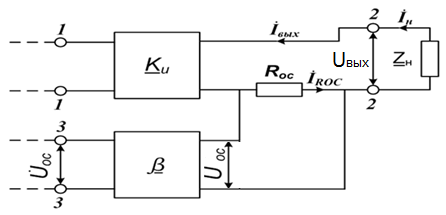

Рисунок 1.16 Способы введения сигнала обратной связи на вход усилителя:

а – последовательный; б – параллельный; в - смешанный

Рисунок 1.17 Амплитудно-частотная характеристика

Усилителя с обратной и без обратной связи

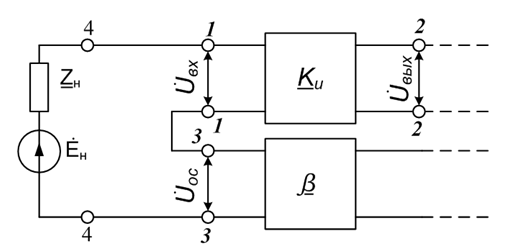

Рисунок 1.18 Последовательная обратная связь по току

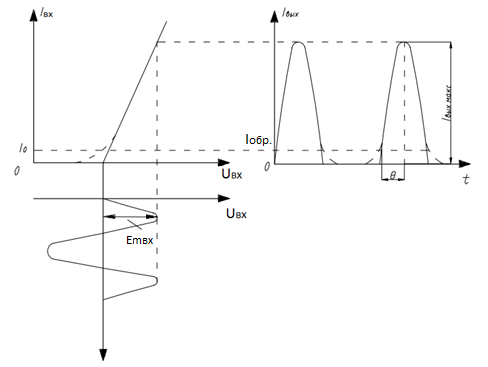

Рисунок 1.19 Графическая иллюстрация работы усилительного каскада в режиме класса А

Рисунок 1.20 Графическая иллюстрация работы усилительного каскада в режиме класса В

Рисунок 1.21 Графическая иллюстрация работы усилительного каскада в режиме класса АВ

Рисунок 1.22 Графическая иллюстрация работы усилительного каскада в режиме класса С

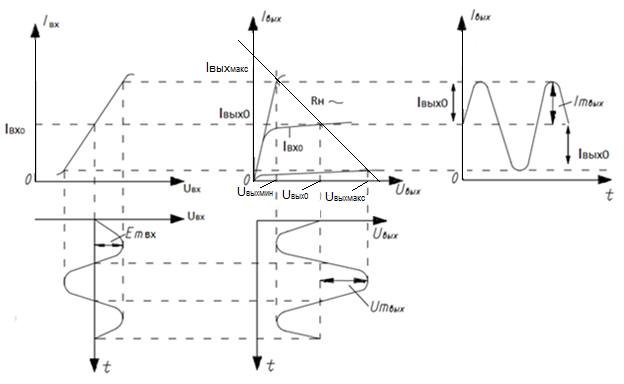

Рисунок 1.23 Графический анализ работы усилительного каскада с нагрузкой в режиме класса А

Рисунок 1.24 Принципиальная схема усилительного резисторного каскада в схеме с ОЭ

Рисунок 1.25 Эквивалентная схема

Усилительного каскада в схеме с ОЭ в диапазоне средних частот

Рисунок 1.26 Эквивалентная схема

усилительного каскада в схеме с ОЭ в диапазоне низких частот

Рисунок 1.27 Эквивалентная схема усилительного каскада в схеме с ОЭ в диапазоне высоких частот

Рисунок 1.28 Принципиальная (а) и эквивалентная (б) схемы усилительного каскада в схеме с ОБ

Рисунок 1.29 Принципиальная (а) и эквивалентная (б) схемы усилительного каскада в схеме с ОК (эмиттерный повторитель)

Рисунок 1.30 Схемы усилителей с непосредственными

межкаскадными связями

Рисунок 1.31 Схемы усилителей с непосредственными межкаскадными связями

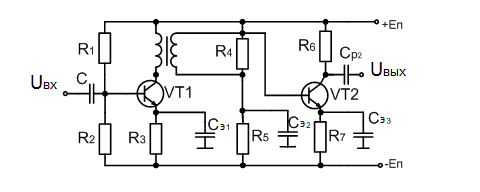

Рисунок 1.32 Схема усилителя с

Гальванической межкаскадной связью

Рисунок 1.33 Схема усилителя с гальваниче- ской межкаскадной связью

Рисунок 1.34 Схема усилителя с оптроном

| К |

| Э |

| Б |

| Iб |

| Iб1 |

| Iэ1 |

| Iб2 |

| Iэ2 |

| Iэ |

| Iк2 |

| Iк1 |

| Iк |

| VT2 |

| VT1 |

| VT1 |

| VT2 |

| Э |

| Б |

| К |

| Iэ |

| Iк2 |

| Iк |

| Iб |

| Iк1 |

Рисунок 1.35 Схемы составных транзисторов

Рисунок 1.36 Каскодная схема

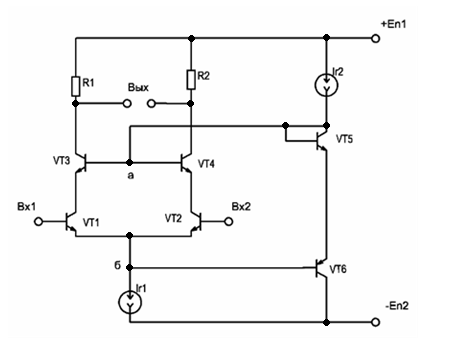

Рисунок 2.1 Схемы генератора стабильного тока

Рисунок 2.3 Схема сдвига нуля

Рисунок 2.2 Схема генератора малого стабильного напряжения

Рисунок 2.4 Схема каскада на двух

транзисторах с эмиттерной связью

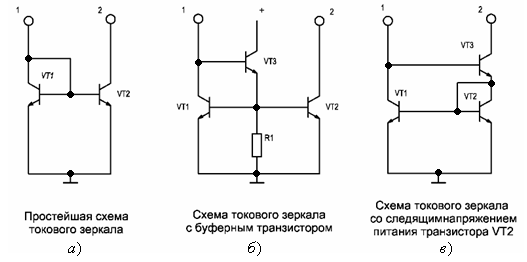

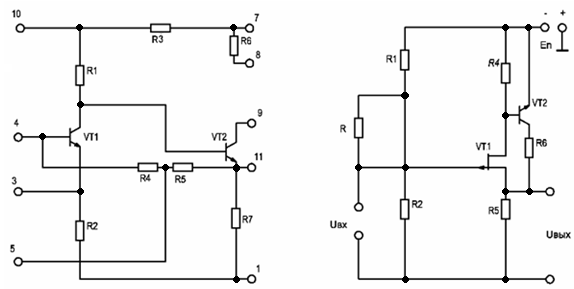

Рисунок 2.5 Структурные схемы токового зеркала

Рисунок 2.6 Типовые схемы токовых зеркал:

a – простейшая схема; б – с буферным транзистором; в – со следящим напряжением питания транзистора VT2

Рисунок 2.7 Схема усложнённых входных дифференциальных каскадов

Рисунок 2.8 Схема входного каскада на транзисторах супер-бэта

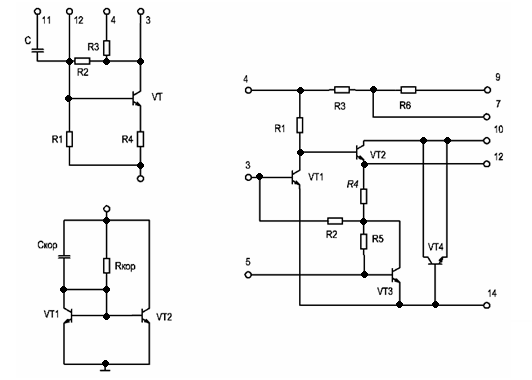

Рисунок 2.9 Схемы УНЧ на интегральных микросхемах

Рисунок 2.10 Схемы широкополосных интегральных усилителей

Рисунок 2.11 Схемы оконечных каскадов интегральных усилителей

Рисунок 2.12 Схема операционного усилителя

Рисунок 2.13 ФЧХ

Рисунок 2.14 Амплитудные (передаточные) характеристики

Рисунок 2.15 Схемы инвертирующего усилителя на базе ОУ с внешней ООС (без цепи питания и частотной коррекции)

Рисунок 2.16 Схема неинвертирующего усилителя

Рисунок 2.17 Схема простейшего дифференциального усилителя, построеного на одном операционном усилителе (ОУ)

Рисунок 2.18 Схема ручной балансировки нуля

Рисунок 2.19 Усилители переменного напряжения на базе ОУ

Рисунок 2.20 Усилитель с ОС Рисунок 2.21 Векторная диаграмма

а) б) в)

Рисунок 2.22 Устойчивость усилителя с ОС. Критерий

Найквиста

Рисунок 2.23 Запасы устойчивости

Рисунок 2.24 Устойчивость усилителя с ОС. Критерий устойчивости Боде

Рисунок 2.25