Тема 2.1 Логические основы ЭВМ, элементы и узлы

Базовые логические операции и элементы. Таблицы истинности. Логические узлы ЭВМ и их классификация. Сумматоры, дешифраторы, шифраторы, мультиплексоры. Триггеры: УГО и таблицы истинности RS-, JK- и Т-триггера. Регистры.

Элементами ЭВМ называют устройства, выполняющие логические функции, запоминающие информацию, преобразующие её и формирующие и усиливающие сигналы.

В качестве устройства, запоминающего информацию в элементах, используют триггер - устройство, обладающее двумя устойчивыми состояниями. Одно состояние триггера принимается за логическую 1, а другое за логический 0. По способу переключения и по закону функционирования триггеры можно разделить на следующие группы: RS-триггеры с раздельной установкой 0 и 1, D-триггеры задержки, универсальные JK-триггеры, счётные Т-триггеры.

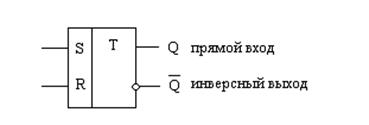

Условное графическое обозначение (УГО) RS-триггера приведено на рисунке 2

Рисунок 2 – RS – триггер с прямыми входами. УГО

Выход триггера принято обозначать буквой Q. Состояние триггера определяется логическим уровнем на этом выходе

Триггер, как правило, имеет два выхода: прямой  и инверсный

и инверсный  .Состояние триггера определяется логическим уровнем на его прямом выходе.

.Состояние триггера определяется логическим уровнем на его прямом выходе.

Значение на инверсном выходе всегда противоположно значению на прямом выходе.

Название триггеров определяется первыми буквами английских слов: S (set - установить); R (reset - выключить): Т (toggle - релаксатор); J (jerk - резко включить); К (kill - резко выключить): D (delay - задержка).

RS-триггеры с раздельной установкой 0 и 1. Простейший RS-триггер имеет два входа: R и S. При комбинации входных сигналов S=1, R=0 триггер устанавливается в единичное состояние Q=l, при входных сигналах S=0, R=l - в состояние Q=0, при S=0, R=0 триггер сохраняет своё состояние. Если на входы: R и S подать 1, то его выходной сигнал не определён, так как триггер при этом находится в неустойчивом состоянии. В связи с этим комбинация входных сигналов R=l, S=1 для RS-триггера является запрещённой.

На рисунке 3 приведены принципиальные схемы RS-триггеров, реализованных на элементах И-НЕ, ИЛИ-НЕ.

|

|

а) б)

Рисунок 3 – RS-триггер. Схемы принципиальные

а) с прямыми входами

б) с инверсными входами

Синхронный (тактируемый) RS-триггер имеет управляющий сигнал С на входе (clock - основная синхронизация), который при С=1 разрешает переключение по закону RS-триггера, при С=0 триггер сохраняет своё состояние.

D-триггер задержки. D-триггер имеет один информационный вход D и вход для синхронизирующего импульса С. Основное назначение D-триггера - задержка и хранение сигнала, поданного на вход D при С=1.

Его УГО приведено на рисунке 4.

Рисунок 4 – D – триггер. УГО

JK-триггер универсальный. JK-триггер работает по правилу RS-триггера и отличается от последнего тем, что комбинация сигналов J=K=1 не является запретной. При этих сигналах JK -триггер изменяет своё состояние на обратное тому, в котором он находился. Условное графическое обозначение этого триггера приведено на рисунке 5.

Рисунок 5 – JK-триггер. УГО

Студент должен

знать:

- базовые логические элементы;

- классификацию цифровых устройств;

- основные логические узлы ЭВМ;

- УГО основных логических узлов.

уметь:

- составлять таблицы истинности;

- составлять схемы простых логических узлов ЭВМ.

Тема 2.2 Основы построения ЭВМ

Понятие архитектуры и структуры компьютера. Принципы (архитектура) фон Неймана. Основные компоненты ЭВМ, их назначение и взаимодействие. Основные типы архитектур ЭВМ.