Оперативные запоминающие

Устройства (ОЗУ)

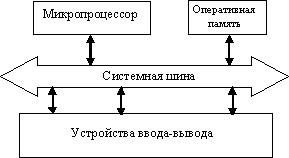

Операти́вная па́мять (также оперативное запоминающее устройство, ОЗУ) — в информатике — память, часть системы памяти ЭВМ, в которую процессор может обратиться за одну операцию (jump, move и т. п.).

Предназначена для временного хранения данных и команд, необходимых процессору для выполнения им операций.

Оперативная память передает процессору данные непосредственно, либо через кеш-память.

Каждая ячейка оперативной памяти имеет свой индивидуальный адрес.

ОЗУ может изготавливаться как отдельный блок или

входить в конструкцию однокристальной ЭВМ или

микроконтроллера.

Рисунок 9.1 – Простейшая схема взаимодействия оперативной памяти с ЦП

На сегодня наибольшее распространение имеют два вида ОЗУ:

• SRAM (Static RAM)

• DRAM (Dynamic RAM)

Статическое ОЗУ

Статическая оперативная память с произвольным доступом (SRAM — Static Random Access Memory) — полупроводниковая оперативная память, в которой каждый двоичный разряд хранится в схеме с положительной обратной связью, позволяющей поддерживать состояние сигнала без постоянной перезаписи.

Тем не менее, сохранять данные без перезаписи SRAM может только, пока есть питание, т.е. SRAM остается энергозависимым типом памяти.

Двоичная SRAM

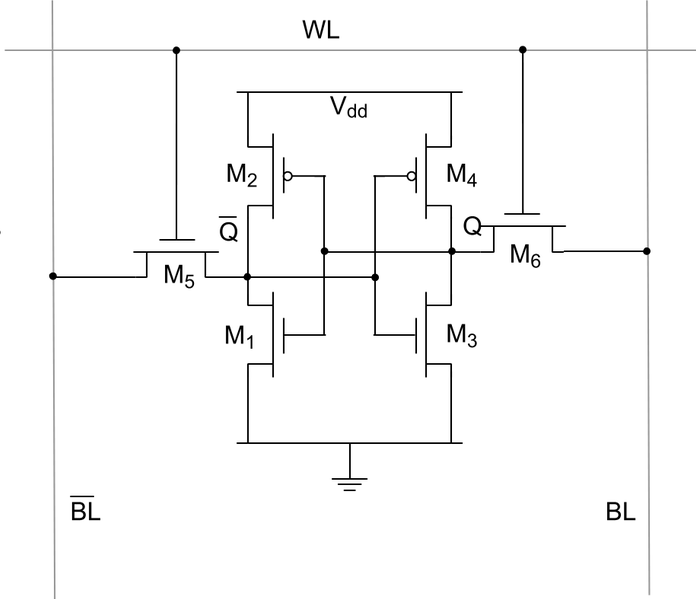

Типичная ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии состоит из двух перекрестно (кольцом) включенных инверторов и ключевых транзисторов для обеспечения доступа к ячейке.

Часто для увеличения плотности упаковки элементов на кристалле в качестве нагрузки применяют поликремниевые резисторы.

Недостатком такого решения является рост статического

энергопотребления.

Рисунок 9.2 – Типичная ячейка статической двоичной памяти

Линия WL (Word Line) управляет двумя транзисторами

доступа. Линии!BL и BL (Bit Line) – битовые линии,

используются и для записи данных и для чтения данных.

Запись. При подаче «0» на линию!BL или BL параллельно включенные транзисторные пары (M5 и M1) и (M6 и M3) образуют логические схемы 2ИЛИ, последующая подача «1» на линию WL открывает транзистор M5 или M6, что приводит к соответствующему переключению триггера.

Чтение. При подаче «1» на линию WL открываются транзисторы M5 и M6, уровни записанные в триггере выставляются на линии!BL и BL, и попадают на схемы чтения.

Для выбора ячеек (WL) используются дешифратор адреса.

Рисунок 9.3 – Дешифратор адреса

| A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 | SRAM | ||||

| WE | |||||

| OE | |||||

| CE1 | |||||

| CE2 | |||||

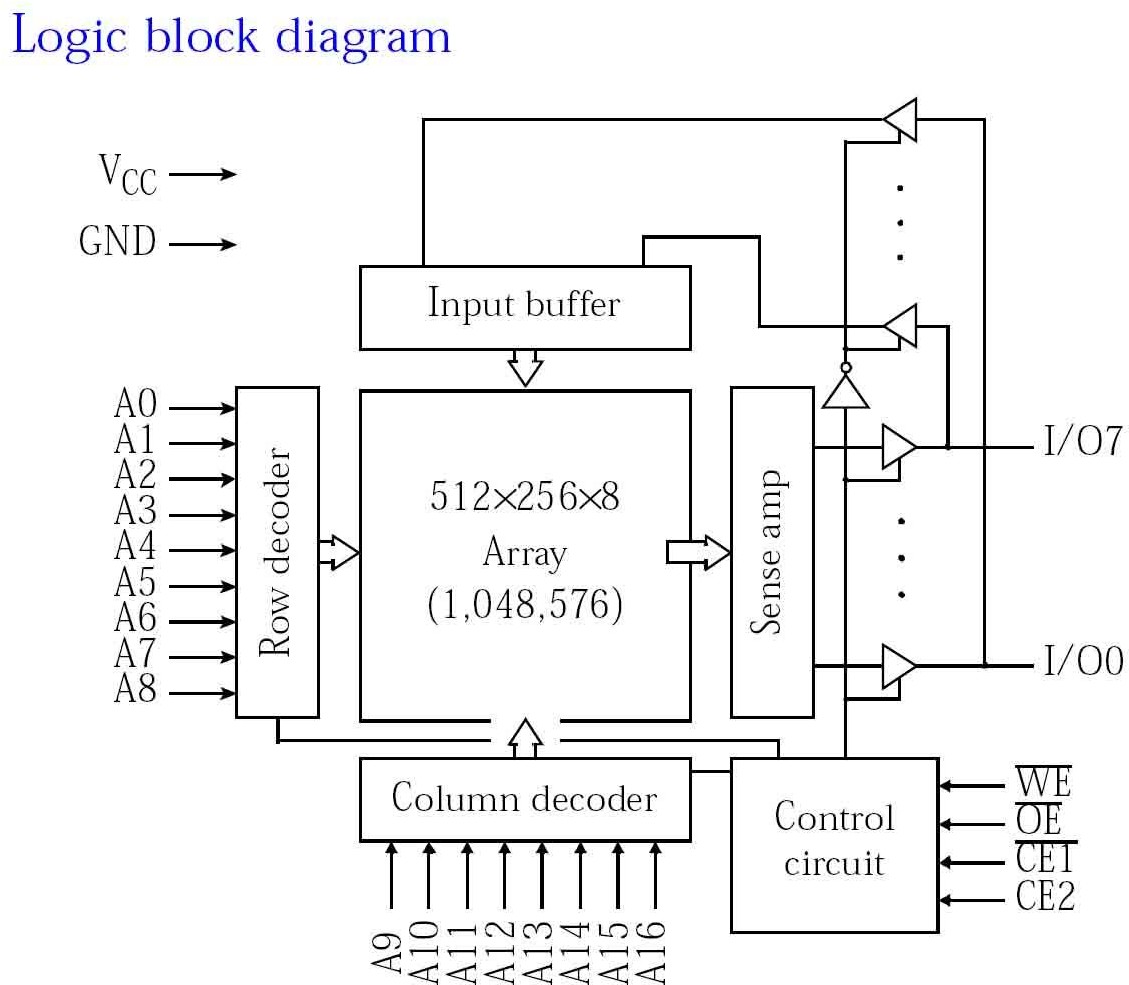

Рисунок 9.4 – Условно-графическое обозначение микросхем SRAM

Рисунок 9.4 – Условно-графическое обозначение микросхем SRAM

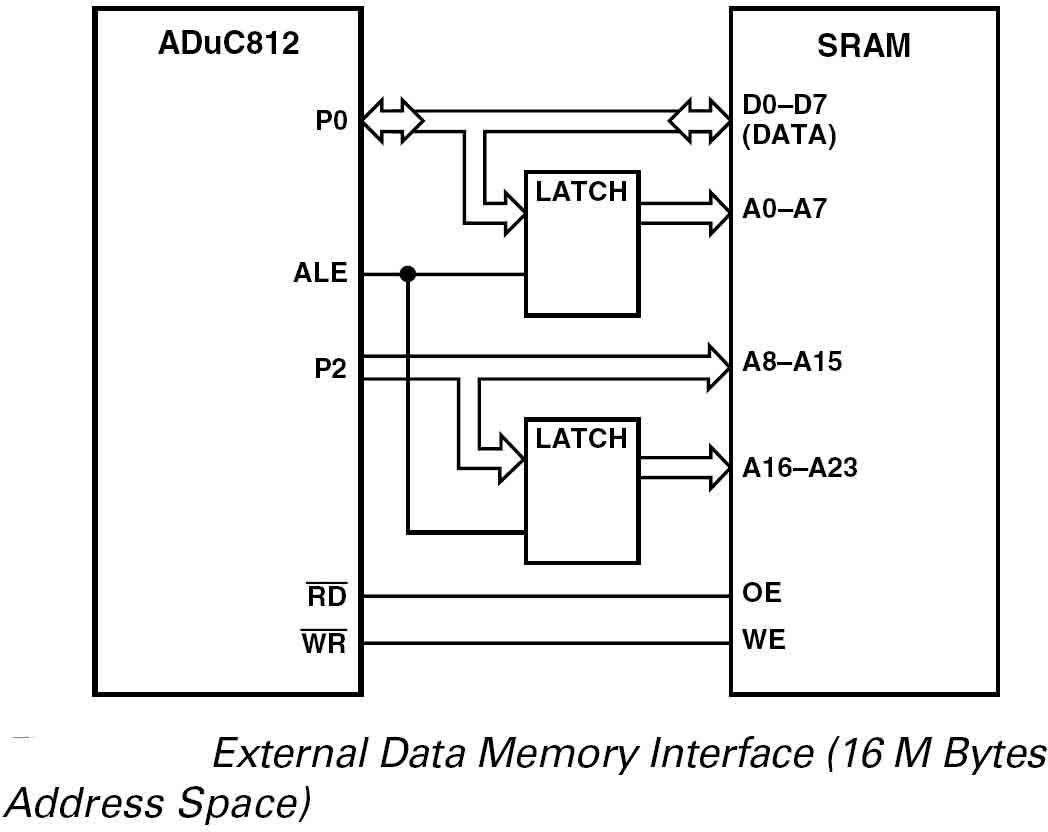

Рисунок 9.5 – Пример подключения SRAM к микроконтроллеру

Рисунок 9.5 – Пример подключения SRAM к микроконтроллеру

Преимущества:

• Быстрый доступ. SRAM — это действительно память произвольного доступа, доступ к любой ячейке памяти в любой момент занимает одно и то же время.

• Простая схемотехника — SRAM не требуются сложные контроллеры.

• Возможны очень низкие частоты синхронизации, вплоть до полной остановки синхроимпульсов.

Недостатки: 13

• Невысокая плотность записи (шесть элементов на бит, вместо двух у DRAM).

• Высокое энергопотребление.

Вследствие чего — дороговизна килобайта памяти.

Тем не менее, высокое энергопотребление не является принципиальной особенностью SRAM, оно обусловлено высокими скоростями обмена с данным видом внутренней памяти процессора.

Энергия потребляется только в момент изменения информации в ячейке SRAM.

Применение

• SRAM применяется в микроконтроллерах и ПЛИС, в которых объем ОЗУ невелик (единицы килобайт), зато нужны низкое энергопотребление (за счет отсутствия сложного контроллера динамической памяти), предсказываемое с точностью до такта время работы подпрограмм и отладка прямо на устройстве.

• В устройствах с большим объемом ОЗУ рабочая память выполняется как DRAM.

• SRAM’ом же делают регистры и кэш-память.

Динамические ОЗУ

Динамическая память — Dynamic RAM — получила свое название от принципа действия ее запоминающих ячеек, которые выполнены в виде конденсаторов, образованных элементами полупроводниковых микросхем.

При отсутствии обращения к ячейке со временем за счет токов утечки конденсатор разряжается и информация теряется, поэтому такая память требует периодической подзарядки конденсаторов (обращения к каждой ячейке) — память может работать только в динамическом режиме.

Этим она принципиально отличается от статической памяти, реализуемой на триггерных ячейках и хранящей информацию без обращений к ней сколь угодно долго (при включенном питании).

Рисунок 9.6 – Запоминающая ячейка динамического ОЗУ

Запоминающие ячейки микросхем DRAM организованы в

виде двумерной матрицы.

Адреса строки и столбца передаются по мультиплексированной шине адреса MA (Multiplexed Address) и стробируются по спаду импульсов RAS# (Row Access Strobe) – строка и CAS# (Column Access Strobe) – столбец.

Совокупность ячеек DRAM образуют условный

«прямоугольник», состоящий из определённого количества строк и столбцов.

Один такой «прямоугольник» называется страницей, а совокупность страниц называется банком.

Весь набор ячеек условно делится на несколько областей.

WE RAS CAS

Устройство управления

Устройство DI

ввода/вывода DO

|

| Накопитель |

Рисунок 9.7 – Типовая структура микросхемы динамической ОЗУ

Основными характеристиками DRAM являются рабочая

Частота и тайминги.

При обращении к ячейке памяти контроллер памяти задает номер банка, номер страницы в нем, номер строки и номер столбца и на все эти запросы тратится время, помимо этого довольно большой период уходит на открытие и закрытие банка после самой операции.

На каждое действие требуется время, называемое

«таймингом ».

Основными «таймингами » DRAM являются:

• задержка между подачей номера строки и номера столбца, называемая временем полного доступа (англ. RAS to CAS delay);

• задержка между подачей номера столбца и получением содержимого ячейки, называемая временем рабочего цикла (англ. CAS delay);

• задержка между чтением последней ячейки и подачей номера новой строки (англ. RAS precharge).

Тайминги измеряются в наносекундах, и чем меньше величина этих таймингов, тем быстрее работает оперативная память.

Типы DRAM

Перечислить типы DRAM. Студенты должны рассмотреть самостоятельно.

Страничная память

Страничная память (англ. page mode DRAM, PM DRAM) являлась одним из первых типов выпускаемой компьютерной оперативной памяти.

Память такого типа выпускалась в начале 90-х годов, но с ростом производительности центральных процессоров и ресурсоемкости приложений требовалось увеличивать не только объём памяти, но и скорость ее работы.