Регистр - устройство для хранения и (или) преобразования многоразрядных чисел.

Регистры обладают большими функциональными возможностями. Они используются в качестве управляющих и запоминающих устройств генераторов и преобразователей кодов, счетчиков, делителей частоты, узлов временной задержки.

Элементами структуры регистров являются синхронные триггеры D, RS или JK - типа с динамическим или статическим управлением. Так как одиночный триггер может запомнить один разряд (бит) двоичной информации, то его можно считать одноразрядным регистром. Для запоминания многоразрядных чисел используют "линейки " из нескольких триггеров - по количеству разрядов чисел. В схемы регистров входят также комбинационные элементы, роль которых в данном случае вспомогательная.

Занесение информации в регистр называют операцией ввода или считывания. Запись информации в регистр не требует его предварительного обнуления (сброса).

Все регистры в зависимости от функциональных свойств подразделяются на две категории: накопительные регистры (памяти, хранения) и сдвиговые.

Регистры памяти - простейший вид регистров. Их задача - хранить двоичную информацию небольшого объема в течение короткого промежутка времени. Эти регистры представляют собой набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод (запись, загрузка) и вывод (считывание) информации производится одновременно во всех разрядах параллельным кодом. Запись обеспечивается тактовым импульсом. С приходом очередного тактового импульса происходит обновление записанной информации.

Сигналы на выходах триггеров характеризуют выходную информацию. Считывание может производиться в прямом или в обратном коде (в последнем случае - с инверсных выходов). Регистры памяти (хранения) представляют собой, по существу, наборы триггеров с независимыми информационными входами и (обычно) общим тактовым входом. В качестве регистров подобного рода могут быть использованы без дополнительных элементов многие типы синхронных триггеров.

Особенно пригодны микросхемы, содержащие в одном корпусе несколько самостоятельных триггеров.

Кроме операции хранения данных регистры могут использоваться и для операции сдвига данных с целью преобразования двоичного последовательного кода в параллельный и наоборот. Это так называемые сдвиговые регистры или регистры сдвига, которые получаются путем цепочного соединения триггеров.

Суть сдвига состоит в том, что по сигналу синхроимпульса происходит одновременная перезапись содержимого каждого триггера в соседний триггер. При этом не меняется само двоичное слово (число), записанное в регистре, оно лишь сдвигается на один разряд и только содержимое последнего триггера ТТ3 пропадает из регистра, а на вход первого ТТ0 поступает новый бит.

Параллельные регистры - это устройства, предназначенные для записи, хранения и выдачи информации, представленной в виде двоичных кодов. Для хранения каждого двоичного разряда в регистре используется одна триггерная ячейка.

Для запоминания многоразрядных слов необходимое число триггеров объединяют вместе и рассматривают как единый функциональный узел-регистр. Если регистр построен на триггерах-защелках, то его называют регистр-защелка.

Рисунок 7 - Параллельный регистр, собранный на RS-триггерах

Рисунок 8 - Временные диаграммы, характеризующие работу регистра

Рисунок 9 - Графическое изображение полученной модели регистра

4 Неполный дешифратор с активными единичными сигналами на выходе

Дешифратор - устройство для расшифровки (декодирования) сообщения и перевода содержащейся в нём информации на язык (в код) воспринимающей системы. В общем случае дешифратор имеет n входов и m выходов. Поступающая на входы дешифратор информация преобразуется — дешифрируется, — и на соответствующем выходе (группе выходов) выделяется сигнал, указывающий признак (или содержание) входной информации. Любому сигналу или комбинации сигналов на входах дешифратор соответствует определённый сигнал или комбинация сигналов на выходах дешифратор Это соответствие задаётся структурой дешифратор при его проектировании. дешифратор. применяют в различных устройствах обработки и передачи информации: в телемеханике, в вычислительной технике (декодирующие устройства, преобразователи представления величин), в радиотехнике и измерительной технике (Детекторы, демодуляторы), в системах телефонной и телеграфной связи. Назначение предопределяет структуру, число входов и выходов дешифратор, форму и последовательность входных и выходных сигналов.

Дешифратор в телемеханике расшифровывают сообщения (их коды) по структурам принимаемых сигналов. Структура сигналов создаётся приданием импульсам, образующим сигналы, различных качеств — признаков. Такими признаками являются полярность, частота и порядок следования, количество, длительность и амплитуда импульсов, группировка импульсов различного качества и т.д. Если, например, дешифратор используется в системе телеуправления, то дешифратор автоматически анализирует структуру принимаемых сигналов в соответствии с программой, заложенной в конструкции самого дешифратор; сигналы с его выходов подаются на входы исполнительных механизмов управляемых объектов. Избирательность — основное свойство дешифратор; она обеспечивает защиту входных цепей воспринимающих систем от посторонних сигналов, которые могут оказать ложное воздействие на систему.

В вычислительной технике дешифратор применяют в качестве преобразователей кода в код или кодов в эквивалентные им непрерывные величины. В радиотехнике дешифратор. восстанавливает передаваемое сообщение из радиосигнала, параметры которого изменяются в такт с передаваемым сообщением.

Таблица 2 - Таблица истинности работы дешифратора

| x1 | x2 | x3 | x4 | a | b | c | d | e | f | g |

Рисунок 10 - Неполный дешифратор

Рисунок 11 - Временные диаграммы, характеризующие работу дешифратора

Рисунок 12 - Графическое изображение полученной модели дешифратора

5 Сборка нового элемента

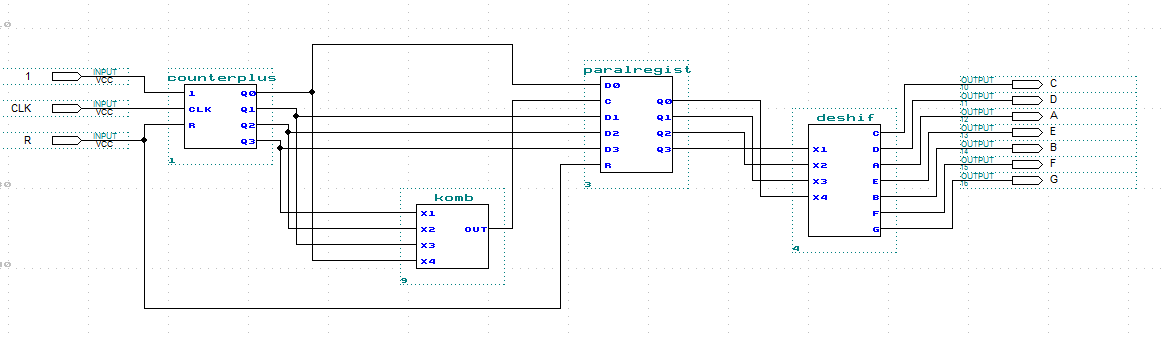

В этом пункте производится окончательная сборки схемы путем соединения ранее полученных компонентов. От источника сигналов «1» будет поступать напряжение высокого уровня необходимое для нужной работы счетчика и регистра. Счетчик будет производить подсчет импульсов поступающих на его вход «CLK» от источника. Полученный четырехразрядный код будет поступать на входы регистра и комбинационной схемы, с выхода которой сигнал также поступает на вход регистра. Информационные коды поступающие на вход регистра сохраняются и передаются на вход дешифратора, где преобразуются в сигнал высокого уровня на выходе, номер, которого соответствует десятичному значению поступившего кода.

Рисунок 13 - Схема нового элемента

Рисунок 14 - Временные диаграммы, характеризующие работу нового элемента

Рисунок 15 - Графическое изображение полученной модели нового элемента

Заключение

В ходе выполнения курсового проекта мною была собрана принципиальная электрическая схема состоящая из: суммирующего двоичного счетчика, комбинационной схемы, параллельного регистра и дешифратора.

Были получены знания о работе компонентов используемых в схеме. Так же была освоена программа проектирования устройств на ПЛИС Altera MAX+PLUS II и рассмотрены основные методы построения схем из уже имеющихся в библиотеке компонентов.

Список использованной литературы

1 Потехин Д.С., Тарасов И.Е., «Разработка систем цифровой обработки сигналов на базе ПЛИС», г. Москва, 2007г.

2 Поляков А.К., «Языки VHDL и Verilog в проектировании цифровой аппаратуры на ПЛИС. Учебное пособие для вузов», г. Москва, 2012г.

3 Антонов А.П., «Язык описания цифровых устройств. ALTERA HDL. Практический курс», г. Москва, 2002г.

4 Грушвицкий Р.И., Мурсаев А.Х., Угрюмов Е.П., «Проектирование систем на микросхемах программируемой логики», г. Санкт-Петербург, 2002г.

5 Зобенко А. А., Филиппов А. С., Комолов Д. А., Мяльк Р. А., «Системы автоматизированного проектирования фирмы Altera MAX+plus II и Quartus II. Краткое описание и самоучитель», г. Москва, 2002 г.