По техническому заданию, устройство должно быть выполнено в технологическом базисе ES2-0.7um. Нам необходимо определить параметры моделей транзисторов, соответствующих данной технологии. Для этого воспользуемся программой Microwind2. Перенесём из нее параметры транзисторов в файл breakout.lib системы среды проектирования OrCAD.

При этом нам необходимо добавить параметр TOX, определяющий толщину подзатворного диэлектрика. Согласно технологическим параметрам tox=14 нм.

Теперь необходимо рассчитать геометрические параметры транзисторов в логических вентилях, следуя нашей технологии ES2-0.7um.

Для нашей технологии минимально допустимая ширина транзисторов 4 λ.

Рассмотрим передаточные характеристики вентилей с минимальными ширинами. Они представлены на рисунке 6.

Рисунок 6- Передаточные характеристики логических вентилей

Это худшие случаи по помехозащищенности. Inv- инвертор с минимальными ширинами. 3norN – элемент 3ИЛИ-НЕ, в котором ширины p-канальных транзисторов равны трем минимальными ширинам. 3nor – 3ИЛИ-НЕ, в котором ширины всех транзисторов равны минимальным. Помехозащищенность нуля в вентилях 3nor и 3norN меньше трети напряжения питания из чего можем заключить, что использование данных вентилей не желательно. Сделаем выбор в пользу согласованных вентилей.

Токи через транзисторы в согласованных вентилях необходимо выровнять:

Wn=1.6um;

Найдем Wp из этого уравнения

Ln=Lp; Округлим до целого числа λ;

Получаем, что Wp=4.8um;

На рисунках 7-9 показаны схемы и символы простейших логических вентилей.

Рисунок 7 - Схема и символ инвертора

Рисунок 8 – Схема и символ элемента 2nor

Рисунок 9 - Схема и символ 3nor

Для обеспечения времени фронтов заданного в техническом задании при работе устройства на емкостную нагрузку будем использовать буфер. Сделаем его на основе двух последовательно соединенных инверторов с уменьшенным выходным сопротивлением. Ширины транзисторов в буфере выберем исходя из согласования токов. Для определения граничного значения повышающего коэффициента ширины, при работе буфера на Сн, промоделируем схему, показанную на рисунке 10.

|

|

Рисунок 10 - Схема для моделирования буфера

Здесь первые два входных инвертора имитируют узел логической схемы, а два выходных образуют буфер. Ширина выходного инвертора буфера привязана к значению переменной K, а входного инвертора буфера - к корню из K. Это делается для сохранения относительного коэффициента разветвления.

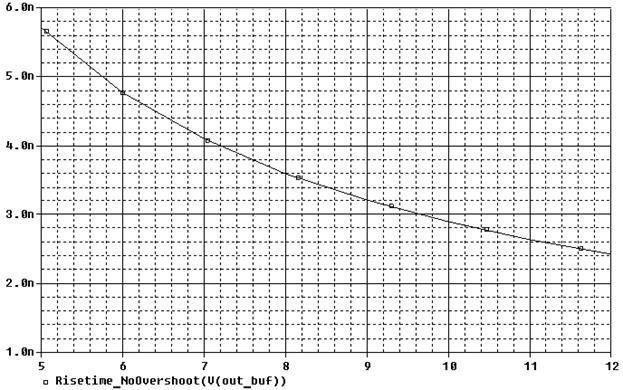

Промоделировав буфер, делаем вывод о том, что для обеспечения заданного времени фронта K должно равняться 11. Такой выбор коэффициента обеспечит запас по времени фронта. Результат параметрического анализа буферов по K показан на рисунке 10.

Рисунок 10 - Результат моделирования буфера

Для оценки времен фронта при уменьшении напряжения питания проведем параметрический анализ. На рисунке 11 показаны зависимость времени фронта и среза от напряжения питания.

Рисунок 11 – Результат параметрического анализа по напряжению питания

Для оценки времени фронта при увеличении нагрузочной емкости проведем параметрический анализ. На рисунке 12 показана зависимость времени фронта от емкости нагрузочного конденсатора.

Рисунок 12 - Результат параметрического анализа по величине емкости

|

|

Исходя из приведенных выше результатов моделирования делаем вывод, что минимальное напряжение питания, при котором сохраняется время фронта выше заданного в техническом задании равно Uип=4.3В.

Максимальная емкость, при которой выполняются требования технического задания к фронтам сигналов, равна  .

.

Для оценки нагрузочной способности и рабочей частоты схемы соберем кольцевой генератор. Схема моделирования, представленная на рисунке 13, является цепочкой из Nmax+1=9 инверторов замкнутых в кольцо, что обеспечивает отрицательную обратную связь. Стабильных состояний у такой схемы, следовательно, в ней будет возбуждаться колебания с периодом  . Для оценки максимальной частоты тактового сигнала с реальной нагрузкой и без нее соберем два кольцевых генератора.

. Для оценки максимальной частоты тактового сигнала с реальной нагрузкой и без нее соберем два кольцевых генератора.

Рисунок 13 - Схема моделирования кольцевого генератора

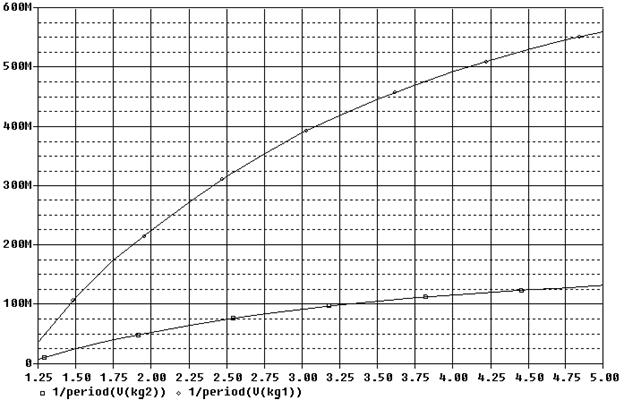

На рисунке 14 показана зависимость максимальной частоты тактового сигнала  от количества подключенных единичных нагрузок к каждому узлу устройства.

от количества подключенных единичных нагрузок к каждому узлу устройства.

Рисунок 14 – Зависимость  от коэффициента разветвления в каждом узле

от коэффициента разветвления в каждом узле

Исходя из рисунка 15 можно заключить, что требования технического задания ( ) выполняются вплоть до Mсх=27. В нашей схеме максимальный коэффициент разветвления Mсх=5.

) выполняются вплоть до Mсх=27. В нашей схеме максимальный коэффициент разветвления Mсх=5.

Полученные частоты:

Без нагрузки:

= 559,9 МГц

= 559,9 МГц

С максимальной нагрузкой

= 132 МГц

= 132 МГц

Полученные частоты удовлетворяют требования технического задания для данного устройства.

Оценим влияния напряжения питания на максимальную возможную частоту тактового сигнала. Результат параметрического анализа кольцевых генераторов по напряжению питания показан на рисунке 16.

|

|

Рисунок 16 – Зависимость частот кольцевых генераторов от напряжения питания

Исходя из приведенных выше результатов можем заключить, что максимальная частота работы устройства выше заданной по техническому заданию при напряжениях питания выше 1,5В.

Приступим к вычислению динамических характеристик всех логических элементов. Схема моделирования приведена на рисунке 17. Два инвертора установленные на вход имитируют узел схемы. Для получения фронтов, срезов и задержек приближенных к задержкам логических элементов в схеме устройства, необходимо подключить на выходы логических элементов нагрузочные инверторы с ширинами, увеличенными в M раз, где М максимальный коэффициент разветвления, встречающийся в схеме для конкретного элемента. Это эквивалентно подключению на выход логического элемента M единичных нагрузок.

Рисунок 17 - Схема моделирования логических элементов

Динамические характеристики вентилей представлены в таблице 2.

Таблица 2 - Результаты измерения динамических характеристик вентилей

| Логический элемент | tфр,пс | tср,пс | tзд01,пс | tзд10,пс | Cн |

| Инвертор | 2*Сinv | ||||

| 2nor | 5*Сinv | ||||

| 3nor | 3*Сinv | ||||

| Буфер | 3 пФ |

На завершающем этапе схемотехнического проектирования приступим моделированию полной схемы устройства на частоте заданной в техническом задании. Все блоки, используемые в логическом проектировании, переделаны с использованием схемотехнических вентилей. В результате общий вид схемы не изменился.

Результат моделирования показан на рисунке 18.

Частота такового сигнала 25 МГц.

Рисунок 18 – Результат моделирования устройства