Задание:

Создать описание мультиплексора “два 4 разрядных входа в один”.

- Первый вход sw(4 downto1);

- Второй вход sw(8 downto5);

- Выход мультиплексора ledbuf (4 downto1);

Вход управления - UP: 0(нажата) на выход передается первый вход, 1(ненажата) на выход передается второй вход.

На выходы ledbuf(8 downto5)подать логические нули.

Дать ответ на вопрос: что такое мультиплексор, демультиплексор?

Синтез схемы

Во вновь созданном проекте, именуемом «MUX» необходимо создать новый файл «File –New – VHDL File». В открывшемся окне набрать следующий код, реализующий функцию мультиплексора согласно заданию (листинг 1). Имя модуля LAB2.

ENTITY LAB2 IS

PORT(

sw: IN BIT_VECTOR(8 downto 1); \\входы типа STD_LOGIK – 8 разрядная шина данных

ledbuf: OUT BIT_VECTOR(8 downto 1);\\ выход типа STD_LOGIK – 8 разрядная шина данных

up: IN BIT \\ последовательный вход управления – управления мультиплексирования

);

END LAB2;

ARCHITECTURE RTL OF LAB2 IS

BEGIN

ledbuf(4 downto 1) <= (sw(4 downto 1) and not (up,up,up,up)) or (sw(8 downto 5) and (up,up,up,up)); \\выходы ledbuf(4 - 1) будут мультиплексированы со входом sw(4 downto 1) при установке логического 0 на входе up, а при установке логической 1 на вход up со входом sw(8 downto 5)

ledbuf(8 downto 5) <= (others <= '0');\\ на выходах установить нули

END RTL;

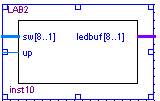

На рисунке 3.1 представлена синтезированная схем, реализуемая при помощи схемного проектирования. Скомпилированный элемент представлен на рисунке 3.2

Рисунок 3.1 - Синтезированная схема

Рисунок 3.2 –Синтезированный компонент

Результат работы схемы отслеживается на временной диаграмме, представленной на рисунке 3.3

Рисунок 3.3 - Временная диаграмма

Вывод (Заключение по результатам выполнения)

Согласно заданию требуется спроектировать электронный компонент – мультиплексор, реализующий в зависимости от сигнала на входе управления up, коммутацию входов данных шин sw 4-1 и sw 8-5 с выходной шиной ledbuf 4-1, оставшаяся часть 8 –разрядной шины данных ledbuf 8-1 постоянно находится в состоянии логический «0».

В результате выполнения задания проведено описание работы элемента на языке VHDL, синтезирован компонент, как представлено на рисунке на плате DiLaB – II (Cyclone II) проведена отладка и проверка работоспособности схемы.

По временной диаграмме проверено состояние переходов схемы в зависимости от комбинаций на входах мультиплексора. В результате выполнения можно дать определение мультиплексору как устройству, позволяющему передавать по одной линии несколько сигналов одновременно в зависимости от сигнала на шине управления.

Работа выполнена в полном объеме.

Приложение №1

СОДЕРЖАНИЕ

Введение

1 Проектирование цифровых устройств

1.1 Составление справочных сведений (задание 1)

1.2 Построение простейших схем (задание 2)

1.2.1 Расчет генератора импульсов

1.2.2 Схемы задержки

1.3 Проектирование арифметического логического устройства

2 Проектирование цифровых устройств Cyclone II (Cyclone III)

2.1 Описание отладочного модуля Di- Lab II Cyclone II

2.2 Описание отладочного модуля mini Di-Lab Cyclone III (задание 4)

2.3 Проектирование цифрового устройства – «бегущий огонь» (задание 5)