Кафедра ЭВА

Курсовая работа

по дисциплине «Моделирование»

Выполнила студентка гр. С-74:

Маняхина С.А.

Преподаватель

Гоманилова Н.Б.

Москва 2004

СОДЕРЖАНИЕ

1. Техническое задание на курсовую работу -

2. Анализ технического задания -

3. Моделирование -

4. Разработка теста -

5. Выводы -

ТЕХНИЧЕСКОЕ ЗАДАНИЕ НА КУРСОВУЮ РАБОТУ

1. Провести моделирование и отладку заданной схемы.

2. Разработать обнаруживающий тест с использованием системы схемотехнического проектирования "Мозайка".

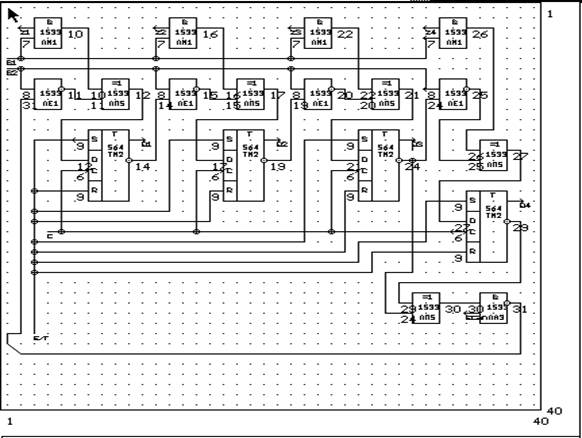

Заданная схема - схема встроенного блока логических наблюдений BILBO

Рис.1

В1, В2 – управляющие входы

Z1, Z2, Z3, Z4 – информационные входы

Q1, Q2, Q3, Q4 – информационные выходы

Scan – вход сканирования

В курсовой работе требуется рассмотреть 2 режима работы схемы:

1. B1=B2=1, C=0 – системный рабочий режим

2. B1=B2=0, C=1 – генератор псевдослучайных чисел

АНАЛИЗ ТЕХНИЧЕСКОГО ЗАДАНИЯ

BILBO – это специально разработанный элемент для создания схем самотестирования. Этот многофункциональный элемент позволяет уменьшить схемную избыточность, которая вводится в кристалл для обеспечения самотестирования.

Рассмотрим работу схемы в заданных режимах.

1. Системный рабочий режим

B1=B2=1, Scan=0

При таких значениях на управляющих входах и входе сканирования схему можно представить следующим образом:

Рис.2

Таким образом, в системном рабочем режиме схема представляет собой 4 D-триггера, работающих независимо друг от друга.

2. Генератор псевдослучайных чисел

B1=B2=0, Scan=1

При таких значениях на управляющих входах и входе сканирования схему можно представить следующим образом:

Рис.3

В данном режиме работы на входы D триггеров 2-4 подаются сигналы с инверсных выходов предыдущих триггеров. Но т.к. сигналы с инверсных выходов инвертируются, то на D-входы подаются сигналы, совпадающие со значениями на прямых выходах триггеров. На вход D 1-го триггера подаются сигналы с выходов триггеров 3-4, которые складываются по модулю 2 и инвертируются.

Пусть в начальном состоянии генератор псевдослучайных чисел выводит число 1111, т.е. триггеры установлены в 1. Значит, в следующем такте на вход D 1-го триггера поступает 1, на выходах триггеров значения –1111. Т.е. схема работает неверно.

Для корректной работы схемы необходимо подавать на вход 1-го D-триггера неинвертированный сигнал. Элемент ИЛИ-НЕ необходим для правильной работы схемы в режиме 1. Поэтому будем инвертировать сигнал еще раз, заменив элемент И на И-НЕ.

Окончательный вид схемы:

Рис.4

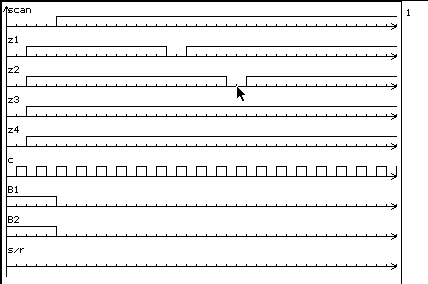

Временные диаграммы для входов:

Рис.5

В схеме использованы следующие элементы:

Серия 1533

«И» ЛИ1 - 4

«ИЛИ-НЕ» ЛЕ1 - 4

«исключающее ИЛИ» ЛП5 - 5

«И-НЕ» ЛА3 - 1

Серия 564

D-триггер ТИ2 - 4

МОДЕЛИРОВАНИЕ

Моделирование схемы было произведено в две итерации. На первом шаге ошибочной оказалась временная диаграмма входов S и R триггеров, которая не была приведена в техническом задании. На входы S и R триггеров подавалась 1, при этом триггеры не срабатывали на входные воздействия. Для корректной работы схемы необходимо подавать на эти входы 0.

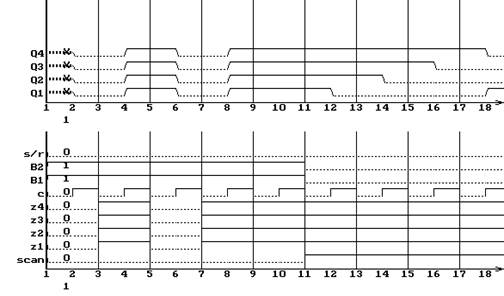

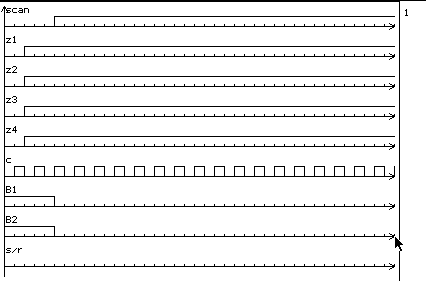

При моделировании схемы были получены следующие временные диаграммы:

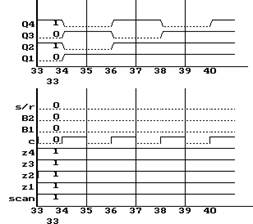

Рис.6

Временные диаграммы на тактах 1-11 соответствуют 1-му режиму работы схемы. Каждый триггер работает независимо от других. Запись 0 и 1 осуществляется верно.

| № имп | Z1 | Z2 | Z3 | Z4 | Q1 | Q2 | Q3 | Q4 |

Такты 12-40 соответствуют 2-му режиму работы схемы.

| № имп | Q1 | Q2 | Q3 | Q4 |

По таблице состояний выходов видно, как осуществляется генерация псевдослучайных чисел: сигналы Q1 и Q3 суммируются по mod2 и поступают на 1-ый триггер. На триггеры 2-4 поступают значения от предыдущих триггеров. Из временных диаграмм также видно, что изменение сигнала на входах Z1-Z4 в данном режиме не влияют на работу схемы, что соответствует выводам, полученным на этапе анализа технического задания.

Следовательно, схема работает верно.

РАЗРАБОТКА ТЕСТА

При разработке теста для заданной схемы было выполнено 2 итерации.

На первой итерации рассматривалась работа схемы в системном рабочем режиме.

В1=В2=1

Scan=0

Рассмотрим элементы 1-4 (рис.4). Возможные неисправности приведены в таблице.

| Неисправ ность | Z1 | Значение на выходе Q1 без неисправности | С неисправностью |

| z1º0 | |||

| z1º1 | |||

| P10º0 | |||

| P10º1 | |||

| B1º0 | |||

| P11º1 | |||

| P12º0 | |||

| P12º1 | |||

| Q1º0 | |||

| Q1º1 |

Неисправности B1º1, B2º1, B2º0, P31º1, P31º0, P11º0 проверить нельзя из-за выбранного режима работы. Таким образом, в качестве первоначального теста подадим следующую временную диаграмму:

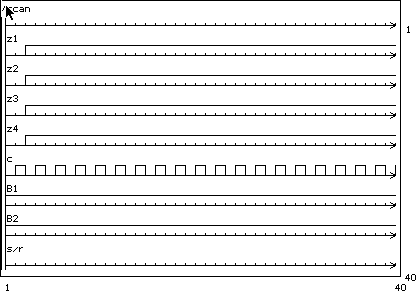

Рис.7

График изменения полноты теста

Рис.8

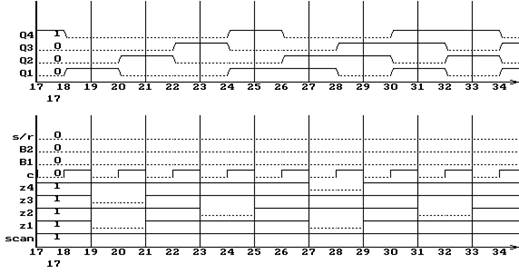

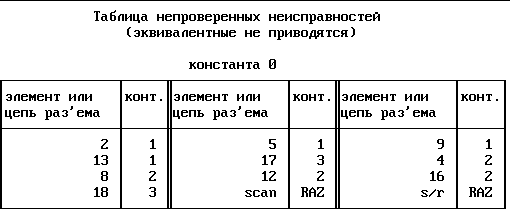

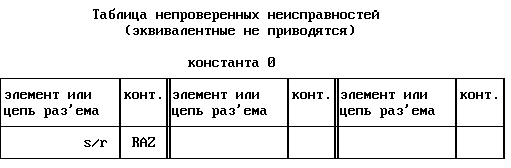

Данные неисправности нельзя проверить в системном рабочем режиме. Поэтому на второй итерации рассматривалась работа схемы в режиме генератора псевдослучайных чисел.

В1=В2=0

Scan=1

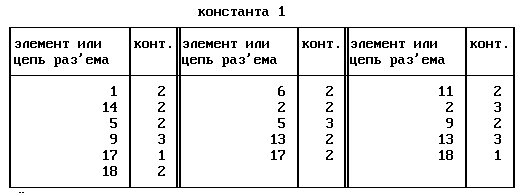

Неисправности типа константа 1:

Для проверки неисправности В1º1 необходимо подать на вход z1=1. При этом на выходе триггера всегда будет 1. Для проверки неисправности Р31º1 необходимо установить на инверсных выходах триггеров 3 и 4 различные значения (4 такт работы генератора псевдослучайных чисел). Неисправности Р11º1, Р14º1, Р15º1 и аналогичные им проверяется при работе генератора на 2-5 тактах работы. Неисправности Р29º1, Р24º1 и Р30º1 проверяются на 2-м такте работы.

Неисправности типа константа 0:

Для проверки неисправности Р30º0 и Р12º0 следует установить на инверсных выходах триггеров 3 и 4 различные значения (4 такт работы генератора псевдослучайных чисел).

Неисправность Р31º0 и scanº0 проверяются на 1 такте.

Таким образом, для проверки неисправностей, непроверенных на шаге 1, необходимо, чтобы генератор псевдослучайных чисел проработал 5 тактов. Временная диаграмма будет выглядеть следующим образом:

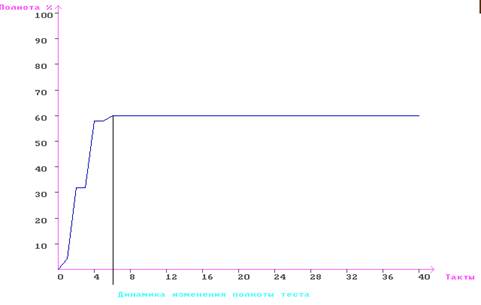

Рис.9

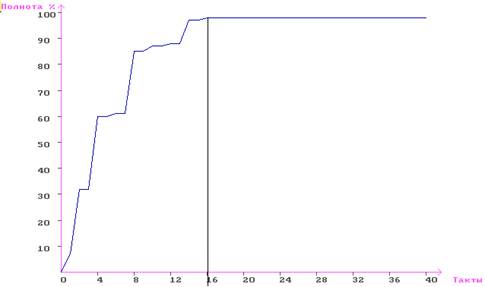

График изменения полноты теста

Рис.10

Неисправность s/rº0 проверить нельзя, т.к. схема работает только при данном значении. Таким образом, для данной схемы построен максимально полный тест. Полнота теста –

98 %.

ВЫВОД

В курсовой работе была проведена отладка схема встроенного блока логических наблюдений BILBO. Затем был разработан тест, обнаруживающий неисправности типа константа 0 и константа 1. Полнота теста составила 98%. Одна неисправность в схеме является не обнаруживаемой.